采用CH365通用PCI接口芯片实现接口电路的软硬件设计

接口/总线/驱动

描述

1、引 言

ISA(Industry Standard Architecture,工业标准结构)总线是上世纪八十年代中期出现的工业现场控制总线。ISA总线数据传输速率较低,又不能动态地分配系统资源,且对CPU占用率高,相应的插卡数量有限,并且如果几个设备同时调用共享的系统资源,很容易出现冲突现象。所以ISA总线被PCI总线为代表的新一代计算机总线替代成为必然。与ISA总线相比,32位的PCI总线速度更快(数据传输率为133 Mb/s)、实时性更好、可控性更佳,更易于实现高速实时的I/O口控制卡、通信接口卡、数据采集卡等。但PCI总线也因其32位地址与数据复用、控制总线及时序较复杂等原因导致以FPGA实现比较困难。本文所述通过CH365芯片可以快速实现PCI接口电路的设计,支持ISA总线接口向PCI总线接口的升级,并且由CH365芯片的本地硬件地址功能可以实现原系统软件无需修改就可使用,大大降低了板卡升级的时间周期和开发难度,具有较高的实用价值和推广价值。

2、PCI总线的特点

PCI是先进的高性能局部总线,可同时支持多组外围设备。其特点是:总线操作与处理器一存储器子系统操作并行;线性突发传输;极小的存取延误;不受处理器限制;基于PCI卡设备信息,全自动配置与资源分配,实现即插即用。

PCI的地址空间有3类:存储器、I/O和配置地址空间。存储器空间和I/O空间同以前的ISA总线规范相同,而配置空间是PCI所特有的。配置空间使系统处理器能够枚举PCI总线上的各种设备,并根据设备要求自动配置存储器和I/O的地址空间。操作系统在自检的过程中检测所有PCI设备,读取设备的配置信息,并给每一设备分配系统资源,如中断、I/O空间、存储器空间等。在PCI系统结构中,为每个PCI都提供了256个字节(至少是前64个字节)的配置空间,这256个字节的配置空间中前64个字节称为头区域,是每一个PCI设备都应该实现的,他的主要功能是识别PCI接口设备,以及PC访问板卡的方式等。其余的192个字节根据不同的PCI设备有所不同。

3、 PCI接口芯片的选择

PCI接口电路至少实现如下功能:

(1) 高速的地址产生单元;

(2) 地址译码及命令译码单元;

(3) 标准配置寄存器(64个字节)、PCI总线逻辑接口单元、用户设备逻辑接口、数据缓冲区等。

所以若用FPGA芯片直接设计PCI接口则难度大且开发周期长,而专用的PCI接口芯片可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的接口。

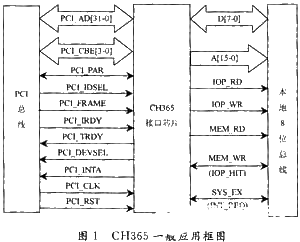

目前常用的PCI专用接口芯片有PLX公司PCI90XX系列,AMCC公司S59XX系列,南京沁恒公司的CH365通用PCI接口芯片。其中南京沁恒公司的CH365是国内自主开发的PCI总线接口芯片,CH365将32位高速PCI总线转换为简便易用的类似于ISA总线的8位主动并行接口,并提供独有的本地硬件地址请求功能,适合制作低成本的基于PCI总线的计算机板卡,以及将原先基于ISA总线的板卡升级到PCI总线上。另外CH365价格便宜、使用方法简单,非常适合用于短周期、低成本PCI接口卡的制作。其一般应用框图如图1所示。

CH365是一个连接PCI总线的通用接口芯片,可将32位高速PCI总线转换为主动8位并行接口并提供16位地址,可以进行I/O及存储器的读和写,可以设定PCI板卡的设备标识。

CH365非突发存取的实测速度可达7 MB/s,写脉冲的宽度从30~240 ns可选;自动分配I/O基址,I/O空间占用256个,其中偏移00~EFH共240 B的标准的本地I/O端口,而F0~FF为CH365内部使用的寄存器,对I/O端口操作只须I/O基址加上偏移量;通过该接口直接升级ISA的I/O板卡到PCI总线,完全不需要修改原ISA卡的相关软件;直接映射支持容量为32 kB的存储器SRAM或者扩展ROM(BootROM),偏移地址0000~7FFFH;提供两线串行主机接口,可以挂接类似24C0X的两线串口E2PROM器件;支持Windows 98/ME/2000/XP,通过DLL提供应用层API。

CH365的地址引脚A15~A0用于提供相对于基址的偏移地址,引脚D7~D0为双向数据引脚,与设备相连。IOP_RD用于提供I/O读选通信号,IOP_WR用于提供I/O写选通信号,MEM_RD用于提供存储器读选通信号,MEM_WR用于提供存储器写选通信号,上述引脚均为低电平有效。与PCI总线相连的引脚直接与PCI总线对应。

4、 PCI接口卡的设计和实现

4.1 原ISA接口卡简介

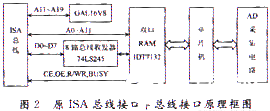

原ISA总线接口卡是一个多路数据采集板,接口卡所采集数据由板上单片机与ISA总线通过双口RAM进行数据交换。双口RAM的11位地址线与ISA总线的低口位地址线相连作为局部地址;ISA总线接口板的高位地址与GAL168V芯片相连,由预先设置在GAL168V芯片中的地址作为接口板基址;双口RAM的左数据线通过一个8路总线收发器隔离后与ISA总线数据线相连,右地址线、数据线与单片机相连。

原ISA总线接口卡总线接口原理框图如图2所示。

4.2 PCI接口卡的设计和实现

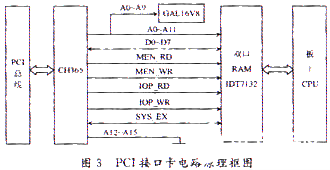

为了实现PCI总线接口需在原ISA接口板上加上CH365芯片及其周边电路。CH365芯片与PCI总线的连接符合PCI总线规范,而CH365芯片提供的本地总线接口端与ISA总线接口类似。为了减少总线接口改变带来的改动,本文利用CH365芯片的本地硬件地址功能设定接口卡的本地硬件地址。

4.2.1 本地硬件地址功能的实现

CH365提供一种可以由板卡制造商选定PCI设备I/O口地址的方法,即本地硬件定址,其原理是将PCI设备的部分I/O口地址译码,通过外围的二级译码电路来实现。外围的二级译码电路比较简单,与ISA总线的I/O译码电路类似,CH365将PCI总线I/O操作地址同步提供给外围电路,当外围电路对地址译码匹配后,向CH365请求本地硬件定址,再由CH365请求PCI总线在该特定I/O口地址范围内进行读写操作。

为启用CH365提供的本地硬件定址功能,需将CH365局部数据总线端中D4线弱下拉接地(即设定值=0),以设置CH365工作于本地硬件定址模式。外围二级译码电路可由GAL16V8实现。

4.2.2 双口RAM的读写

CH365的本地地址线和数据线端与双口RAM相连。双口RAM允许2个CPU同时读取任何存储单元(包括同时读同一地址单元),但不允许同时写或一读一写同一地址单元,否则就会出现写入值和读出值不是期望值的混乱状态。虽然双口RAM本身带有BUSY控制信号来协调两端的访问,但BUSY信号脚要求与两侧CPU的READY线相连,而CH365并不具有READY信号线,因此,需要引入仲裁逻辑控制模块。常用的双口RAM解决地址竞争的途径有:令牌传递法、基于邮箱机制的INT中断法以及插入等待周期的BUSY法等。在本系统中采用第二种方法。

基于邮箱机制的INT中断法的基本思想是:给每个端口分配一个地址作为邮箱,比如本系统可以令CH365使用00H,单片机使用8000H,这两个地址用来装载作为分配两端口RAM使用权的依据数据。具体约定为:当左端口CH365写地址单元00H时,通过逻辑器件可实现右中断DSP INT(DSP中断)为低,向DSP发出中断清求,DSP读地址单元00H时,DSP INT为高,复位CH365发出的中断请求。同理,当右端口写地址单元8000H时,左中断INT REQ(CH365中断)为低,可向左端口发出中断请求;而当左端口读地址8000H时,INT_REQ为高,复位DSP发出的中断请求。当信箱内容为00时,表示正在使用该方端口;当信箱内容为FFH时,表示结束使用该端口。因此,双方在对端口的其他单元进行读写操作开始时,需要向邮箱中写入00H,操作结束,写入FFH。如果没有发生争用,则直接进行读写操作,否则,慢的一方产生中断,并查询对方邮箱,直到对方邮箱内容为FFH。具体实现可借助CPLD来完成。

4.2.3 PCI接口卡设计中应注意的问题

PCI接口作为高频数字电路,电磁兼容设计尤为重要,在设计PCB板时需要参考PCI总线规范。CH365的PCI信号的走线长度应小于35 mm,尽量走弧线或者45°线,信号布线尽量在元件面,在PCB背面保留大面积接地覆铜。CH365芯片有3对电源引脚,在制作印制板时,应在每对电源附近放置高频消磁退耦电容。

4.2.4 PCI接口卡的硬件电路原理

PCI接口卡的硬件电路原理框图如图3所示。

5、 结 语

本文所述,通过增加一片CH365芯片,采用硬件地址方式所设计的PCI接口卡,可获得和原ISA卡完全相同的性能。而用户计算机控制程序不用作任何修改,仅仅在PCI板卡插入计算机过程中,添加CH365芯片的驱动程序而已,从而避开繁杂的PCI总线接口规范标准,大大简化了PCI接口卡设计的难度,同时也极大地降低了PCI卡开发和制造的成本,具有较好的市场前景。本文所升级的PCI接口卡已经实际使用,功能正常,取得了很好的效果。

责任编辑:gt

-

为什么要从“软硬件协同”走向“软硬件融合”?2022-12-07 3942

-

CH365基址不一样是为什么?2022-10-11 923

-

PCI总线接口芯片CH365技术手册2022-09-09 812

-

沁恒股份PCI总线接口芯片:CH365概述2019-11-04 3605

-

采用CH365芯片实现PCI总线接口卡设计2019-04-29 2546

-

请问各种PCI接口芯片的区别是什么?2019-01-23 4187

-

各种PCI接口芯片2013-12-05 3978

-

PCI 总线接口芯片CH3652013-03-12 6164

-

基于CH365的PCI总线运动控制卡的设计2013-01-10 2184

-

基于CH365的PCI适配卡的设计2011-08-04 893

-

PCI总线接口芯片CH3652010-11-08 6225

-

基于通用接口芯片CH365的财税安全卡设计2009-09-26 1472

-

基于PCI总线的数据采集接口设计2009-08-19 620

-

CH365,中文资料,pdf datasheet(PCI 总2009-07-23 1309

全部0条评论

快来发表一下你的评论吧 !