全加器的定义_全加器的输入端有几个

电子说

1.4w人已加入

描述

全加器的定义

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器逻辑图原理

两个多位二进制数相加时,除了最低位以外,其他每一位相加时都需要考虑低位的进位,即将加数、被加数和低位的进位3个数相加,这种加法运算称为全加运算,实现全加运算的电路叫做全加器。

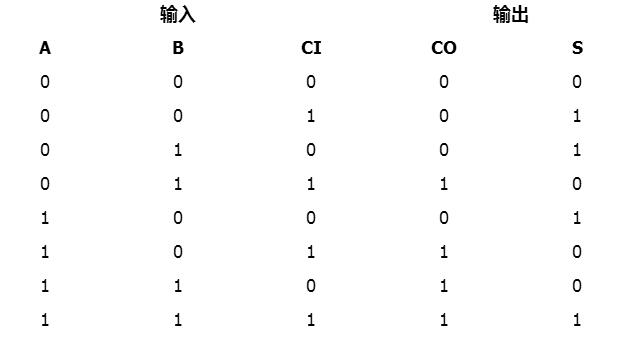

全加器的真值表如表1所示。A、B、CI分别为加数、被加数和低位的进位,S为本位和输出,CO为向相邻高位的进位输出。

表1 全加器真值表

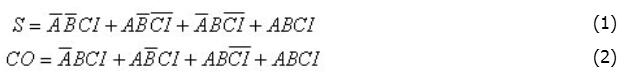

根据真值表写出输出逻辑函数式:

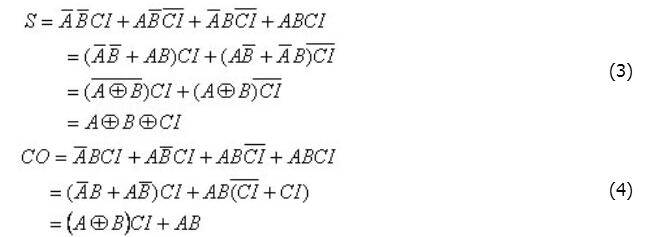

将函数式进行化简和转换

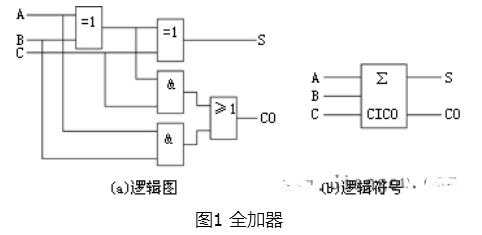

画出全加器的逻辑图,如图1所示。

全加器的输入端有几个

全加器的输入端有三个,分别为A、B、C(低位的进位);两个输出S(和);C(运算产生的进位)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 全加器

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 1626

-

如何对全加器进行实验2021-10-29 2396

-

怎样去设计一种基于FPGA的1位全加器2021-09-17 1771

-

FPGA入门——1位全加器设计 精选资料分享2021-07-26 1637

-

全加器的真值表2021-06-29 63537

-

全加器逻辑表达式_全加器的逻辑功能2020-04-23 135056

-

高性能CMOS全加器设计的详细资料说明2019-07-03 3070

-

请问Quartus2中的用一位全加器来实现四位全加器2019-03-06 6345

-

全加器是什么?全加器和半加器的区别?2018-07-25 77223

-

用74ls151实现全加器设计电路2018-05-07 130997

-

一位全加器代码VHDL2014-12-09 7383

-

全加器,全加器是什么意思2010-03-08 87510

-

全加器2009-04-07 10327

全部0条评论

快来发表一下你的评论吧 !