MAX3420E与SPI主控制器构成USB外设器件的中断系统分析

嵌入式技术

描述

MAX3420E可与任何SPI主控制器相连,以构成全速USB外设器件。尽管一般都由MAX3420来管理底层USB信令,但是需要处理USB事件时,SPI主控制器必须参与处理,当MAX3420的INT引脚指示有中断发生时,SPI主控制器将读取14个中断请求位,以确定需要服务的中断,一般情况下,主要由这些中断请求(IRQ)位确定MAX3420E的工作过程,在选择器件时,SPI主控制器可以是微控制器、DSP、ASIC或具备SPI端口的其他器件,并应能提供SCLK信号。

MAX3420E的中断逻辑

◇ IRQ位

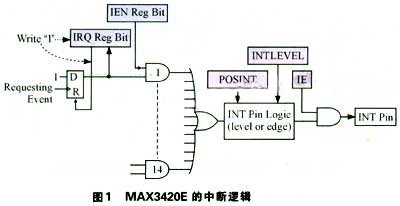

图1所示为MAX3420E中断逻辑。阴影部分是可通过SPI访问的寄存器位,图中有一个IRQ位,实际上,每一个中断都有一个用于锁存服务请求的触发器。触发器的输出即为IRQ,它出现在MAX3420E寄存器中,IRQ位提供两种功能:一是读取一个IRQ位,然后返回IRQ触发器的状态;二是写入一个“1”至IRQ位,以清除IRQ触发器,而写入“0”至IRQ位,则不改变触发器状态。

事实上,可以在任意时刻读取IRQ位,它反映了IRQ触发器的状态,当按照写入1而不是0来清除所选的IRQ位时,这一过程不需要读-修改-写周期,假设MAX3420E的IRQ位与普通的寄存器位一样,即写1置位,写0清除,那么,清除USBIRQ寄存器的USESIRQ位的操作代码如下:

#define rUSBIRQ 13 //register 13

#define bmURESIRQ 0x08 //URESIRQ is bit4,bm means“bit mask”

unsigned char dum;

dum=rreg(rUSBIRQ); //read the register

dum=dum&—bmURESIRQ; //chear one bit

wreg(Rusbirq,dum); //write it back

由于SPI主控制器可通过写1来清除一个MAX3420E IRQ位,而写0则不改变其他寄存器位,因此,SPI主控制器可直接写入位屏蔽值以清除URESIRQ位。这样,上述代码中的最后三条语句便可由下面的单条语句所替代:

wreg(rUSBIRQ,bmURESIRQ);//1 cheras an IRQ bit,0 leaves it alone

◇ IEN位

14个MAX3420E中断的每一个都有相应的中断使能(IEN)位,IEN位和IRQ触发器输出进行“与”操作,可决定是否向INT引脚传送中断请求。14个IRQ触发器通过门控电路后再进行“或”操作,也会形成一个内部中断请求信号,并传送至中断引脚逻辑模块。

实际上,无论IEN位的状态如何,IRQ位都指示中断悬挂状态,这样,即使中断不触发INT引脚,固件仍可以检查该悬挂中断,如果您的程序需要检查一个IRQ寄存器“是否悬挂中断”,比较简单的方法是读取IRQ和IEN寄存器,并对它们进行“与”操作,然后检查“等待和被使能的IRQ”位,零值表示没有使能的中断,系统处于悬挂状态。

◇ IE位

SIP主控制器通过IE位来使能或者禁止INT引脚,由于该位影响到所有的中断,因此通常称之为全局中断使能,不论IRQ或者IEN位的状态如何,当IE为0时,INT引脚均无效。

可用两个寄存器位INTLEVEL(参考下面的讨论)和POSINT来控制INT引脚的工作方式,在设置IE为1之间,应先设置这两个配置位。其操作如下:

(1)电平模式

某些微控制器系统使用低电平有效中断。当采用这种配置时,MAX3420E采用一个开漏极晶体管驱动INT引脚至地,由于引脚只能驱动低电平,因此,需要在INT引脚和逻辑电源之间接一个上拉电阻,该模块支持多个芯片的INT引脚输出(每个均为开漏输出)连接在一起,并使用单个上拉电阻。由于任何一个芯片输出都可将引脚拉低,因此这种逻辑有时也称为“线或”。对于这种类型的系统,可设置INTLEVEL为1。

(2)边沿模式

MAX3420E的INT引脚可以驱动边沿有效的中断系统,此时,微控制器在其中中断输入脚上将检查0到1或者1到0跳变,INTLEVEL为0是MAX3420E的缺省模式。SPI主控制器通过第二个POSINT位设置边沿极性,POSINT为1时,MAX3420E为悬挂中断输出一个0到1的跳变。POSINT为0(缺省值)时,MAX3420为悬挂中断输出一个1到0的跳变。

需要说明的是:如果一个IRQ位置位,而其对应的IEN位清零,则IRQ将不会影响INT输出引脚,但是,中断仍处于悬挂状态,永远可以读取IRQ位以获得其状态,可向对应的寄存器位写1,并将IRQ位清零。

悬挂中断(IRQ位是1)的IEN位出现0到1跳变时将产生中断。

INT引脚可连接至微控制器的中断系统,此外,微控制器可以轮询INT引脚,以确定MAX3420E是否有中断处于悬挂状态,最适合轮询的模式是电平模式(INTLEVEL=1),这是因为在边沿模式中,INT引脚输出的脉冲可能太窄,微控制器无法探测到(参考下面的讨论)。请注意,电平模式需要在INT引脚和V1之间连接一个上拉电阻。

INT引脚状态与波形

◇ 电平模式

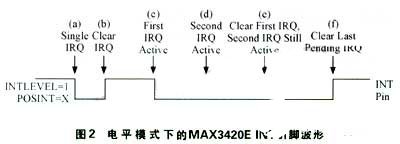

图2所示为电平模式下的MAX3420E的INT引脚波形。INT引脚静态为高电平(上拉至VL)。假设图中两个中断的IEN位均置为1,全局IE位也置1,那么将发生一个中断请求,使MAX3420E INT引脚置低,实际上,尽管MAX3420E中断输出引脚被称为INT引脚,它有时也是负极性(例如在电平模式下)。

SPI主控制器完成中断服务后将向IRQ位写入1,并将其清零,并使INT引脚返回至静态高电平。(a)和(b)之间的间隔是中断置位其IRQ位和SPI主控制器清除IRQ位之间的时间,当系统产生另一个中断请求,会将INT引脚拉低,而当第一个中断请求处于悬挂状态时,系统可能产生第二个中断请求,而此时INT电平没有变化,因此至少有一个中断处于悬挂状态(实际上,此刻有两个中断处于悬挂状态。)

当SPI主控制器完成一个中断服务向IRQ位写入1并将其清零后,由于仍有一个中断处于悬挂状态,INT引脚将保持低电平,此后SIP主控制器处理完剩下的中断请求,并向IRQ位写入1,在将其清零,此后由于没有中断处于悬挂状态,因此,INT引脚将返回至静态高电平。

这种逻辑可以很好地处理INT引脚轮询,如果MAX3420E的任何部分需要服务,并且其中断已被使能,那么INT引脚将变为低电平,在微控制器清除最后一个悬挂IRQ位之前,INT引脚一直保持低电平。

◇ 边沿模式

图3所示为两种极性边沿模式下MAX3420E的INT引脚波形,极性由POSINT位控制。该波形与电平模式相似,但有两处不同,在两种条件下,INT引脚将产生边沿跳变:第一是一个IRQ位变为有效状态(其IRQ触发器产生0到1跳变),此时处理器将清除一个IRQ位(向其写入1),其他IRQ处于悬挂状态,第二个条件是在确保还有中断需要服务时,处理器能够检测到边沿跳变。

除了产生边沿跳变外,与电平模式一样,INT引脚也具有有效和无效状态,INT引脚的无效状态取决于POSINT位设置的边沿极性,在这一点上,边沿模式与电平模式相似,察看INT引脚的状态就可以知道是否有中断处于悬挂状态,当在负极性边沿模式下如果没有悬挂中断,INT引脚为高电平,如果有悬挂中断,则为低电平,而在正极性边沿模式下,如果没有悬挂中断,INT引脚为低电平,如果有悬挂中断,则为高电平。

INT引脚的有效状态意味着至少有一个中断处于悬挂状态,无效状态是指没有中断处于悬挂状态,假设中断已被使能,那么,系统将出现以下事件;

(1)产生一个中断请求时,MAX3420E INT引脚出现一个边沿跳变,边沿的极性取决于POSINT位的设置,由于中断仍处于悬挂状态,INT引脚保持其有效状态。

(2)SPI主控制器完成中断服务后,并向IRQ位写入1,并将其清零。MAX3420E INT引脚返回至无效状态,图中(a)和(b)之间的间隔(1)是产生中断和SPI主控制器清除IRQ位之间的时间。

(3)产生另一个中断请求时,MAX3420E INT引脚产生一个边沿跳变,并保持其有效状态。

(4)当第一个中断请求处于悬挂状态时,系统又将产生第二个中断请求,由于MAX3420E INT引脚必须产生另一个边沿跳变。因此,该引脚将在无效和有效状态之间产生跳变脉冲,从而提供正确的边沿极性,在MAX3420E中,该脉冲的宽度固定为10.67μs,由于还有中断处于悬挂状态,INT引脚可保持在有效状态。

(5)SPI主控制器完成一个悬挂中断服务后,向其IRQ位写入1,将其清除。与第(d)步一样,INT引脚产生另一个边沿跳变。

(6)SPI主控制器处理完剩下的中断请求,并向其IRQ位写入1,将其清除。由于此时已没有中断处于悬挂状态,因此,INT引脚返回至无效状态。

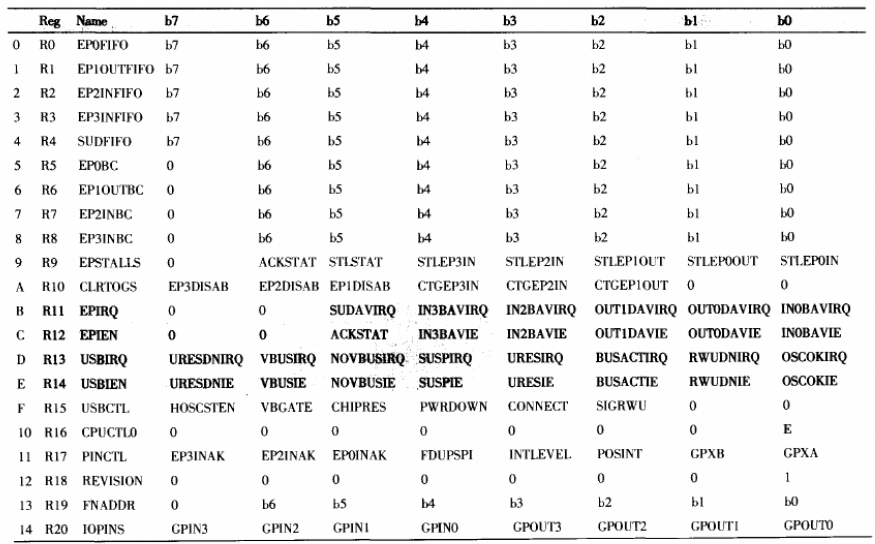

中断寄存器

表1是MAX3420E寄存器控制位,其中阴影部分可用于控制USB中断系统。MAX3420E具有两类USB中断,可由表1中阴影部分的寄存器控制,中断位分为两类:一是位于EPIRQ(R11)和EPIEN(R12)寄存器的端点控制,二是位于USBIRQ(R13)和USBIEN(R14)寄存器的USB控制,全局IE位在CPUCTL寄存器中。

中断请求位BAV

该器件的三个缓冲区就绪(BAV)IRQ位可用于指示是否可以将SPI主控制器装入一个IN端点FIFO,芯片复位或者IN数据由端点缓冲区成功地发送给主机后,MAX3420将置位这些IRQ位,此后该IRQ将通知SPI主控制器缓冲区可以装入新数据。

与所有的MAX3420E IRQ位一样,也可以通过写入1来三个清除BAV IRQ位,但是千万不要这样做,相反,应通过写入IN端点的字节计数寄存器来清除BAV IRQ位,这是因为MAX3420E要使用一个IN端点的BAV中断请求位作为锁定机制。

事实上,上述机制可以确保SPI主控制器和MAX3420E的串行接口引擎(SIE)不会同时使用端点缓冲区。例如,如果清除BAV位,然后以两条单独指令装入字节计数器。那么当您更新字节计数寄存器时,可能已经开始了数据包传输,从而导致数据出错。

责任编辑:gt

-

MAX3420E USB外设控制器,SPI接口技术手册2025-05-23 1238

-

将USB添加到任何内容2023-03-02 1215

-

MAX3420E外设控制器的中断系统,看完你就明白了2021-04-19 1101

-

基于SPI芯片MAX3420的USB控制器接口设计2018-11-20 1747

-

MAX3420E系统调试步骤2018-08-24 2021

-

MAX3420E USB外设控制器,SPI接口2011-01-19 1336

-

MAX3420E信息卡2009-04-29 669

-

为任何系统增加USB2009-04-25 1113

-

MAX3420E的USB杖举程序(及其他)2009-04-23 672

全部0条评论

快来发表一下你的评论吧 !