从模拟设计和保护控制集成电路的角度来研究可靠性

描述

模拟触及一切。如果没有供应商在过去几十年中开发的大量模拟和混合信号组件,让许多行业实现飞跃的数字“革命”是不可能的。

没有对可靠性的同等投入,这些进步也不可能发生,可靠性被定义为系统或系统元件在规定的条件下在指定的时间内无故障地执行其预期功能的概率。

半导体行业别无选择,只能提高其设计和制造产品的可靠性,尤其是在安全关键市场。举个例子,考虑到一些汽车制造商现在要求芯片能够使用18年,而汽车和卡车的零缺陷代表了一些最苛刻的应用条件。在一些工业应用中,更换传感器很困难,必须取消局部维修,芯片需要使用20年或更长时间。

可靠性设计

可靠性问题的主要原因包括设计的复杂性、容易出错的过程以及评估健壮性的有限验证。所涉及的机制可以是物理的、化学的、电的、热的或其他导致失败的过程。

一个罪魁祸首是先进的CMOS技术——在更小、更快、功耗更低的芯片中增加功能。虽然缩放有助于高集成度混合信号系统的设计,但它也带来了可靠性挑战:缩放不适用于模拟电路,而不适用于数字集成电路。一般来说,极端先进的节点不会对设计模拟部分的晶体管产生重大影响。

在本文中,我们将从模拟设计和保护控制集成电路的角度来研究可靠性。模拟需要一种不同的方法,这种方法必须由设计者在没有设计工具的大力协助下解决。模拟设计相对缺乏自动化,这给单个设计师和设计团队带来了实现质量和性能的更多负担。

可靠性必须融入整个开发周期,这已成为公认的惯例。这就是所谓的可靠性设计(DFR),通常从概念阶段的早期一直使用到产品报废,以确保在产品的整个生命周期内完全满足客户的期望。DFR可以在产品发布前设计出或减轻潜在的故障模式,基于发现问题的测试和可靠性预测的统计分析方法。

这一阶段的可靠性工程旨在通过冗余、内置测试和高级诊断等措施来提高系统的健壮性。离散模拟元件参数往往会随时间漂移;环境影响——腐蚀、振动和温度——也是有问题的。可靠性测试可以在整个产品或系统生命周期的组件、子系统和系统级别进行。

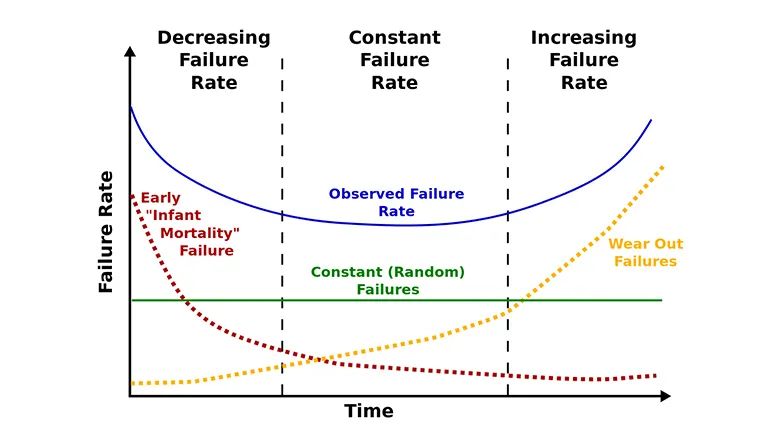

图1:“浴缸曲线”(蓝色,上面的实线)是早期失效概率降低(红色虚线)和磨损失效概率增加(黄色虚线)加上随机失效常数(绿色,下面的实线)的组合。(来源:维基百科,公共领域)

系统保护

由于设备故障或外部干扰,电网内部会发生故障。但是通过在您的系统中实施适当的电路保护,可以通过例如在网络中打开电路来隔离电气故障来防止灾难。这些保护系统检测由于电气故障引起的电压和电流。

模拟输出电路保护涵盖各种情况。了解环境和应用有助于工程师决定应该做什么以及做多少来保护模拟输出。

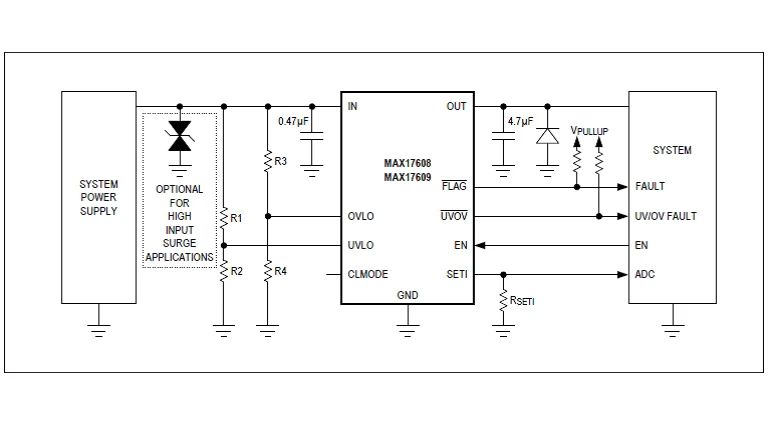

为了防止常见电路故障(如正向/反向电压/电流保护),可调节过压和过流保护器件等器件非常适合保护系统免受正负输入电压故障的影响。可调输入过压保护范围为5.5V至60V,可调输入欠压保护范围为4.5V至59V。输入过压闭锁(OVLO)和欠压闭锁(UVLO)阈值使用外部电阻设置。

这些器件具有高达1A的可编程限流保护,因此在启动时控制浪涌电流,同时在输出端对高电容充电。

MAX17608和MAX17610阻止电流从外向内流动,而MAX17609允许电流反向流动。这些器件具有热关断保护功能,可防止功耗过大。它们采用12针(3毫米x 3毫米)小型TDFN-爱普封装。

可靠性监控

为确保故障率保持在最低水平,应在加速条件下监控代表从关键晶圆制造厂和组装过程装运的器件的可靠性。样本大小可能有所不同,但通常每个家庭有数百个(或更多)设备,分布在不同的环境压力下。结果可以在定期发布的报告中更新。

用于保护和互连集成电路的封装也必须是可靠性保证链的一部分。封装通常由导电合金引线框架制成,该引线框架保持集成电路管芯(或多个管芯),并提供将其连接到引线框架的某种机制(例如倒装芯片、直接管芯附着或金属线)。引线框架组件用各种材料封装,例如环氧树脂或陶瓷,以保护集成电路引线框架组件并提供机械稳定性。

图2:max 17608/09典型工作电路。(来源:马克西姆)

包装完整性测试根据当前合格的规格验证产品的进货质量。例如,超声波测试是一种灵敏的非破坏性技术,可以描绘出封装空隙和内部界面分离和裂纹。JEDEC J-STD-020等标准可用于识别非密封固态表面贴装器件(SMDs)的水分敏感性等级。该程序可以防止焊接操作过程中由于湿气引起的应力而造成的潜在损坏。

其他预处理应力用于模拟高温和最大工作电压下的典型器件性能。应分析所有故障的原因。该分析的结果可用于建立纠正措施,以消除发现的故障机制。

在不同的读取点对器件进行电气测试,以便在加速条件下确定器件在初始和长期使用期间的性能。应要求器件在整个电压和温度范围内满足所有数据手册规格。

-

#硬声创作季 #集成电路 集成电路版图设计-9.12项目设计实例及技巧-芯片的可靠性1-闩锁效应水管工 2022-10-17

-

集成电路在高可靠性电源的应用2019-06-11 0

-

基于集成电路的高可靠性电源设计2019-07-25 0

-

单片机应用系统的可靠性与可靠性设计2021-01-11 0

-

影响硬件可靠性的因素2021-01-25 0

-

GaN功率集成电路的可靠性系统方法2023-06-19 0

-

GaNPower集成电路的可靠性测试及鉴定2023-06-19 0

-

半导体集成电路的可靠性设计2009-10-19 530

-

超深亚微米集成电路可靠性技术2010-04-27 607

-

集成电路可靠性检查的最佳实践方案2018-02-02 2357

-

集成电路为高可靠性电源提供增强的保护和改进的安全功能2021-03-21 667

-

集成电路封装测试与可靠性2021-04-09 2038

-

集成电路的可靠性判断2023-06-14 1742

-

集成电路封装可靠性设计2023-06-15 1090

-

集成电路封装可算性模拟分析2023-06-27 526

全部0条评论

快来发表一下你的评论吧 !