高频下射频大功率器件的TRL校准

描述

以LDMOS(横向扩散金属氧化物半导体)为代表的射频大功率器件已经在民用通信市场以其优异的性能和低廉的价格而得到越来越广泛的应用,对于这种射频大功率器件的器件水平和能力评估也越来越受到关注。本文基于负载牵引系统,采用简单、便捷以及可重复使用的理念,使用常规的微带线阶梯型阻抗变换器电路为基础,充分考虑在应用测试中的偏置电路,进行前期使用ADS(Advanced Design System)仿真加后期验证,设计制造了低耗无串扰的TRL(Though Reflected Delay)校准件,为测试得到射频大功率器件的射频性能奠定了优异的基础。

随着通信的日益发展以及半导体功率器件研究和生产技术的突飞猛进,上世纪90年代末以前主要以硅双极型晶体管和砷化镓场效应管为核心的射频微波功率放大器正被增益、线性度和输出功率等方面更加优秀的产品所取代(硅基射频LDMOS以及氮化镓场效应管)。这同时也对这些新技术、新产品的性能评估提出了更高的要求。目前国内以945-960 MHz频段的RF LDMOS功率管产品(单裸管芯输出功率达到180瓦,线性增益达到19dB,效率达到70%,电压驻波比达到10:1)已经达到了实业化的目标。较之于传统上常用的SOLT校准(适用于同轴校准),TRL校准对于在非同轴环境下进行射频大功率器件的测试来说是一种非常精确的校准方式。这种校准方法的优点在于其校准准确度只依赖于传输线的特征阻抗而不是其他标准,反射标准的反射系数和传输系数的长度都可以在校准中由计算得出,很好地避免了一些测试板引入的误差,更能准确地反映被测器件的性能。

1

TRL校准件的要求

基于目前通用的射频测试板材,我们选用4350B型板材,这种板材制造标称的介电常数εr = 3.48,损耗因子为0.0037,板材厚度选取30mil,走线铜厚选取17μm。此次需要完成的目标频段是2.0GHz~2.5GHz,制作出来的Reflect、Though以及Delay校准件均能满足在此频段内反射系数Г(S11)<-10dB,传输系数T(S22)<-0.9dB。器件根部原始设计阻抗根据经验设定为2.5Ω,测试电路输入输出端口设计阻抗为通信系统设备通用的50Ω,端口采用常用的SMA型端子作为射频信号输入输出的物理接口。

1

TRL校准件的构建

因为最终目的是为基于Load-Pull系统的器件做阻抗提取和性能评估,对于校准件的版图设计基本需考虑通用性和成本,即在射频信号主路采用微带线阶梯型阻抗变换器的基础上,还需要在设计过程中考虑器件应用时所需要的直流偏置电路。

Part 1 射频信号主路设计

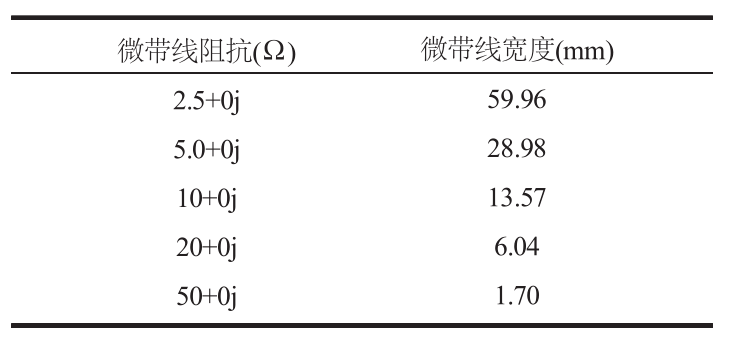

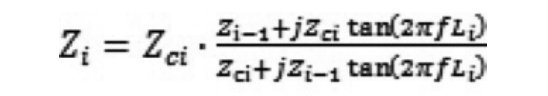

1、射频信号主路设计由于从器件根部的2.5Ω变换到测试电路输入输出端口的50Ω,而且需要实现2.0GHz~2.5GHz的频段跨越,为了确保在宽频带上能获得良好的匹配性能,因此设计阶梯为4级,对应设计的中间变换阻抗为:5Ω、10Ω、20Ω。可以采用下面的阻抗计算公式计算:

其中,W为线宽,T为铜线厚度,εr为板材的介电常数。

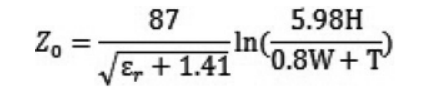

在此我们运用Linecalc这个小软件来计算和确定微带线宽度,如图1所示。

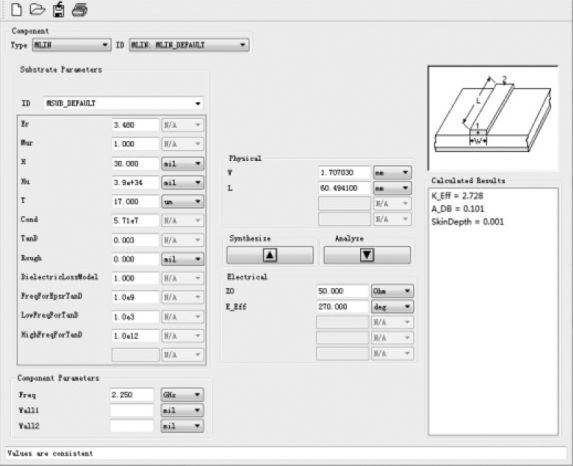

通过软件计算得出微带线宽度与设定阻抗的关系如表1:

图1:ADS微带线计算工具

表1:ADS微带线计算结果

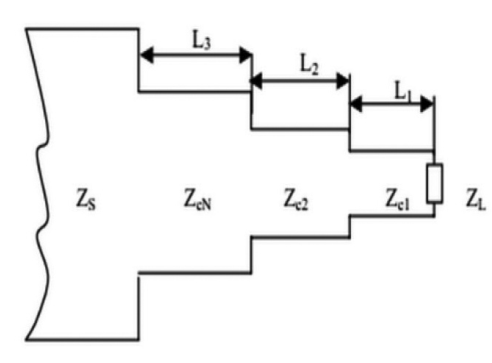

2、射频信号主路设计的微带线长度的设计思路为使用不定长度传输微带线多阶梯阻抗变换器(图2)。根据传输线理论:第i节的输入阻抗公式为:

这样就可以使用递推法计算出每一节微带线的长度。在此由于考虑整个校准件是一个整体,以及还存在去除偏置电路的影响以及整个校准件不宜做得太大的问题,因此对于每一节微带线的长度,我们将使用ADS的S-parameter调谐仿真,以及Layout之后的Momentum仿真,从整体上对微带线的长度和宽度进行调节,以达到能实现设计目标的要求。

图2:阶梯阻抗变换器

Part 2 直流偏置电路

直流偏置电路为射频功率放大器主路的元器件提供一个工作状态,其设计的好坏将影响放大器的性能,尤其是漏极偏置电路的设计。一般直流偏置电路设计需要遵循的三个原则:

(1)偏置电路对信号主路影响要尽量的小,即不引入较明显的附加耗损、反射以及高频信号沿偏压电路的泄露。

(2)为了偏置电路存在的大电流,需要考虑合理的偏置线宽度。

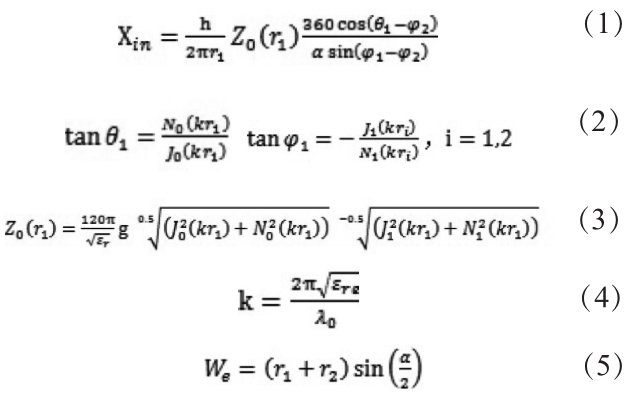

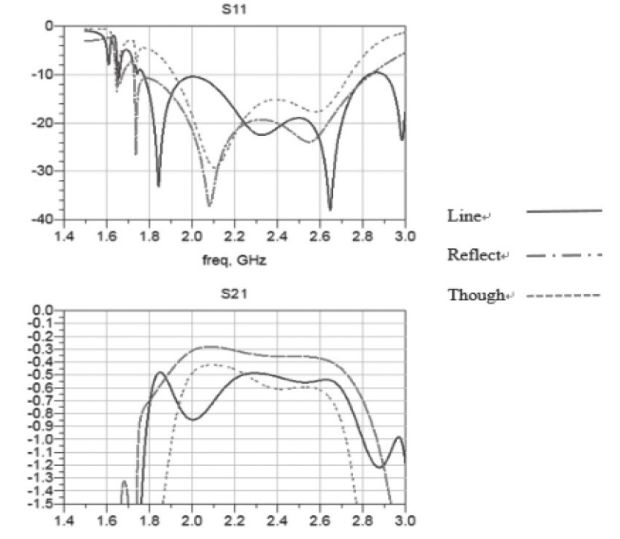

(3)尽量结构紧凑,简单。 基于直流偏置电路的三个原则,我们选择四分之一扇形开路线(即四分之一波长开路短截线的变形),这样能够很好满足三原则的要求。扇形微带短截线电抗可以由下列关系式出[5]:

在公式(3) 中,Ji(x)和Ni(x)是第一类和第二类贝塞尔函数,α扇形微带短截线的角度,εre是等效介质常数,λ0为自由空间波长,r1和r2是扇形微带线的内、外半径,hW分别是介质基片的厚度和微带宽度,We是扇形短截线等效为微带线的宽度。

根据设计的三原则,偏置线宽度的设计,尤其是器件漏端的偏置线线宽的设计,需要我们考虑电流承载能力,同时也需要考虑的是直流偏置铜线必须为尽量细的高阻线,因为这样能减少偏置电路对于主路的影响。那么根据表2中铜箔宽度与承载电流的关系,我们就可以进行选择。在此设计中我们考虑电流承受能力在1.2A左右,所以使用0.762的线宽也将电流承载能力的余量考虑在我们的设计中。

表2:铜箔宽度与承载电流的关系

1

TRL校准件的仿真与验证

Part 1 校准件的仿真

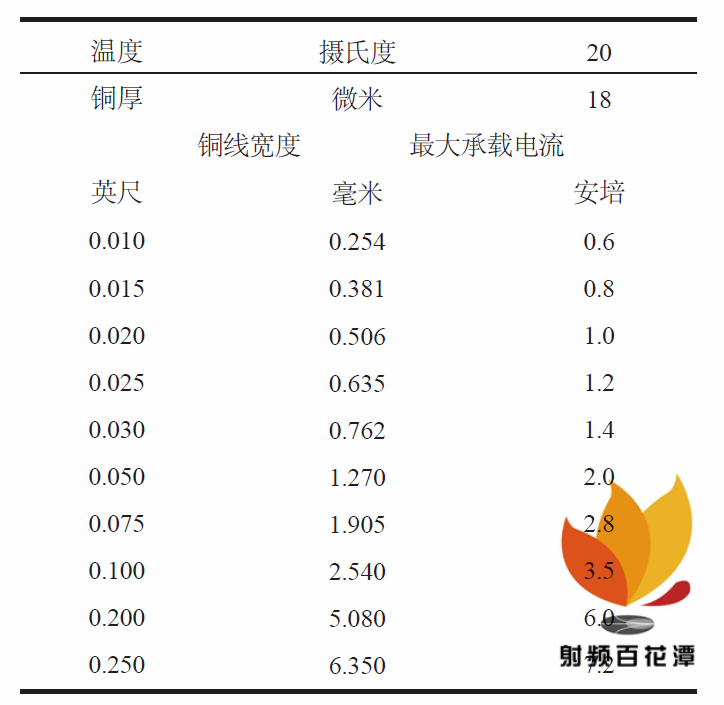

通过上述对于整个TRL校准件的设计考虑,使用ADS工具,我们得到了本次根据仿真电路得出的可用于实际制作的PCB版图,以及使用ADS的Momentum仿真出来的结果。

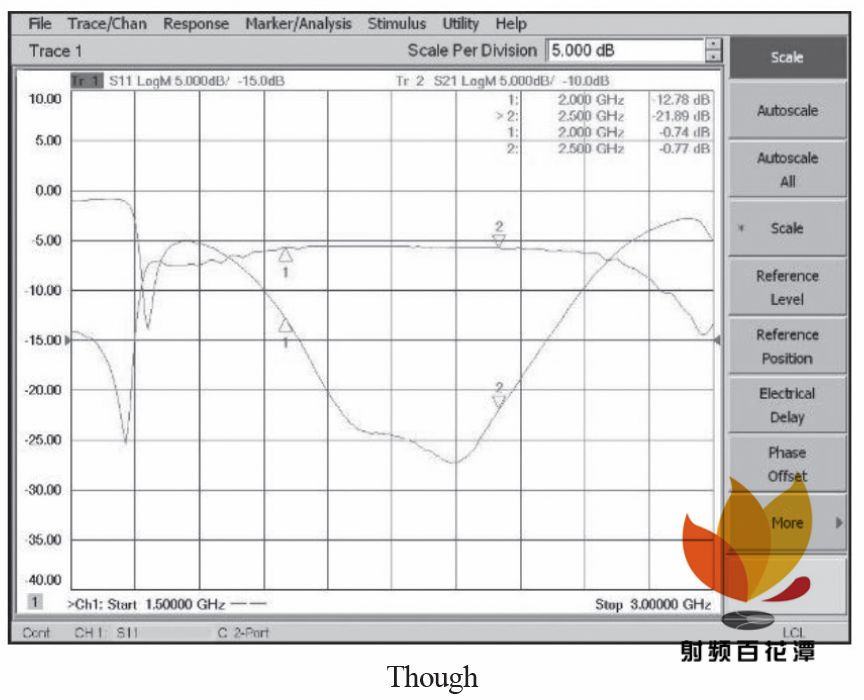

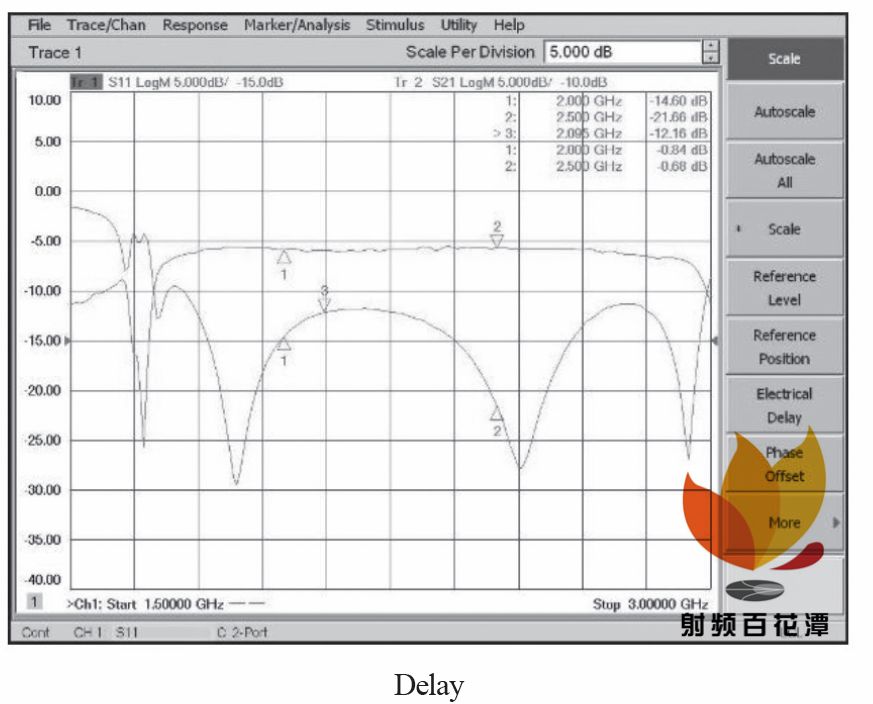

图3中的S11和S21各有三条线段,分别代入Though、Reflect、Delay三块校准件的反射系数和传输系数。考察2.0GHz、2.25GHz和2.5GHz三个典型频点的值,在S11的曲线图上,除Delay在2.0GHz点上只达到了-11dB,其余均低于-15dB;同样在S21的曲线图上,除Delay在2.0GHz点上接近于-0.9dB,其余均高于-0.7dB。应该说2.0GHz~2.5GHz这个频段内很好的达到了设计目标。

图3:TRL校准件Momentum仿真图

ADS这个软件在仿真、优化过程中有着优异的性能,对于比较高要求和挑战的性能指标能够做好预先仿真,并实现PCB版图电路,减少了工程反复和硬件材料的浪费,降低了设计成本,是一个很好的射频工程应用工具。

Part 2 校准件的验证

校准件的验证分两步进行,第一步是对校准件直接进行小信号测试验证,第二步是使用频率在 2.0GHz~2.5GHz之间的器件,在配合Load-Pull系统找到器件封装根部阻抗后,再通过普通射频电路测试板的匹配来验证校准件是否符合设计要求。1、校准件小信号参数的验证在完成TRL校准件的加工之后,我们将TRL校准件中的Though校准件和Delay校准件在Agilent的N5241A网络分析仪上进行小信号参数的测试,采用其结果与仿真结果进行对比。图4中上面的图为“Though校准件”的S11和S21的频率扫描图,下面的图为“Delay校准件”的S11和S21的频率扫描图。从结果来看,“Though校准件”和“Delay校准件”的S11最大值均低于-12dB,S21的最大值均高-0.84dB。其测量结果与仿真结果基本一致,从测试值来讲还略优于仿真的结果。

图4:TRL校准件S参数实测

2、器件的校验

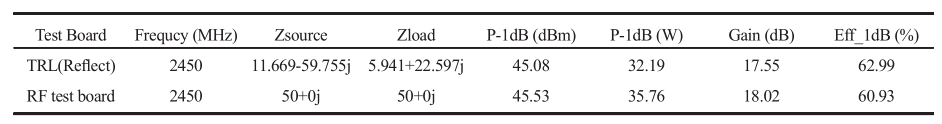

在此我们选取了一颗工作频率在2.45GHz,功率30W的RF-LDMOS,并已在封装内完成输入两级匹配的器件来进行验证。通过与Focus的Load-pull的校准和测量,我们得到的封装器件的根部阻抗为:

输入端:11.669 - 59.755j;

输出端:5.941 + 22.597j

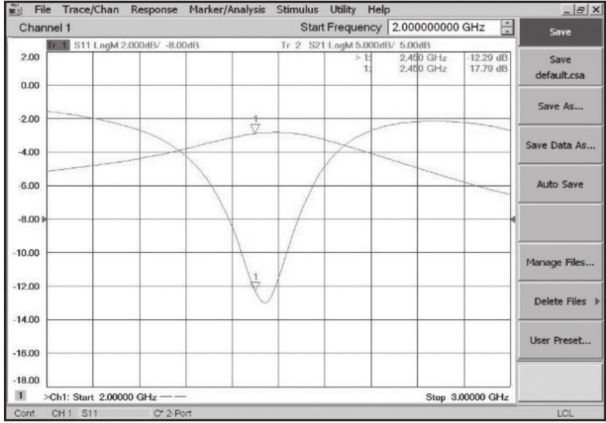

使用测量得到的器件根部的阻抗值,我们对符合器件的射频电路测试板进行了匹配,见图5。测试板的小信号测试曲线见图6。对比使用TRL校准件得到的器件性能与射频外围电路测试板得到的器件性能,可以得出表3。

表3的数据显示了使用TRL校准件测得的是器件根部阻抗以及在此阻抗下得到的器件性能。与根据根部阻抗进行的射频电路测试板匹配后的器件性能比较,其增益、功率和效率基本一致。

图5:24030器件射频测试电路

图6:TRL校准件小信号测试曲线

表3:TRL校准件得到的24030器件根部阻抗以及性能测试对比

1

结语

上文关于TRL校准件的设计和制作很好地完成了既定的目标,实现了高频下射频大功率器件的TRL校准,同时我们也看到,TRL校准件的设计涉及的很多方面和细节需要很好的梳理和把握。当然,一个好的TRL校准件的设计和制作还需要考虑更多的封装的兼容以及更宽频率的覆盖,这个也是我们将要努力的方向。

-

无源器件在大功率条件下S参数的变化量2023-08-21 3274

-

怎样设计和验证TRL校准件以及TRL校准的具体过程2023-05-25 7329

-

大功率晶体管是什么器件_大功率晶体管优缺点2023-03-01 2417

-

大功率高频开关电源的设计与实现2021-09-29 2351

-

TRL微波器件测量的校准方法2019-07-18 3768

-

关于集总参数衰减器的大功率特性讨论2019-06-24 2215

-

基于PIN Diode射频开关的大功率无线设备调试2019-05-26 5165

-

请问大功率的电子元器件有哪些2019-02-15 4400

-

大功率的电子元器件有哪些2015-06-03 2753

-

高频中、大功率晶体管2013-08-17 3347

-

TRL校准提取管芯S参数的技术2012-04-27 2724

-

大功率高频变压器2011-07-09 3047

-

高频大功率电子捕鱼器电路2011-06-29 9142

-

激光调制的可控大功率微波射频源2009-10-23 607

全部0条评论

快来发表一下你的评论吧 !