基于FPGA技术实现ADN2850的串口控制设计

可编程逻辑

描述

引 言

数字电位器是利用微电子技术制成的集成电路,它是依靠电阻阵列和多路模拟开关的组合完成阻值的变化。它没有可动的滑臂,而通过按钮输入信号,或是通过数字输入信号改变数字电位器的阻值。数字电位器由于可调精度高,更稳定,定位更准确,操作更方便,数据可长期保存和随时刷新等优点,在某些场合具有模拟电位器不可比拟的优势。

1、ADN2850的基本结构和工作原理

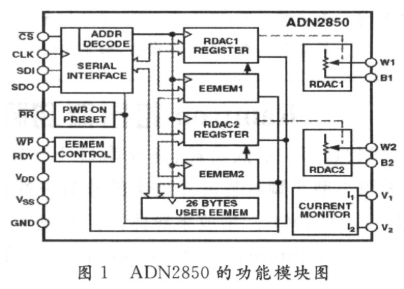

ADN2850是ADI公司的双通道,1 024阶非易失性数字电位器。温度系数仅为35 ppm/℃。其功能模块图如图1所示。它的输出电阻W和B之间的阻值主要由中间寄存器RDAC中存储的值决定。RDAC的值可以由外部指令直接赋予或者从内部非易失性存储器E2MEM中载入。E2MEM中的值可以被修改或者被保护。当RDAC中的值被改变后,新的值也可以被存入E2MEM中。之后,新的值将在系统重新上电后自动加载到RDAC中。

账 ADN2850的指令系统包含16种模式,通过一个标准SPI串行接口传送24位命令字决定,高位在先。24位命令字的前4位是命令,接下来4位是地址,后面16位是数据。这些指令可以用于RDAC的值的写入,E2MEM值的改写与复原,电阻值的回读等。

2、SPI接口简介

SPI是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用4根线,节约了芯片的管脚,同时为PCB的布局上节省空间。正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI的通信以主从方式工作,这种模式通常有1个主设备和1个或多个从设备,一般需要4根线,事实上3根也可以(单向传输时)。其也是所有基于SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCLK(时钟),CS(片选)。由SCLK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成1位数据传输,输入也使用同样原理。这样,在至少8次时钟信号的改变(上沿和下沿为1次),就可以完成8位数据的传输。ADN2850的SPI接口的4根引脚线分别是SDI,SDO,CLK,CS。

这里利用FPGA对SPI接口进行配置。为了方便对输入SPI的指令的随时改变,而不需要程序的重复写入,24位指令通过串口输入到FPGA。串口通信由微机上的串口调试助手协助进行。由于少了重新写入程序的时间,从而调试速度和效率明显增高。

3、串口简介

串口是计算机上一种通用的设备通信的协议,可以用于获取远程采集设备的数据。

串口按位(b)发送和接收字节。通信使用3根线完成:地线、发送、接收功能。由于串口通信是异步的,端口能够在一根线上发送数据同时在另一根线上接收数据。其他线用于握手,但不是必须的。串口通信最重要的参数是波特率、数据位、停止位和奇偶校验位。波特率是衡量通信速度的参数,它表示每秒钟传送的bit的个数。数据位则是衡量通信中实际数据位的参数。停止位一般是为了平衡两个系统的时钟而在实际数据位结束后传送的。奇偶校验位是串口通信中检错的一种方式,没有校验位也可以。整个系统的连接框图如图2所示。

4、ADN2850的串口控制

用串口控制ADN2850的流程图如图3所示。一旦有指令从串口发送,就重新经FPGA后写入ADN2850。

Verilog HDL程序分为3个模块,分别为复位rstgen模块,串口接收datagen模块和SPI接口操作spi模块。24位指令由微机输入,经串口接收模块后输出1个24位数据和1个标志位,用于SPI接口模块把数据传入ADN2850中。

账 datagen模块关键程序如下所示(相关变量声明省略):

该程序已经通过前仿真,并在Altera公司的EP2C70 FPGA上通过了验证,达到了预期的效果。

5、结 语

通过串口的应用,ADN2850的控制过程变的很方便。而串口本身连线简单占用资源少,应用也比较广泛,所以数字电位器ADN2850的串口控制不失为一种可行的方法。

责任编辑:gt

-

基于Nios驱动的ADN2850的BeMicro FPGA方案2021-05-17 1012

-

ADN2850 FMC-SDP转接器和评估板/Xilinx KC705参考设计2021-05-11 2390

-

ADN2850:非易失性存储器,双1024位数字电阻器数据表2021-04-30 1688

-

ADN2850-微控制器无操作系统驱动程序2021-04-22 1207

-

AN-628:ADN2850评估套件用户手册2021-04-18 2264

-

ADN2850 IBIS型号2021-04-09 661

-

双1024位的非易失性存储器ADN2850介绍2020-09-30 3726

-

EVAL-ADN2850-25,适用于电池供电应用和许多其他应用,速度最高可达50 MHz2019-10-21 2330

-

EVAL-ADN2850SDZ,包括RDAC和EEMEM寄存器中的读/写访问,电阻的递增/递减2019-09-03 2866

-

ADN2850非易失性存储器双1024位数字电阻器数据表2017-10-17 1051

-

51单片机控制ADN2850的阻值2016-12-05 2855

-

ADN2850,pdf datasheet (1024-Po2009-09-22 765

全部0条评论

快来发表一下你的评论吧 !