基于PID闭环控制的开关电源传导仿真

描述

前言

开关电源的设计在确保其它参数满足要求的前提下,还需要将功率半导体和功率磁元件开关过程产生的EMI噪声降低到标准限制以下。按照产品设计流程,通常在确定了拓扑方案后,从理论上既可以得到理想情况下的开关传导噪声特性,而实际产品测试中需要考虑到开关环路杂散参数和实际器件中的杂散参数带来的影响。其中既有杂散参数的引入造成系统传递函数变化的影响,又有磁元件等高di/dt、dv/dt器件或线路在工作中的电磁场耦合的影响。这些影响在设计前期很难简单的预估,但却严重影响开关电源的传导特性。

本文通过使用ANSYS等工具,提取开关电源中的杂散参数,通过模拟电源工作环境获得接近实际工作时的传导特性。

为了方便,这里使用了某产品的PCB设计,其主电源采用DC12V输入,3.3V/2A输出,芯片方案采用TI公司的LMR14030。该方案为非隔离BUCK方案,常见于汽车电子等小功率电子设备中。

电源拓扑设计

1.1、基本参数

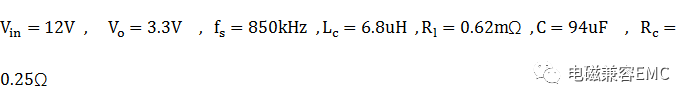

已知

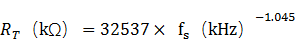

其中 为开关频率,根据LMR14030规格书中给出的

为开关频率,根据LMR14030规格书中给出的 阻值和

阻值和  的关系式得出。

的关系式得出。

(1)

为输出电感

为输出电感 的直流电阻,其值由PExprt计算得到。

的直流电阻,其值由PExprt计算得到。 为输出电容引脚电阻,根据SIwave中电容库参数得到。

为输出电容引脚电阻,根据SIwave中电容库参数得到。

图1、PExprt中输出电感参数

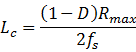

根据张占松的《开关电源原理与设计》中的公式

代入数据可得 。由规格书中可知电源芯片的最大供电能力为3.5A,因此电源多数情况下工作在CCM模式下。要求输出电压纹波

。由规格书中可知电源芯片的最大供电能力为3.5A,因此电源多数情况下工作在CCM模式下。要求输出电压纹波 ,根据下式

,根据下式

可得电容大小为 实际取值为2颗47uF电容并联。

实际取值为2颗47uF电容并联。

1.2、BUCK的开环仿真

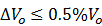

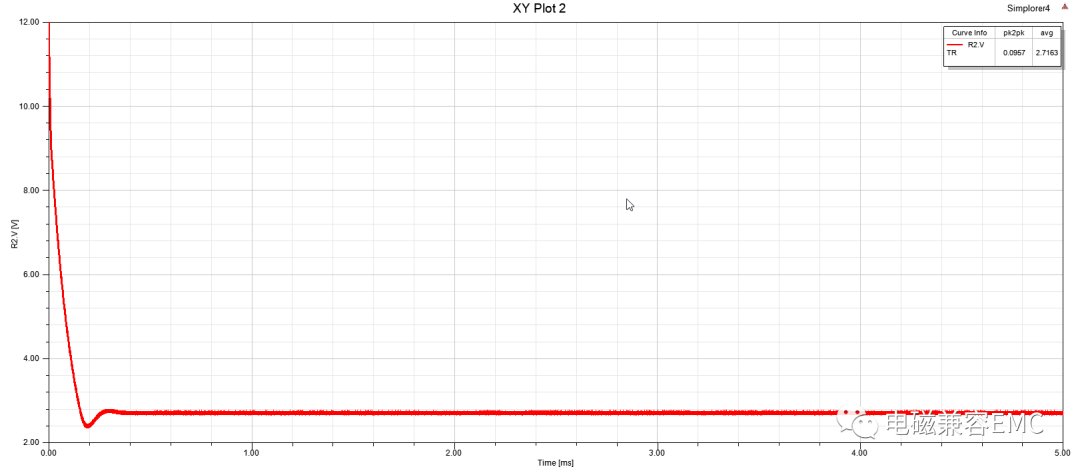

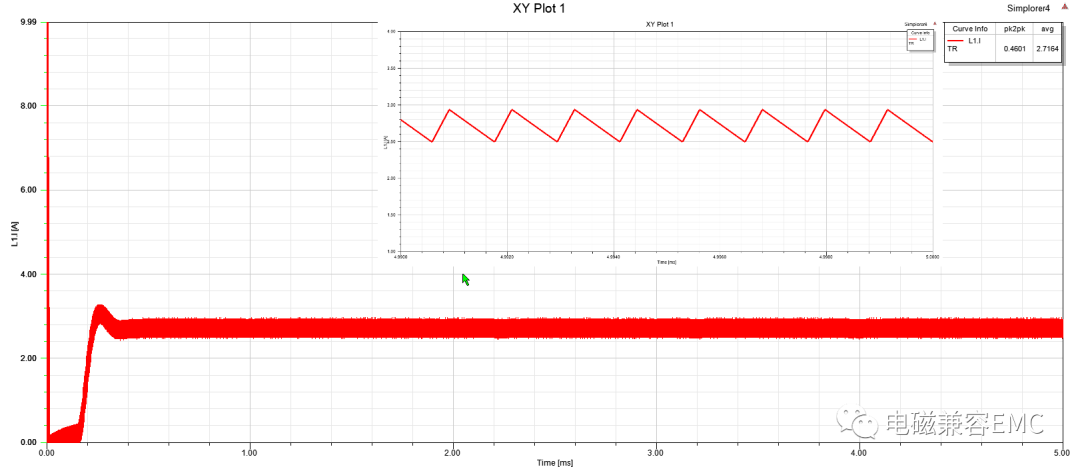

利用simplorer搭建如下电路,将上面参数定义到对应器件中。其中开关频率为850khz,占空比为0.275。最终得到的电感电流和输出电压波形如下图所示。

图2、BUCK开环仿真拓扑

图3、负载电阻电压

图4、输出电感电流

由电感电流结果可知,电路确实工作在CCM模式。负载电阻纹波电压为0.096V,电压平均值为2.72V,纹波电压超出设计要求。原因主要为输出电容选择了一个ESR较大的物料,当调整为0.02Ω后,电压纹波降低到0.4%,符合要求。开始选择的47uF电容为1206封装,观察物料库中该封装尺寸的ESR,对比同样容值2816封装尺寸电容,可以发现小封装尺寸电容具有更大的ESR值。

图5、不同封装电容的寄生电阻对比

1.3、闭环仿真

理想情况下Buck电路的传递函数为

其中, ,

, ,

, ,代入数据可得它们的值如下:

,代入数据可得它们的值如下:

,

, ,

, .

.

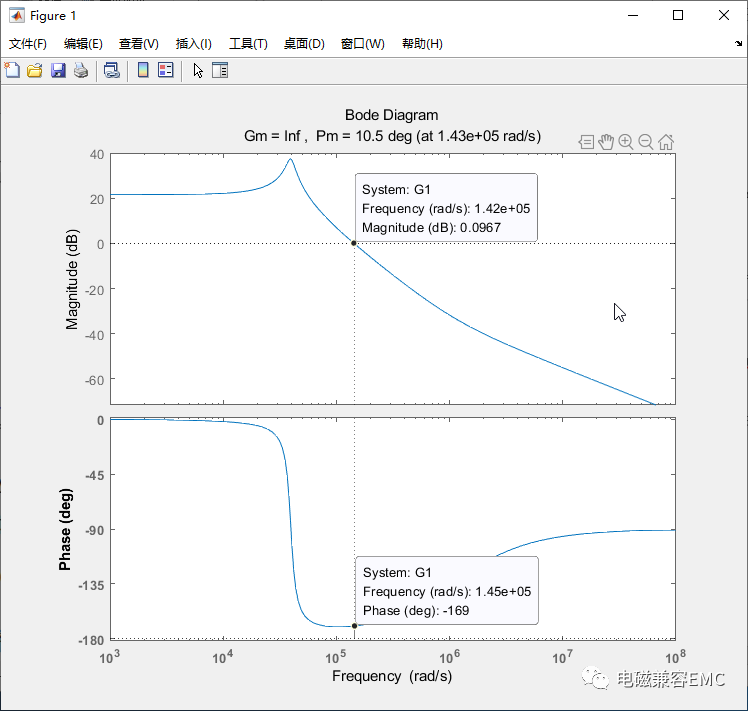

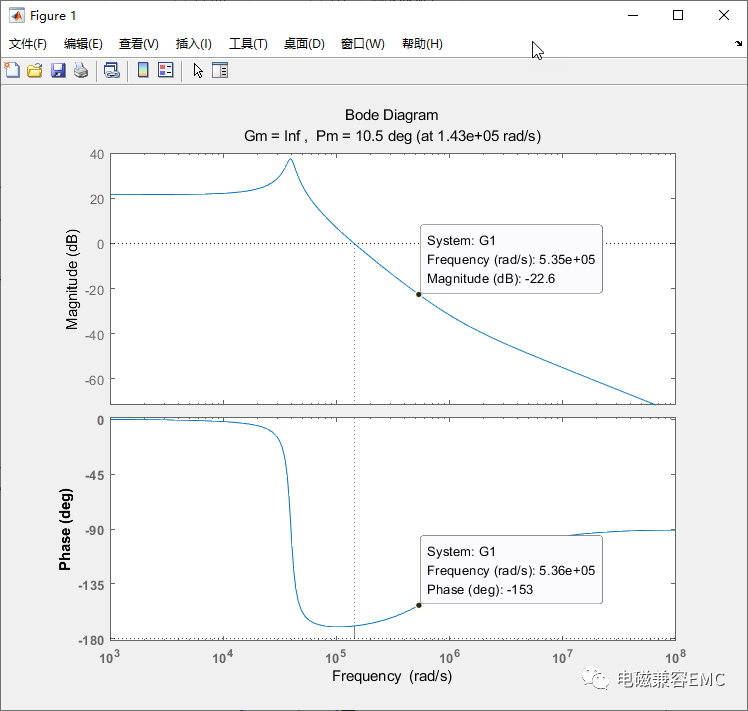

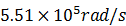

采用MATLAB计算得到所设计的开环Buck幅频相频特性曲线如下

图6 开环Buck幅频相频特性曲线

由上图可知,穿越频率为 ,开环Buck的相位裕度为10.5°,小于45°,需要进行相位补偿。增益裕度不需要补偿。

,开环Buck的相位裕度为10.5°,小于45°,需要进行相位补偿。增益裕度不需要补偿。

常用的补偿方式有比例补偿,PI补偿,PD补偿,PID补偿等等。我们只要选取一种补偿方式使其相位裕度大于等于45°,幅值裕度大于7dB就可以了。

我们选取补偿后的穿越频率 ,对应的角频率为

,对应的角频率为 ,利用MATLAB的点捕捉功能,在图上捕捉出角频率为

,利用MATLAB的点捕捉功能,在图上捕捉出角频率为 的点,如下图所示。

的点,如下图所示。

图7、 85kHz幅频相频点捕捉图

由上图可知,在频率为 85kHZ 处的相角为-161°。如果单单采用比例补偿,是不行的。因为采用比例补偿将开环 buck 的穿越频率由 增加到

增加到 后,此时的相位裕度为 180°-153°=27°<45°,显然不行。频率为 85kHZ 处的相角为-161°,要是 buck 稳定,在此处的相角最小应该为-135°(此时对应的相位裕度刚好为45°),只有这样,最终的相位裕度才能大于等于 45°。所以,应该找一个相频曲线有大于 0 的部分补偿网络对该 buck 进行补偿(这里采用 PI 补偿是不行的,有兴趣的可以自己尝试)。根据各类补偿网络的相频曲线可知,有 PD、PID 补偿网络的相频曲线存在大于 0 的部分。在这里,为了增大静态增益,我们选取 PID补偿网络对系统进行补偿(有

后,此时的相位裕度为 180°-153°=27°<45°,显然不行。频率为 85kHZ 处的相角为-161°,要是 buck 稳定,在此处的相角最小应该为-135°(此时对应的相位裕度刚好为45°),只有这样,最终的相位裕度才能大于等于 45°。所以,应该找一个相频曲线有大于 0 的部分补偿网络对该 buck 进行补偿(这里采用 PI 补偿是不行的,有兴趣的可以自己尝试)。根据各类补偿网络的相频曲线可知,有 PD、PID 补偿网络的相频曲线存在大于 0 的部分。在这里,为了增大静态增益,我们选取 PID补偿网络对系统进行补偿(有 部分)。

部分)。

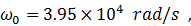

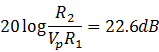

1.4、PID补偿网络的参数设计

采用 PID 补偿网络对我们的开环 buck 进行补偿,按照以下步骤就可以确定 PID补偿网络的各个参数。

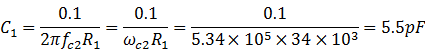

首先将穿越频率调整到 处,具体计算方法如下:

处,具体计算方法如下:

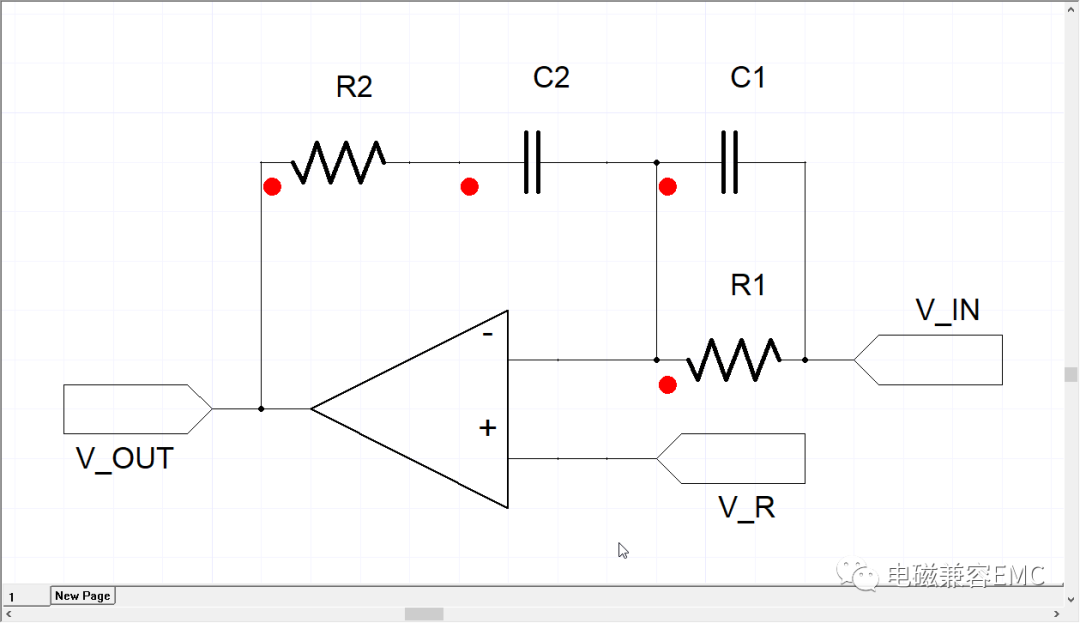

还是使用点捕捉功能,在 matlab 画出的幅频相频曲线上捕捉角频率为 的幅值,如图 7 所示,可得此时幅值为-22.6dB,所以补偿网络的应该在开环的幅频曲线基础上加上22.6dB (向上平移22.6个单位),使穿越频率额由

的幅值,如图 7 所示,可得此时幅值为-22.6dB,所以补偿网络的应该在开环的幅频曲线基础上加上22.6dB (向上平移22.6个单位),使穿越频率额由 变成到

变成到 。平移多少个单位,也可以通过计算得来。计算很简单,如下:

。平移多少个单位,也可以通过计算得来。计算很简单,如下:

所以 85kHz 对应的点也在斜率为-40dB的直线上,因此在相频曲线上取角频率为 和

和 的两个点(设这两个点的幅值分别为

的两个点(设这两个点的幅值分别为 和

和 (单位dB)),利用直线斜率的定义可得:

(单位dB)),利用直线斜率的定义可得:

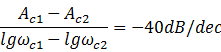

显然有 (穿越频率过横轴),所以可得

(穿越频率过横轴),所以可得

(和-22.6差不多)

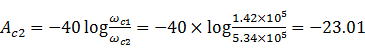

补偿网络的电路图如下:

图8、PID补偿网络电路图

原理图中给出的采样网络电阻值分别为 和

和 。取

。取 (

( 是三角波峰值,闭环网络传递函数里最终会因为三角波的比较环节引入一个

是三角波峰值,闭环网络传递函数里最终会因为三角波的比较环节引入一个 的比例因子,也相当于一个比例环节,所以这里需要将它带上),则有:

的比例因子,也相当于一个比例环节,所以这里需要将它带上),则有:

所以

。将PID网络的比例系数P乘到开环Buck传递函数里得到的传递函数如下:

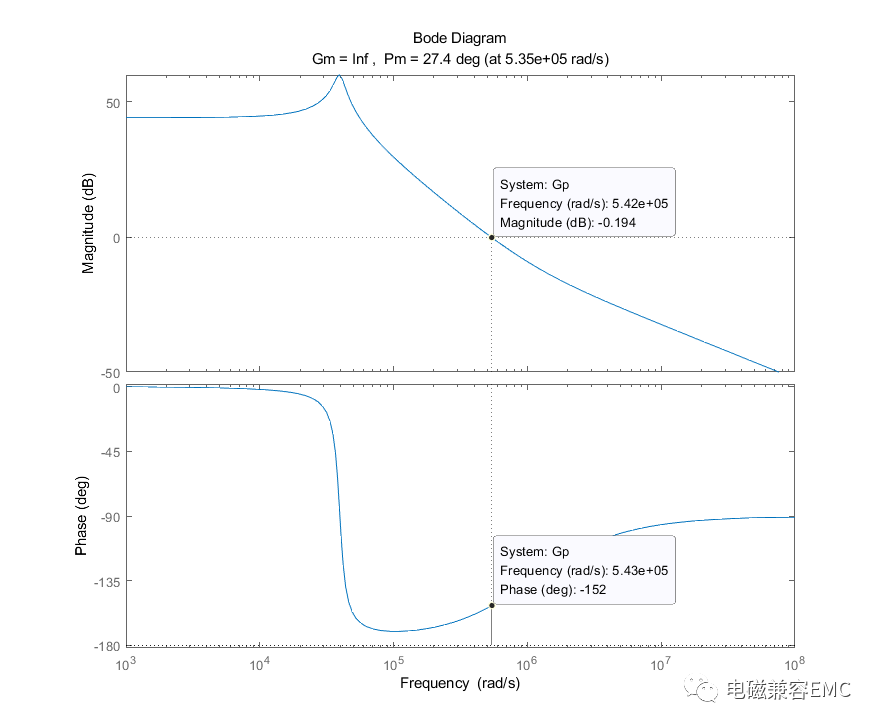

在MATLAB 中计算上述传递函数,可以得到 的幅频相频曲线如下图所示:

的幅频相频曲线如下图所示:

图9、传递函数Gp的幅频相频曲线

由上图可知,传递函数 穿越角频率为

穿越角频率为 ,很接近85kHz,所以R2选择基本合理。此时相裕角度也增加到了28°,几乎与153°互补,说明计算正确。

,很接近85kHz,所以R2选择基本合理。此时相裕角度也增加到了28°,几乎与153°互补,说明计算正确。

2)提高静态增益

为了能够使用 PID 补偿网络提供开环 buck 的静态增益,又不影响到它的幅值裕

度(为什么会影响到幅值裕度请观察 PID 补偿网络的相频曲线)。

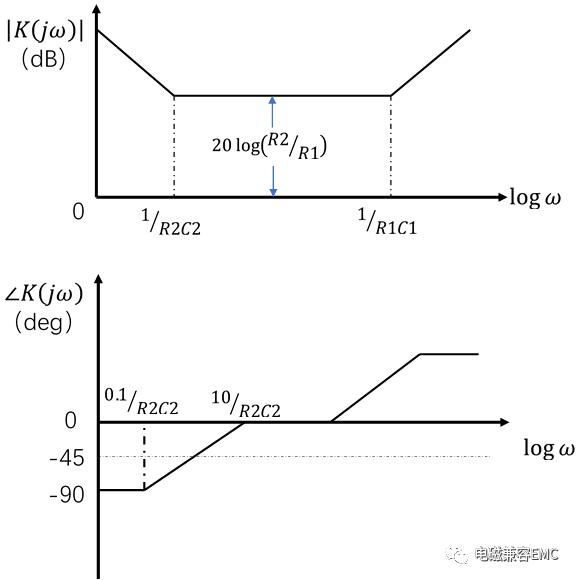

图10、PID网络的相频曲线

因为 PID 补偿的相频曲线有个从-90°增加到 0°的过程,而开环 buck 的相频曲初始有个从 0°向 180°减小的过程,如果把这个这两个过程叠加起来,可能为产生一个-180°的相角。这个-180°相角对应的频率所对应的幅值就是系统的幅值裕度的相反数。而在这两个过程中,PID 补偿网络的幅值一直为正,开环 buck的幅值也一直为正。这样一来,叠加后的幅值必然大于 0,从而幅值裕度必然小于 0,显然是不行的。因此,为了避免产生这种情况,我们应该选取合适的C2。根据 PID 补偿网络和 Gp 的相频曲线可知,如果我们使得下式成立,那么一定不会出现上文所说的那种情况。

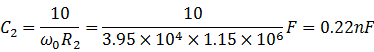

所以可得

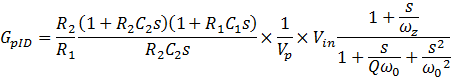

现在可将PID补偿网络的PI部分加入开环Buck的传递函数中,得到新的传递函数如下:

根据这个传递函数的幅频相频曲线可以判断我们选取的 ,

, 是否合理。

是否合理。

在MATLAB 中重新运行计算可得到传递函数 的幅频相频特性曲线如下图所示:

的幅频相频特性曲线如下图所示:

图11、传递函数Gp1 的幅频相频特性曲线

由上图可知, 的穿越角频率为

的穿越角频率为 ,与

,与 的穿越角频率一致,接近85kHz。相位裕度为27°,相对于

的穿越角频率一致,接近85kHz。相位裕度为27°,相对于 的28°几乎不变。这里没有出现我们上文说的幅值裕度为负的那种情况,说明我们选择C2的值基本合理。接下来,我们需要做的就是增大相位裕度,使其大于等于45°。

的28°几乎不变。这里没有出现我们上文说的幅值裕度为负的那种情况,说明我们选择C2的值基本合理。接下来,我们需要做的就是增大相位裕度,使其大于等于45°。

3)提高相位裕度

观察PID补偿网络的相频特性曲线可知,如果要提高开环Buck的相位裕度,应该PID补偿网络的相频曲线上相角大于(45°-27°)=18°的部分加到 上,也就是有

上,也就是有 。如果我们先取

。如果我们先取 试试看,此时可确定

试试看,此时可确定 的值如下:

的值如下:

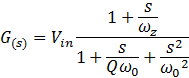

经过PID补偿后,闭环网络的传递函数 如下:

如下:

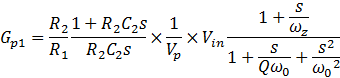

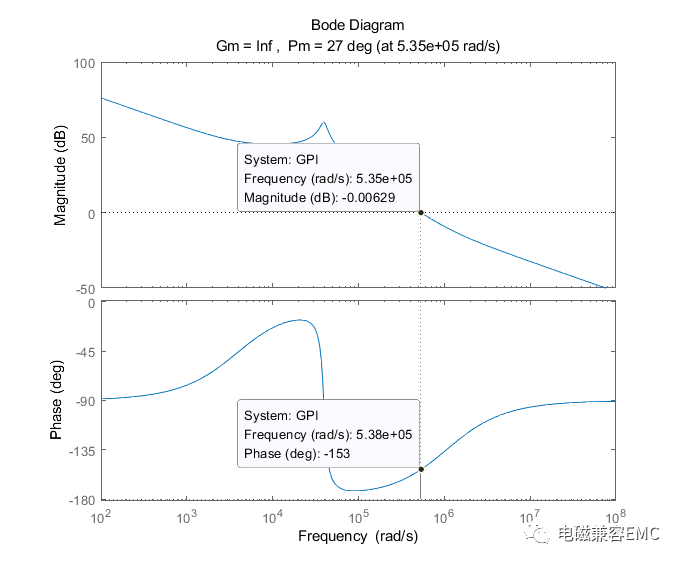

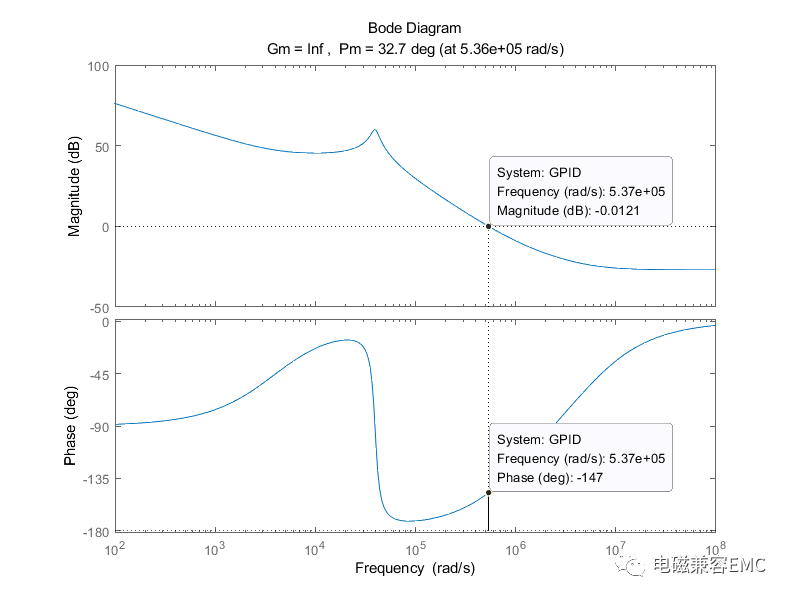

通过MATLAB 可得 的幅频相频曲线如下图所示:

的幅频相频曲线如下图所示:

图12、GpID 的幅频相频曲线

的穿越角频率为

的穿越角频率为 ,接近85kHz,但是相位裕度为33°偏小。我们在此技术上增大C1,相位裕度也会增加,经过一番尝试后最终取得C1=18pF,此时闭环Buck的幅频相频曲线如下:

,接近85kHz,但是相位裕度为33°偏小。我们在此技术上增大C1,相位裕度也会增加,经过一番尝试后最终取得C1=18pF,此时闭环Buck的幅频相频曲线如下:

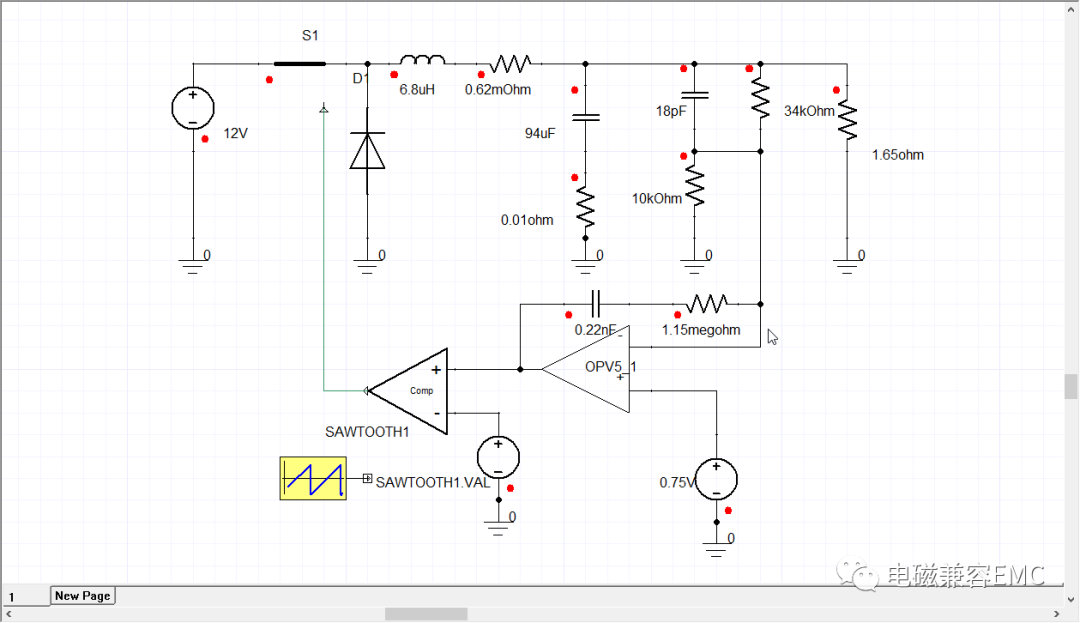

图13、最终幅频相频曲线

由上图可知,闭环Buck的穿越角频率为 ,相位裕度为46.3°,幅值裕度为无穷大,满足要求。至此PID补偿网络的参数全部计算完毕,下面开始进行闭环Buck的仿真。

,相位裕度为46.3°,幅值裕度为无穷大,满足要求。至此PID补偿网络的参数全部计算完毕,下面开始进行闭环Buck的仿真。

1.5、Buck闭环仿真

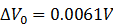

闭环仿真电路如下图所示:

图14、闭环仿真电路拓扑

这里需要注意放大器中传输频率(放大器带宽)参数的设置,由于放大器具有频率响应特性,如果其传输频率接近采样电阻输入电压的波动频率,就会出现信号失真的情况,这里我们先不考虑由于实际放大器在工作中出现的信号失真问题,所以将其传输频率设置为200MHz,即远大于电路开关频率850kHz。

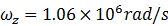

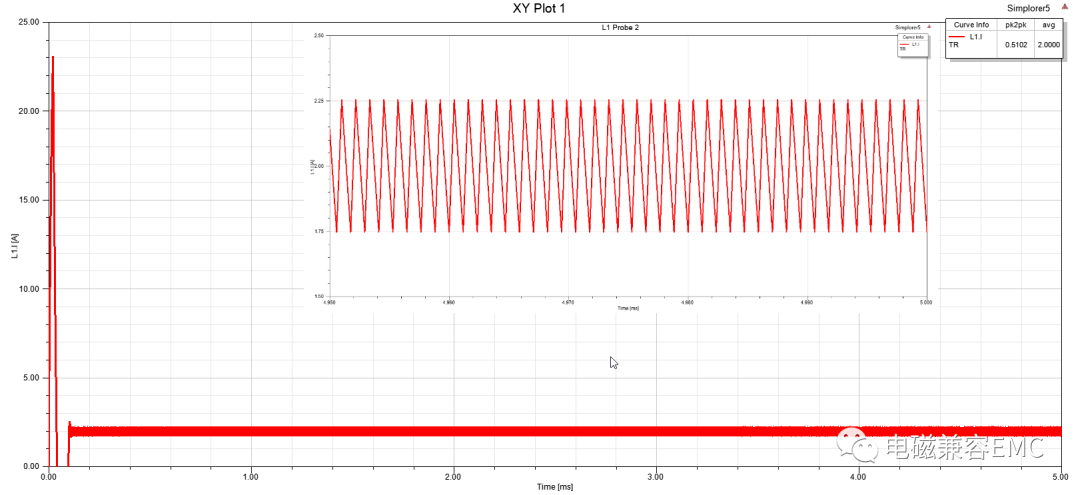

仿真结束后的电感电流波形如下图所示,电流峰峰值的0.5倍小于电感平均电流值,buck工作在CCM模式。下图中的三角波为将电流波形进行局部放大的部分。

图15、电感电流波形

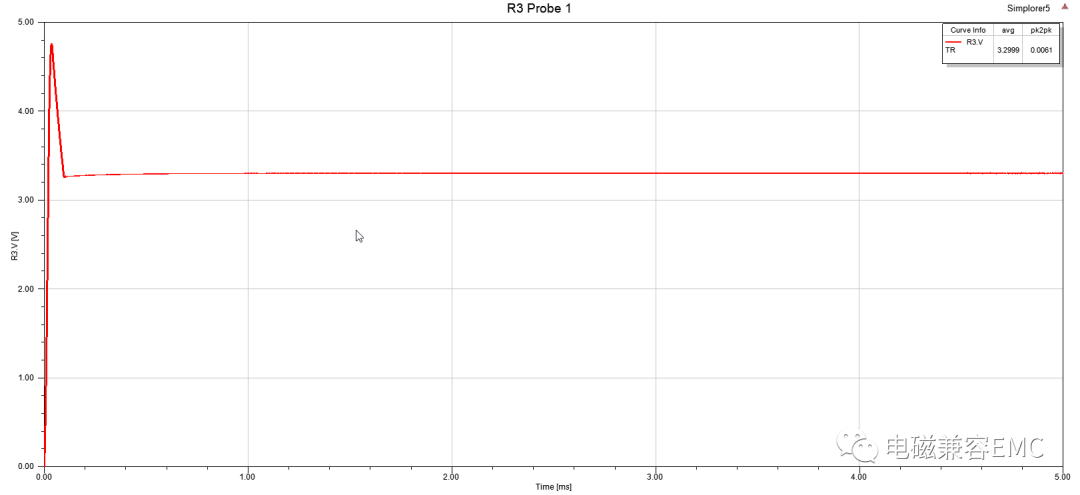

图16、负载电阻电压波形

输出电压 ,纹波电压

,纹波电压 ,纹波电压

,纹波电压

,满足设计要求。

前面仿真采用了具有实际物理参数的模型,所以其环路响应过程存在特定的幅频相频响应特性,如果以纯粹的数学模型替代,是不需要对环路部分进行补偿的。如下面就采用数学模块替代放大器、电容电阻和比较器,其具有简单且计算结果理想的特点。方便最终进行验证。下图a中的模块搭建最为简单方便,图b中需要对PID模块中的P、I、和D参数进行合理的设置,才可得到正确的结果。

(a)

(b)

图17、采用数学模块作为环路控制

2、PCB及磁元件寄生参数的提取

2.1、PCB的寄生参数提取

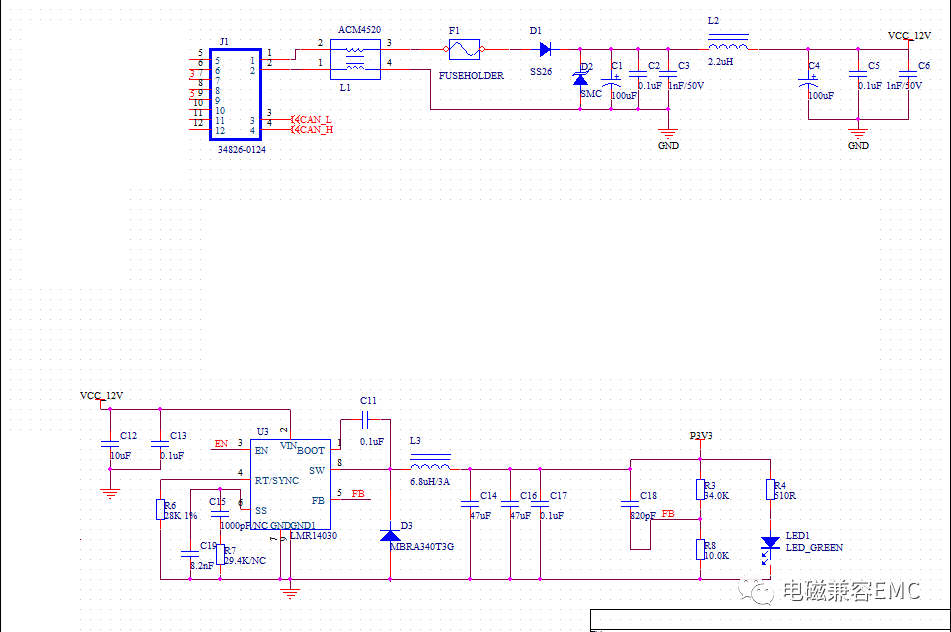

下图为本次需要仿真的电源原理图和PCB部分,该电源采用TI公司的LMR14030芯片方案。其开关特性已经由第一章中结合芯片参数与环路补偿计算获得,其计算结果应该接近电源实际工作的状态。由于无法获得该芯片的spice模型,所以采取第一章中的控制模型,下图U3电源芯片中的EN、RT/SYNC、SS和BOOT管脚在实际工作中对EMI传导噪声的影响并不大,所以没必要对这些管脚内部的电路进行建模。

图18、主电源部分原理图

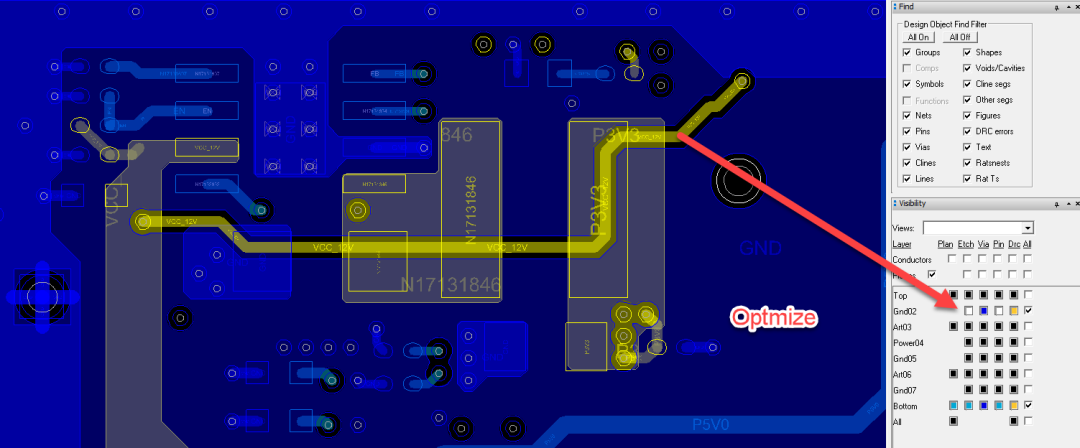

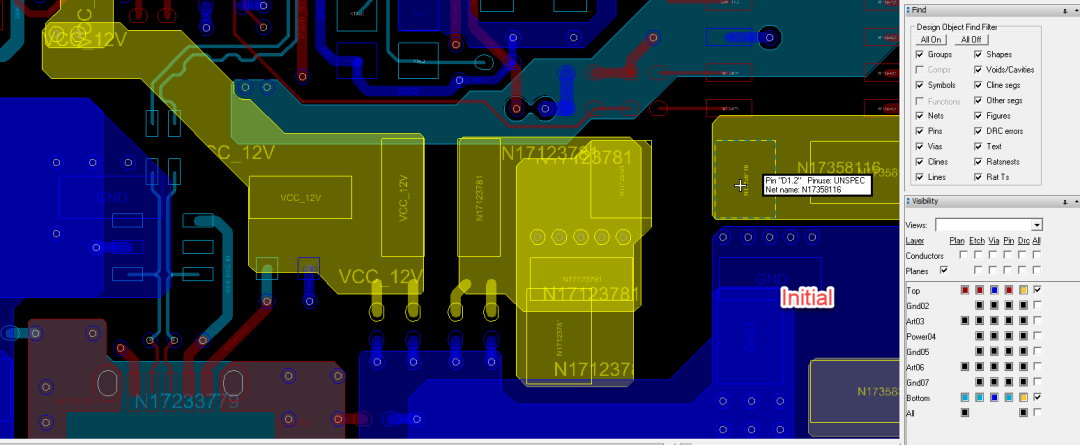

图19、主电源(黄色部分)PCB布局

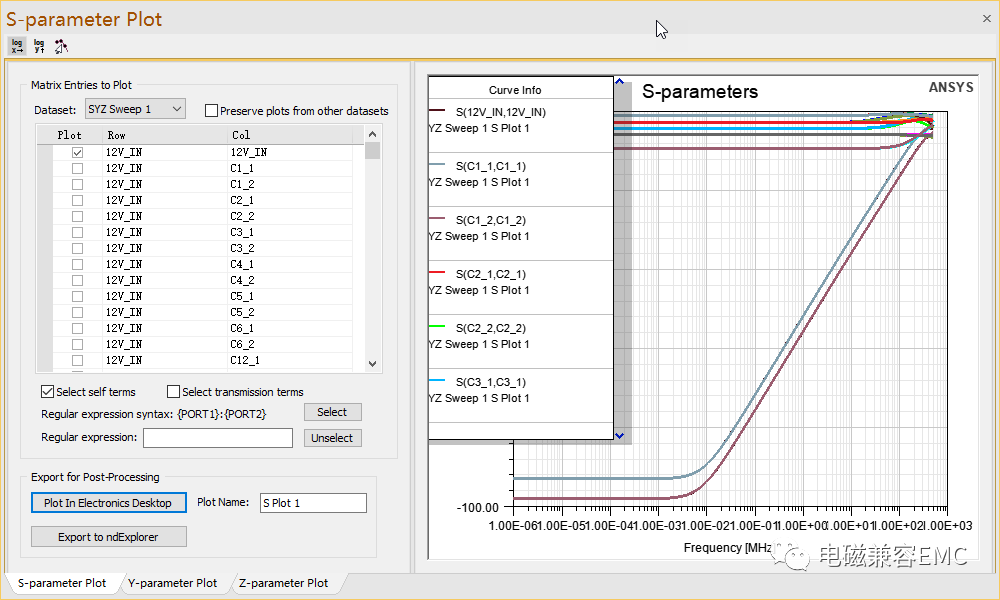

将PCB文件导入SIwave软件中,将目标电源部分网络中的各器件设置为端口,抽取宽频S参数。

图20、PCB文件的S参数

2.2、磁元件模型建立

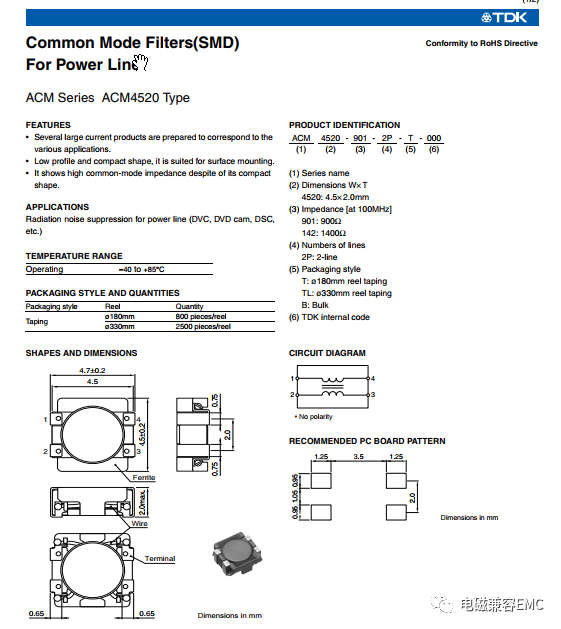

由图18原理图部分可以知道,12V电源部分包含3个电感原件,分别为L1、L2、L3,其中L1为TDK公司的ACM450型号共模电感,其参数如下,粗略计算得到该共模电感的感值为1.4uH。L2和L3为未知厂家的差模电感。

图21、L1共模电感参数

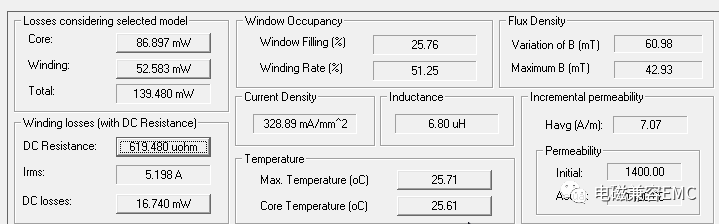

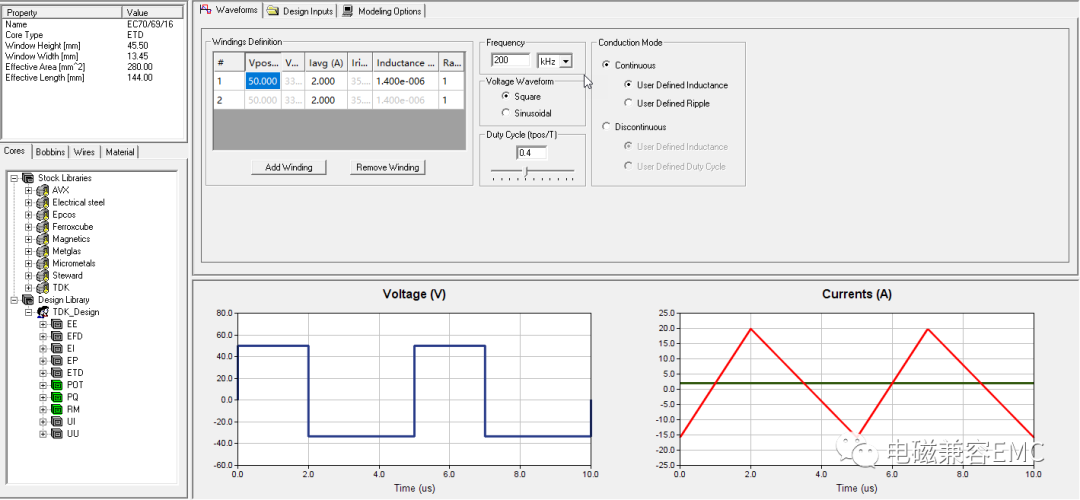

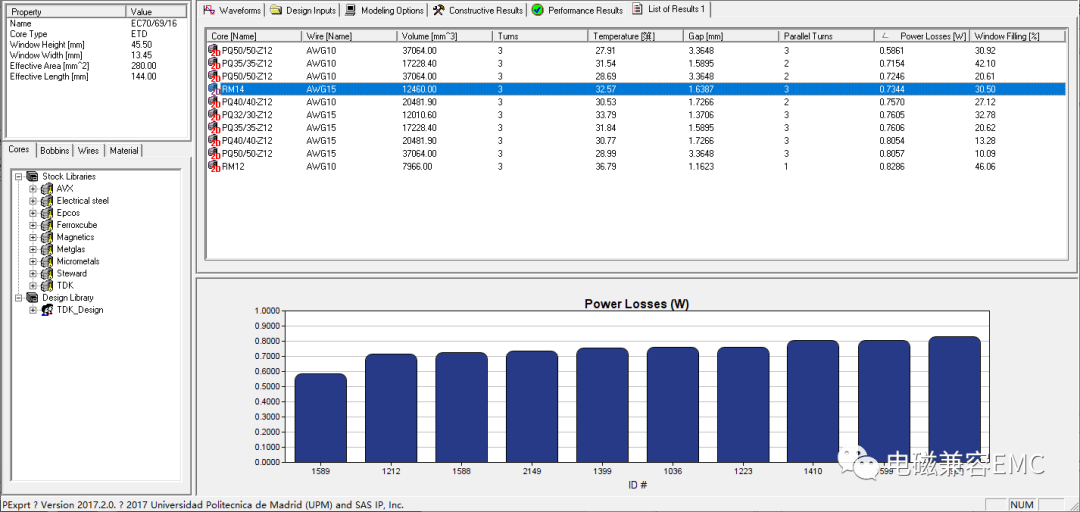

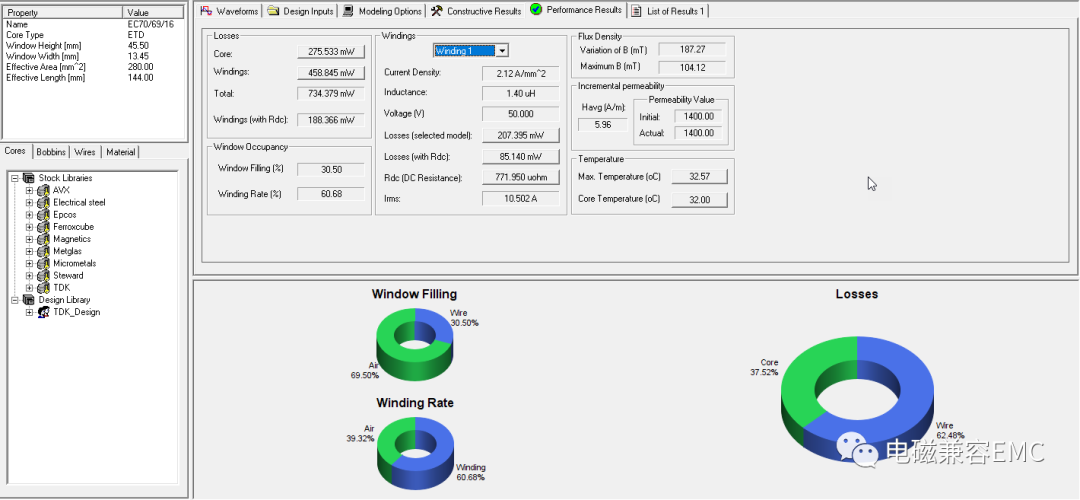

新建PExprt文件,选择共模电感,输入电感的电压电流和感值,然后选择TDK公司的磁芯。由软件给出自动设计得到的结果。我们选择RM14磁芯作为本次电感模型的磁芯。计算得到的电感参数如下图所示。

图22、共模电感L1的设计参数

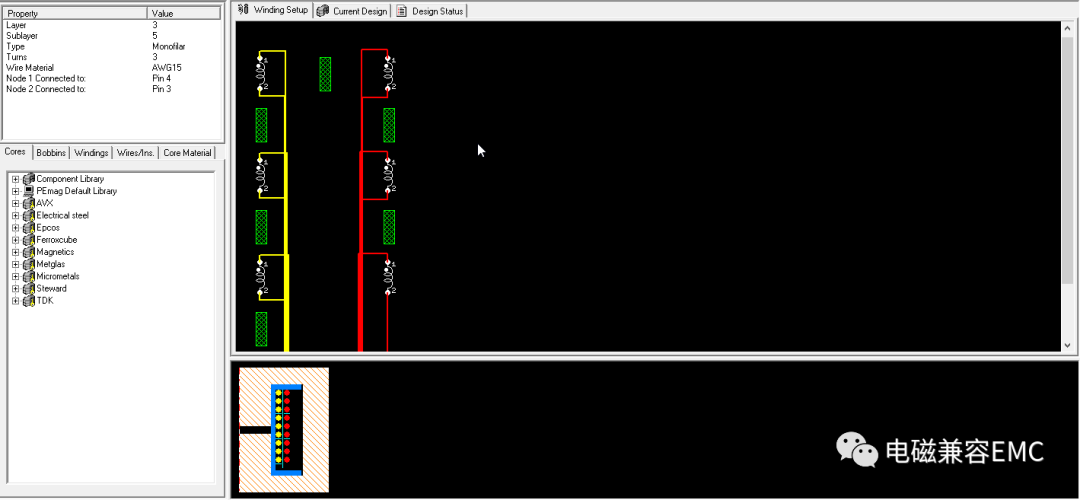

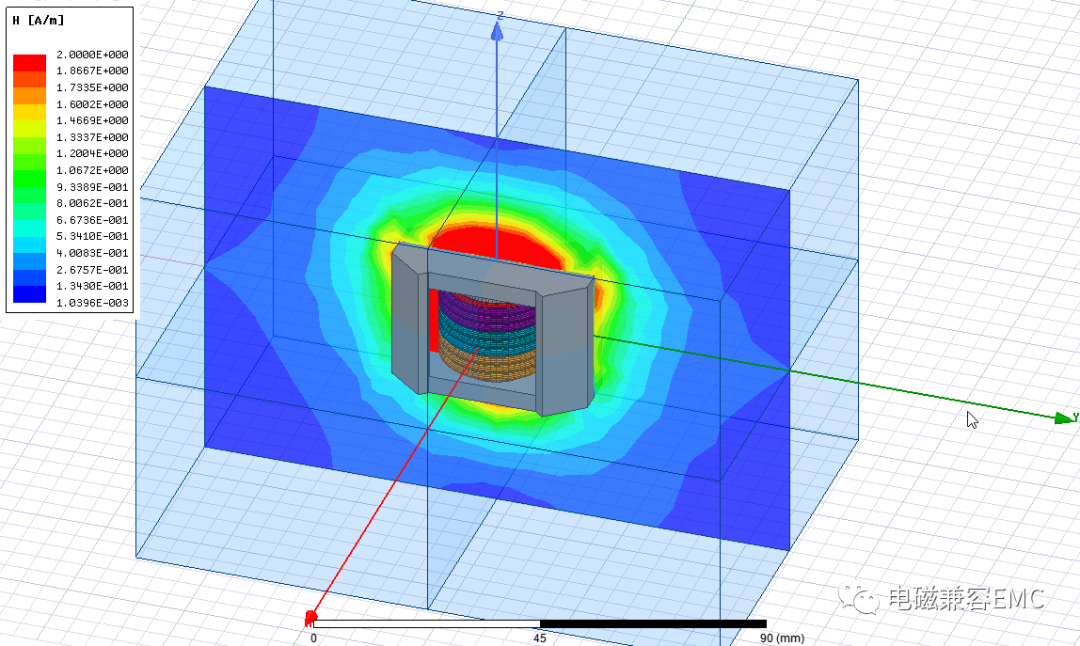

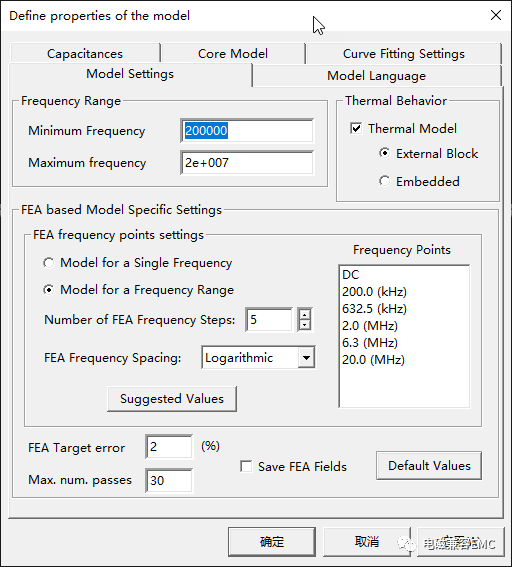

设计完毕后,将选择的方案导入到PEmag中,由PEmag自动生成电感的Maxwell模型,并完成求解过程。求解完成后,将其导出为SML模型,以方便simplorer调用。

图23、共模电感L1的绕组结构以及Maxwell磁场分布

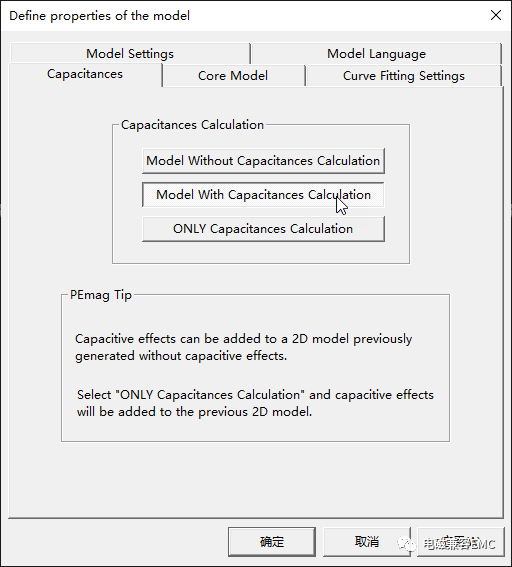

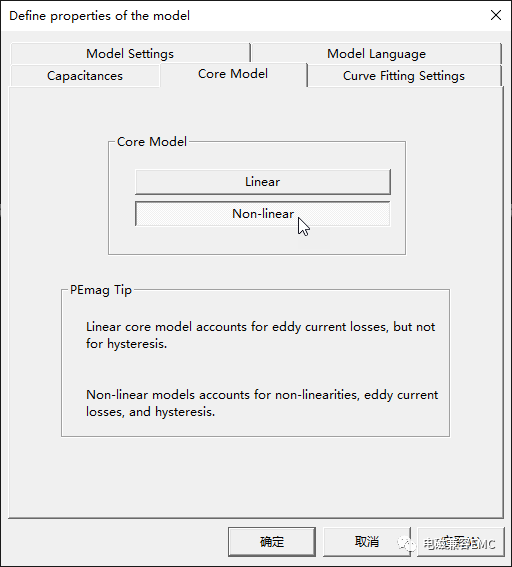

由于磁芯材料具有非线性,实际电感需要考虑匝间电容效应,所以求解过程中这些因素都要考虑进去,按照下图参数设置。

图24、求解设置

与L1的设计过程一样,L2选择TDK公司PC50材质、RM12形状的磁芯,L3选择Epcos公司PC50材质,PM70形状的磁芯。

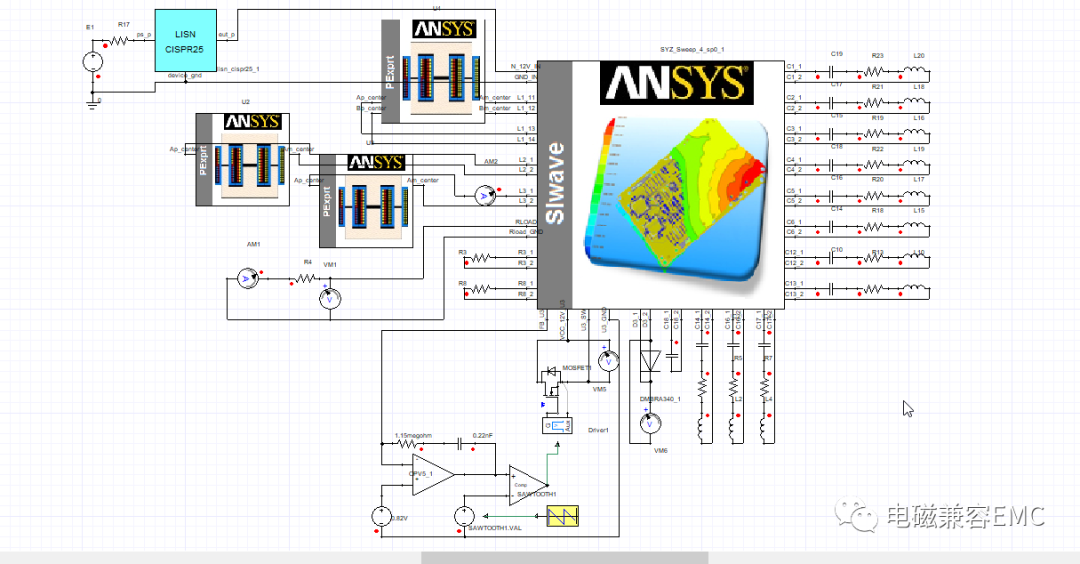

2.3、传导仿真系统电路搭建

SIwave求解PCB文件后,获得了电源走线部分的宽频S参数。由PExprt设计电感原件,然后由Maxwell对电感模型进行三维求解。同时也根据第一章部分得到该电源的环路控制部分参数。至此,系统仿真电路所需的参数已经全部获得,打开simplorer,将SIwave模型以SML模型形式导入,然后导入电感原件的SML模型,并将PID控制环路添加进来。最终得到下图电路。

图25、系统仿真电路

上图仿真电路中的电容采用含有寄生参数的集总电路表示,以描述其在宽频范围内的非线性特征。其特征值采用SIwave电容库中各大电容厂家给出的电容参数,具体如下表所示。

表1、 系统仿真电路中的电容参数

| 电容代号 | C1、C4 | C14、C16 | C12 | C2、C5、C13、C17 | C3、C6 |

| 容值 | 100uF | 47uF | 10uF | 0.1uF | 1nF |

| ESR | 90mΩ | 20mΩ | 300mΩ | 0.06Ω | 240mΩ |

| ESL | 0.28nH | 0.49nH | 0.56nH | 0.82nH | 0.298nH |

| 封装 | 08X10 | 1206 | 0603 | 0402 | 0402 |

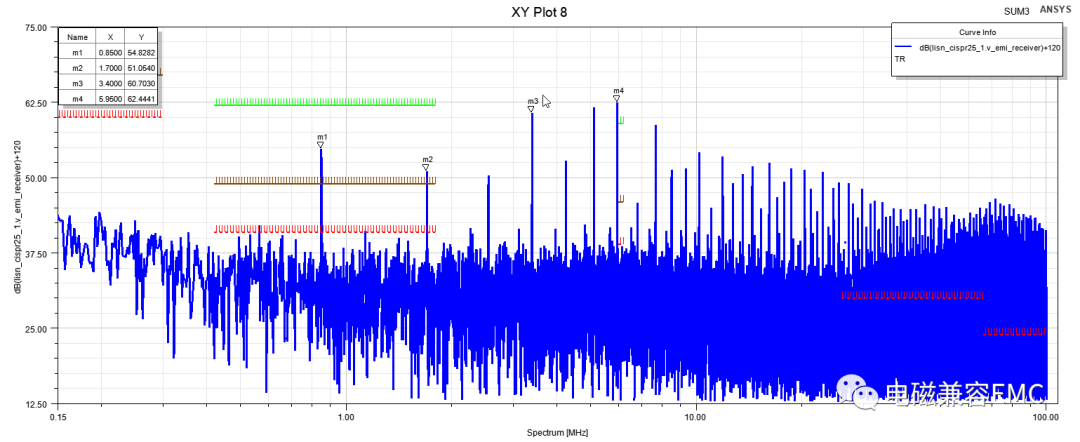

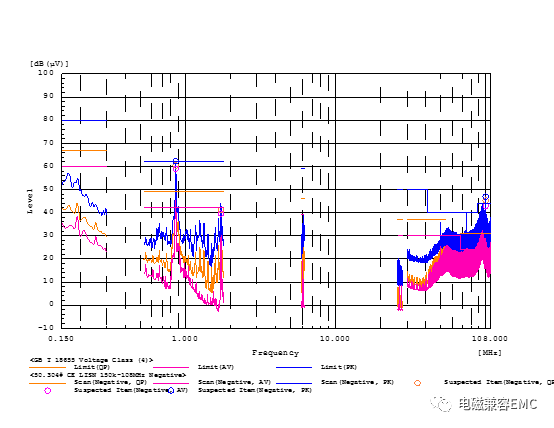

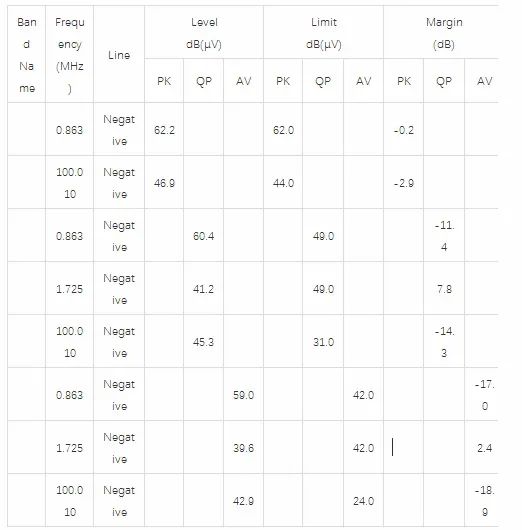

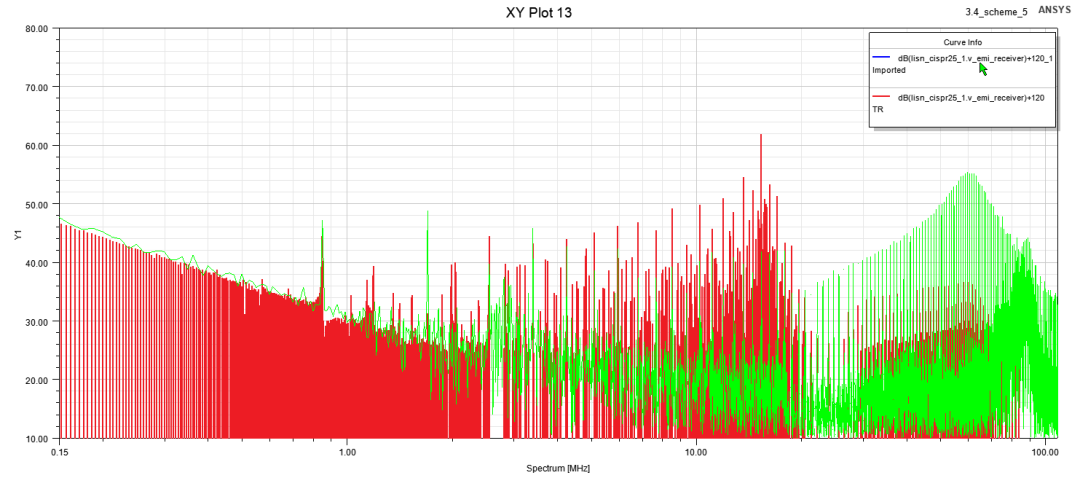

仿真完成后,将LISN上检测到的传导噪声经过傅里叶变换得到频域结果,如下图所示,可以看到,开关频率的基频和二次谐波超标,6MHz左右几乎刚刚躲过限制线,高频超标。

图26、传导仿真结果

下图为测试结果,由于没有采用连续频谱测试,丢失了很多信息,从现有的数据来开,基频实测PK值62.2dBuV,仿真结果中该频率为54.8dBuV,1.7MHz位置仿真结果为51dBuV,实测结果PK值约为45dBuV。

图27、传导测试结果

3、结果分析及优化

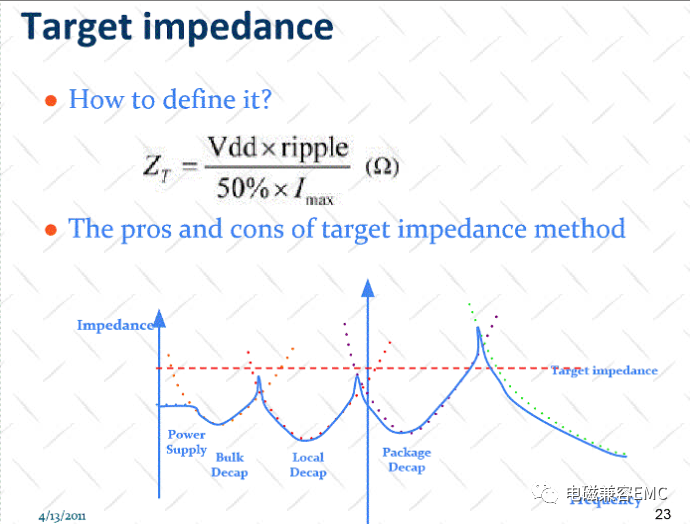

产品前期设计中,工程师是无法凭借个人经验直接对电源传导噪声进行有效的优化的。而优化无非是优化开关电源拓扑,PCB布局布线,和接口滤波电路这三种方式,从操作性和难易程度来讲,三种方式依次降低。第一种方式可实现性最低,因为EMC工程师在电源拓扑选择上是没有多少话语权的。第二种方式需要根据传导噪声在PCB上的分布,对PCB走线布局进行重新设计的,而优化PCB走线及布局是需要结构和layout工程师配合进行的。EMC工程师最具话语权的方式仅剩滤波电路了,这里就尝试采用PI中目标阻抗优化的方式,快速调整输入端电源网络的阻抗特性,增加高频隔离度。

注:这里仅提供电容部分优化思路,电感部分的逻辑是一致的,对于电容无法照顾到的频段,可以采用电感进行补充,其过程无非是调整电感参数将整个阻抗曲线控制在更低水平。

根据oldfriend电源完整性优化设计文章中对目标阻抗的设计,文章中给出的建议是0.5*Imax(以1/2最大电流值作为目标值)。

图28、目标阻抗的设定

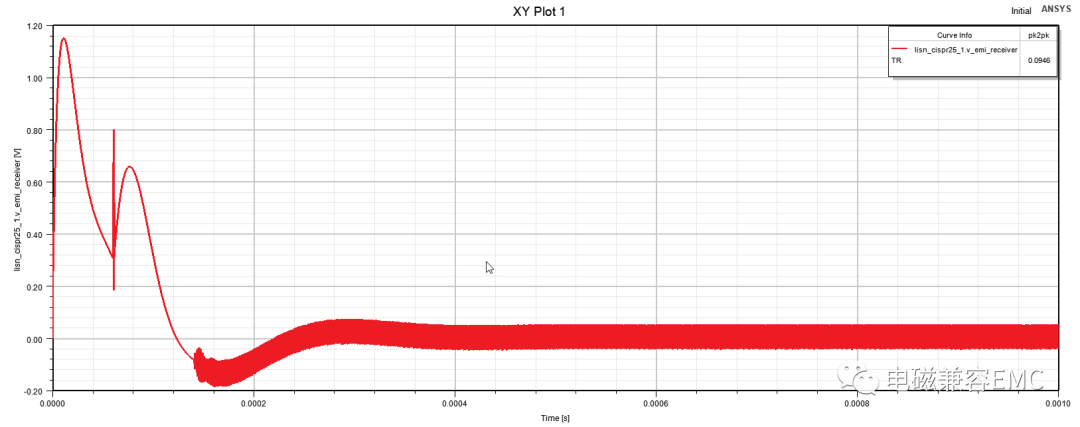

由于最终是以LISN端接收到的纹波大小来评估EMI特性,所以采用第二章中LISN上的传导噪声纹波作为纹波参考,其稳定后的纹波峰峰值为0.095V,负载电流为2.18A,因此目标阻抗设计为0.087Ω。

图29、LISN端的噪声电压波形

3.1、随机电容组合参数

采用siwave中的PI Advisor模块对12V输入网络进行阻抗优化设计,查找siwave电容库中对应封装和容值的电容寄生参数,随机选择满足封装和容值要求的电容型号,其中C1和C4暂且用2816陶瓷电容替代,最终电容参数如下表所示。

表2、随机选取的陶瓷电容参数

| 电容代号 | C1、C4 | C14、C16 | C12 | C2、C5、C13、C17 | C3、C6 |

| 容值 | 100uF | 47uF | 10uF | 0.1uF | 1nF |

| ESR | 46mΩ | 56mΩ | 4mΩ | 0.06Ω | 0.26Ω |

| ESL | 0.28nH | 0.45nH | 0.78nH | 0.82nH | 0.298nH |

| 封装 | 08X10 | 1206 | 0603 | 0402 | 0402 |

3.2、优化电容参数

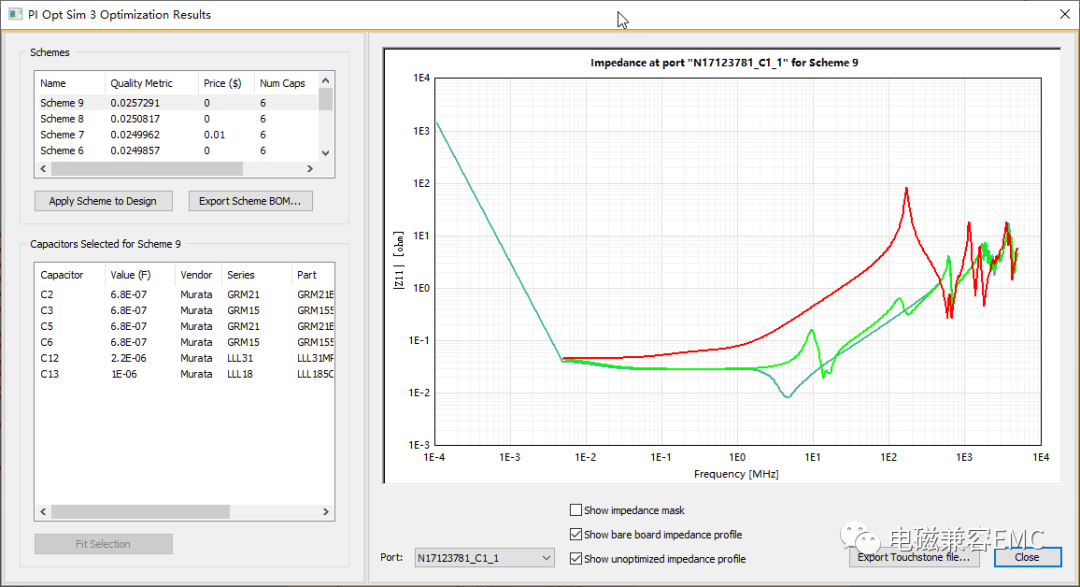

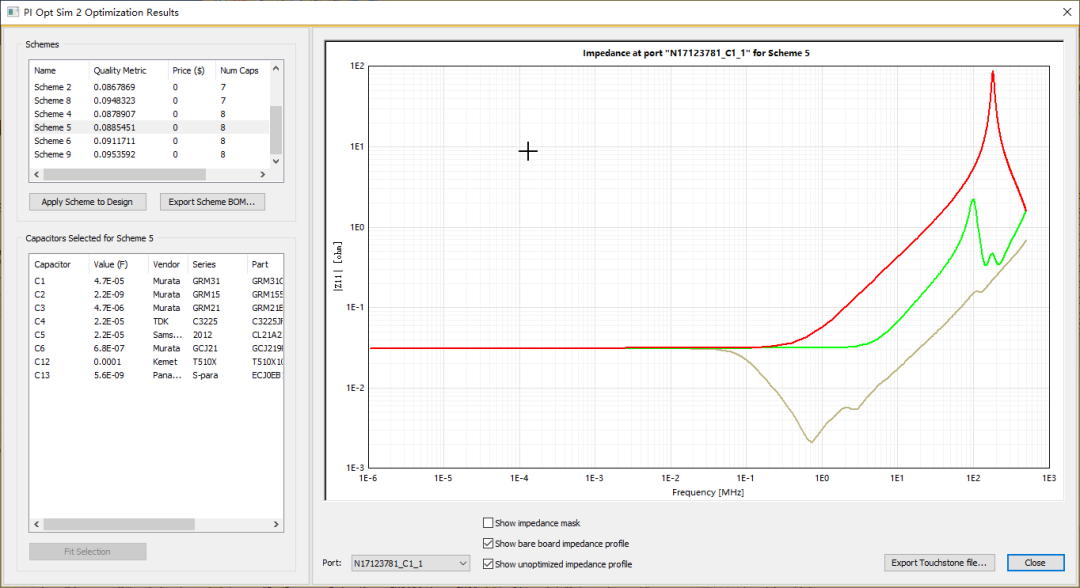

打开PI Advisor,选择0.087Ω作为目标阻抗,得到10个优化方案,分别总结如下

图30、十种优化方案的电容容值及型号

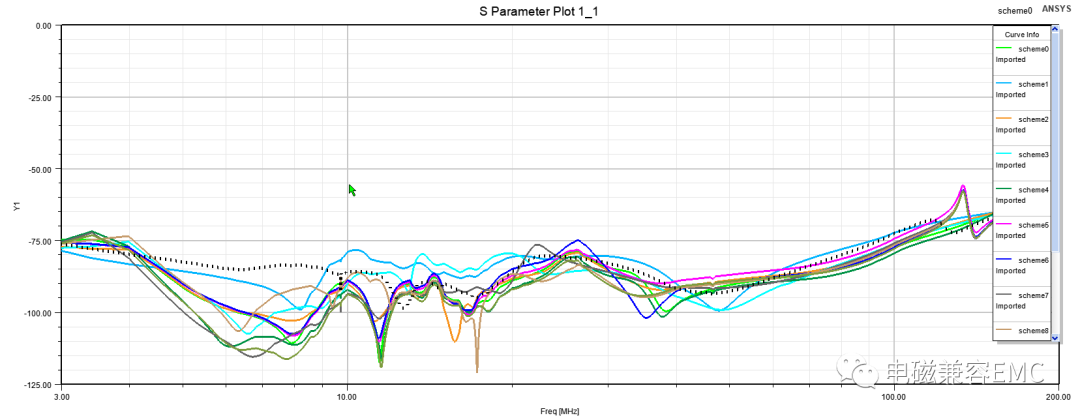

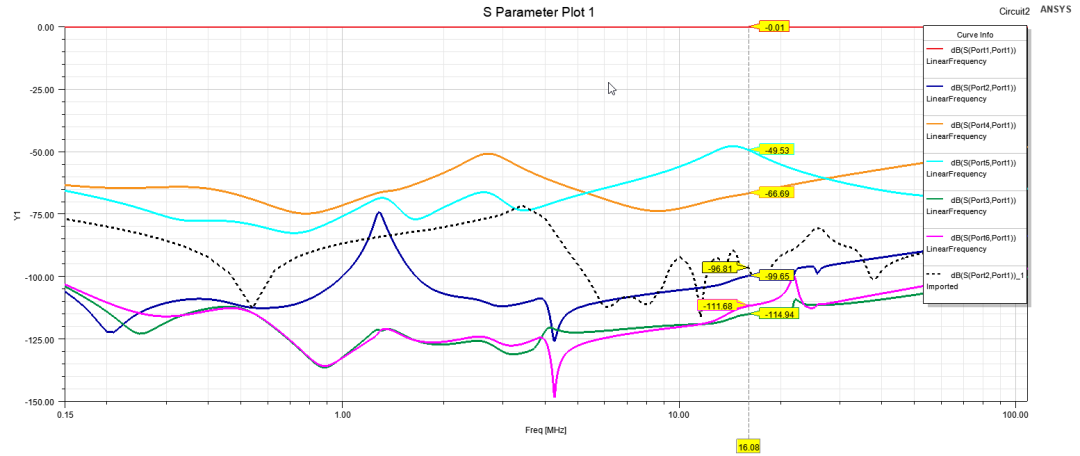

以上十种方案的输入输出隔离度结果对比如下,对比可见其中第4种结果的隔离度较好。缺陷在于该方案在低频3MHz左右的阻抗高于初始方案。

图31、不同电容方案的S参数对比

3.3、电容结果对比

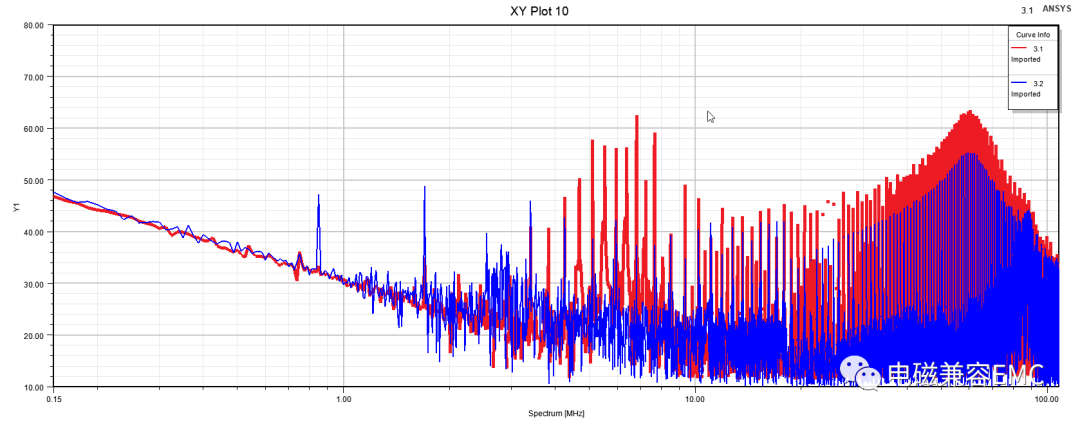

将3.1和3.2中Scheme 4的电容参数作为对比,分别带入系统电路中,得到的传导结果如下,从中可以看出,3.2节中的电容方案在3MHz以上的高频部分具有较低的EMI传导噪声,而低于3MHz的部分,其噪声幅值是高于3.1节中的电容方案的。

图32、两种电容方案在系统电路中得到的传导结果

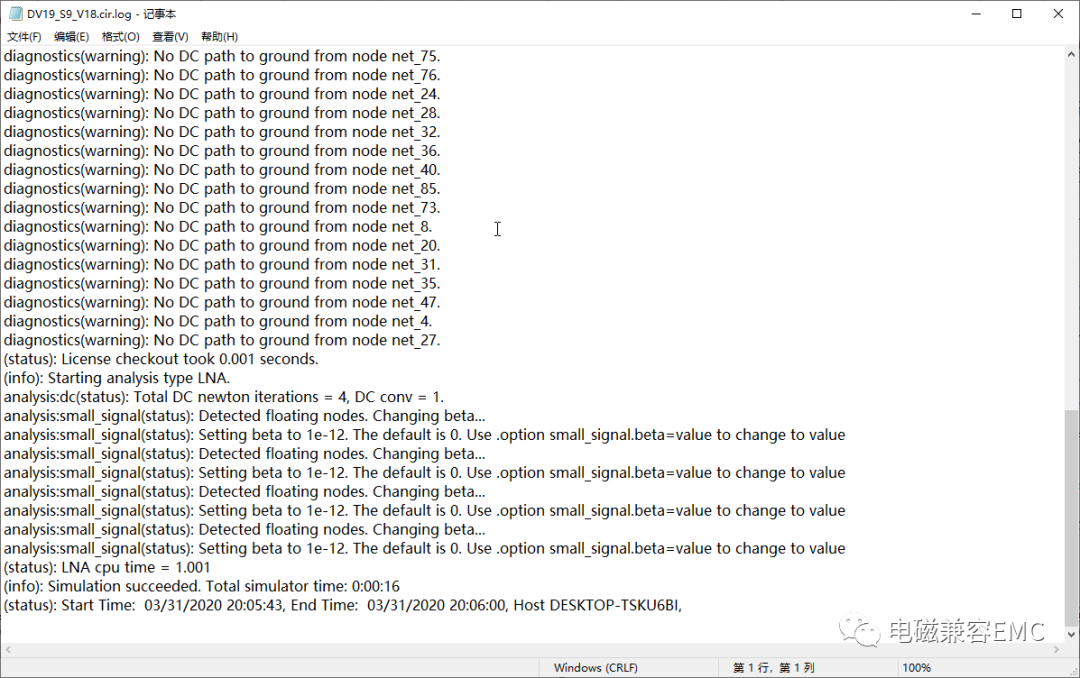

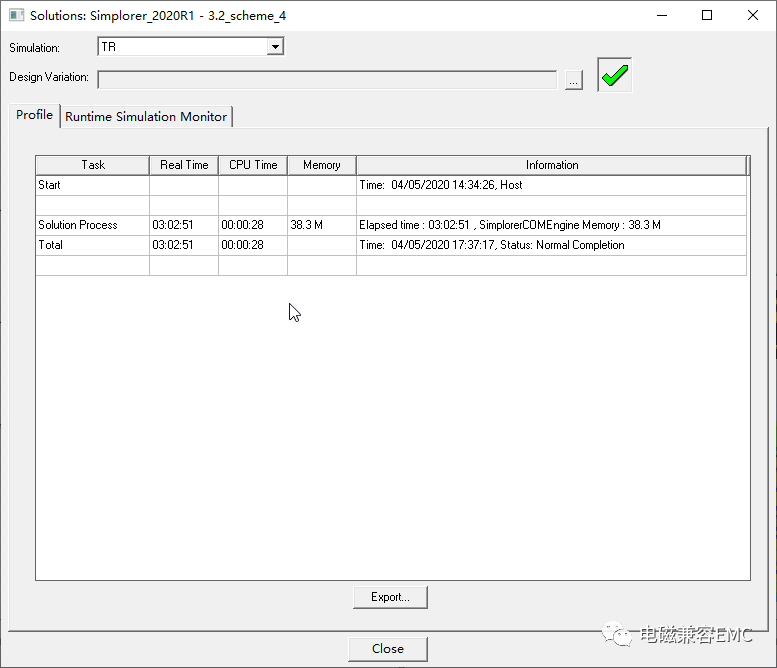

上图中4MHz~10MHz部分,3.2节方案的结果是明显低于3.1节对应方案的,这与图32中的S参数结果是对应的。两者分别采用了ANSYS designer和simplorer求解,采用designer求解所需时间为16秒,而采用simplorer求解所需时间为3个小时,对于需要优化滤波电路参数的工作来讲,采用designer无疑是最快速的。

图33、Designer仿真记录

图34、Simplorer仿真记录

3.4、调整布局继续优化

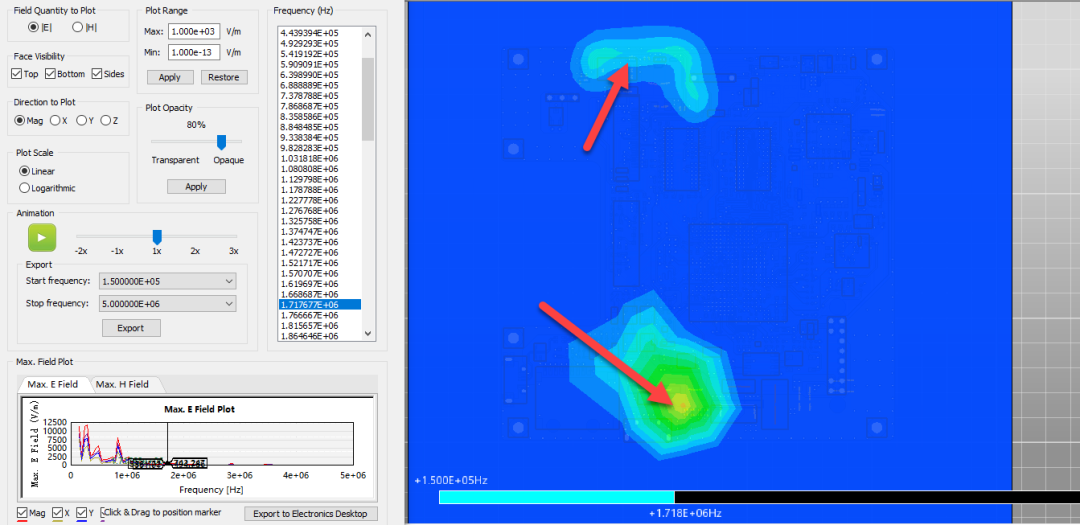

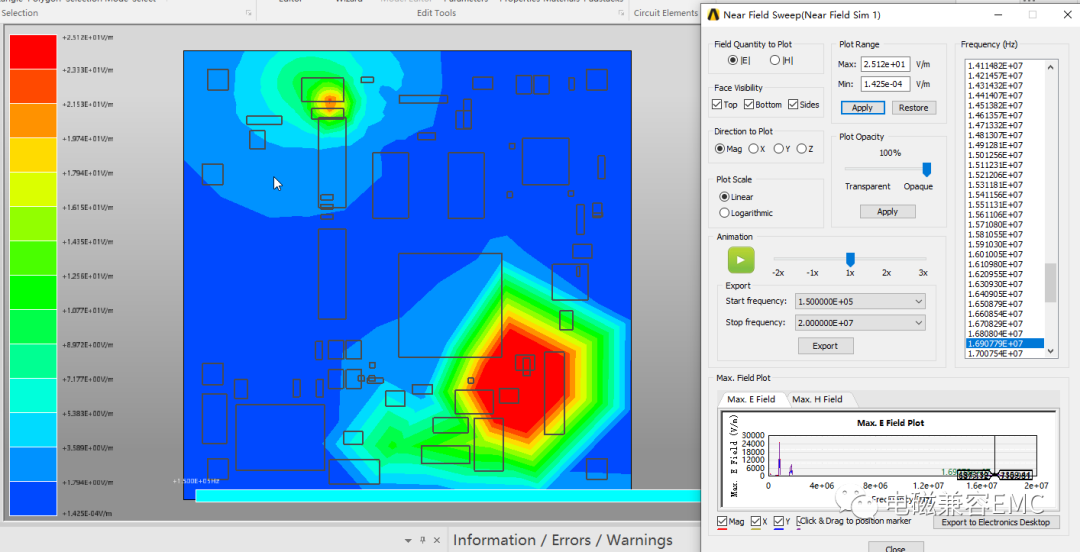

根据3.3节simplorer仿真结果,将其作为激励源导入siwave中,进行近场仿真,获取低频噪声对应的电场分布如下,可以看到1.7MHz频率对应的近场噪声主要分布在L2和U3位置的12V网络,传导噪声分布主要在TOP层。

图35、1.7MHz传导噪声的近场分布

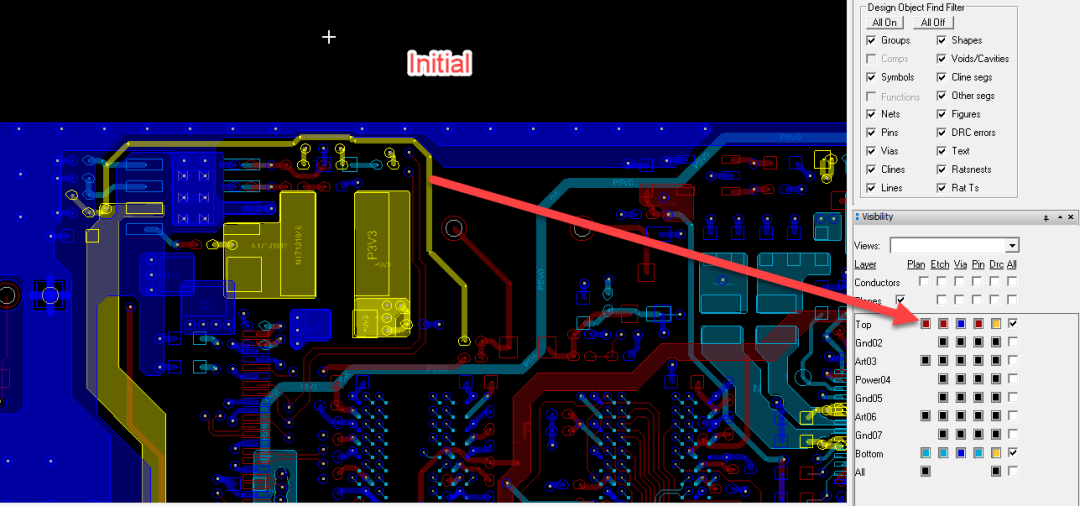

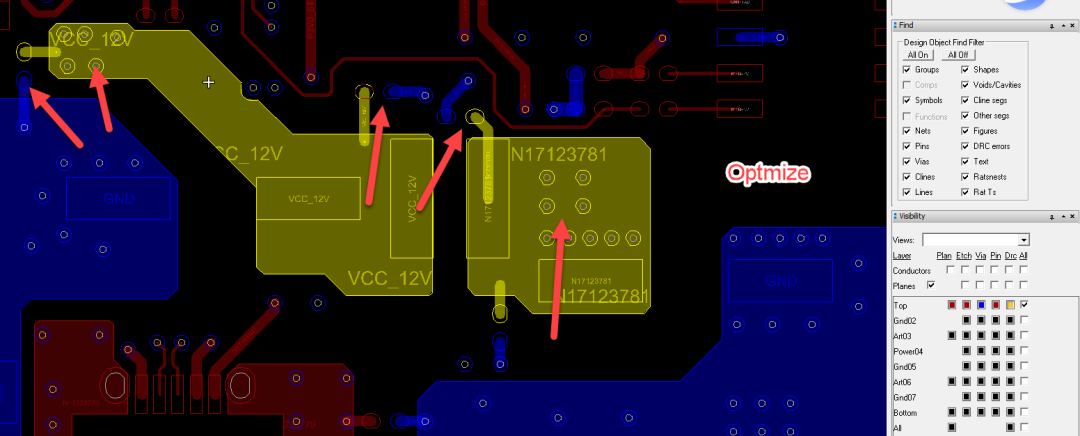

检查PCB布局,36-(a)可以明显发现,初始状态下12V网络在Top层走包围U3区域,(U3和P3V3在底层),由于边缘效应,以及接近输出在表层的FB信号部分走线,会耦合部分传导噪声,因此将其迁移到第二层,远离板边及其他敏感电源网络。36-(c)可以发现,硬件工程师将C1储能电容放在了L2之前,这是极其错误的做法,而且C1和C4两颗电容均远离U3,这都会增加U3从C1取电的阻抗。因为有D1防反二极管存在,后面可将D1修改为L1进行尝试。另一个问题在于L1周边的电容过于集中,所以将其分散开来,同时增加电源网络过孔数量,在尽量不修改布局的前提下进行优化处理。

(a)

(b)

(c)

(d)

图36、PCB优化前后

(a)(b)优化前;(c)(d)优化后

以上面PCB优化为基础,导入初始状态下的电容参数进行PI电源网络阻抗优化,从优化结果中得到下面两个低频较好的方案,选择方案5作为电容组合。

图37、去耦电容优化

表3、电容组合参数

| 电容代号 | C1 | C2 | C3 | C4 | C5 | C6 | C12 | C13 |

| 容值 | 22uF | 22uF | 12nF | 47uF | 22uf | 2.2nf | 22uF | 1uF |

| ESR | 3mΩ | 3mΩ | 6mΩ | 2mΩ | 3mΩ | 135 mΩ | 3mΩ | 11mΩ |

| ESL | 0.4nH | 0.5nH | 0.345nH | 0.75nH | 0.5nH | 0.3nH | 0.4nH | 0.35nH |

| 封装 | 0805 | 0805 | 0805 | 1210 | 0805 | 0603 | 0805 | 0603 |

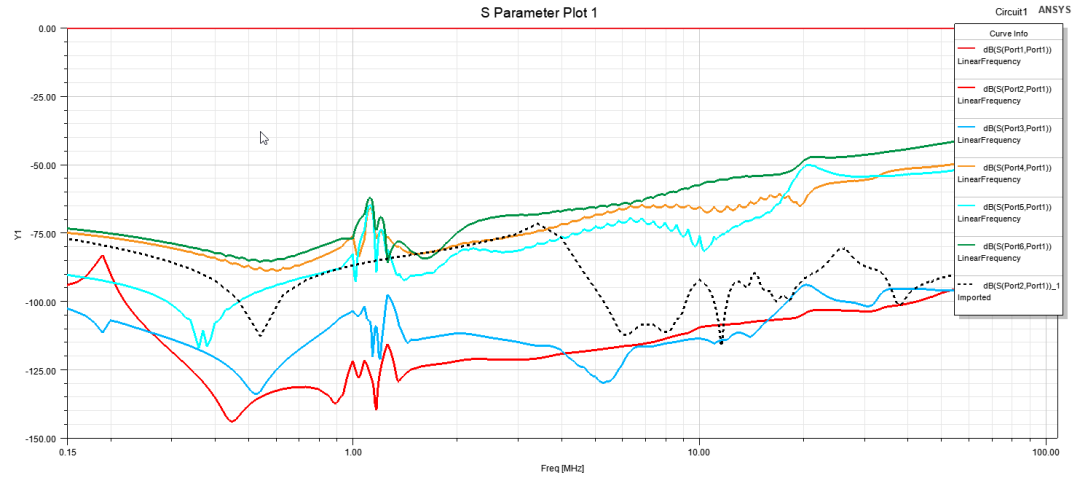

暂不考虑耐压等其他问题,将其直接导入Designer仿真S参数,同时考虑电感部分,得到的S参数如下,在不同位置放置端口查看观察不同位置的滤波效果,可以看到S21(连接器到电源芯片-蓝色线)并不是插损最低的曲线,最低位置在D1和L2之间。

图38、表3得到的S参数

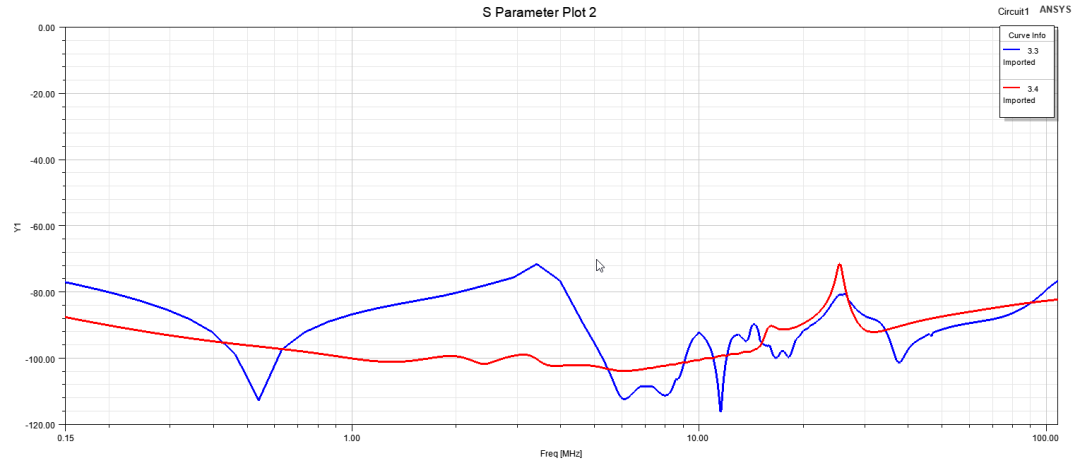

将3.3节的电容参数导入进来,对比布局调整后的变化,如下图所示,可以看到低频有所降低,布局的优化使滤波电路整体波动降低了,所以说即便是轻微的布局调整对电源滤波电路效果的影响也是巨大的。

图39、调整PCB布局前后后相同电容组合的S参数对比

根据designer中调整的情况,发现在调整L2到电源芯片之间的电容参数时,端口到电源芯片之间的S21结果变化不大,因此假设主要影响滤波电路性能参数的部分在于接口到L2之间,笔者在共模电感两侧和防反二极管位置增加X电容后发现,确实有明显改善。由于PCB布局的不合理,重新布局会严重增加笔者的工作量,加上笔者个人水平有限(想偷个懒^_^!)优化部分到此为止。结果中的部分电容和电感对电源传导噪声并无有效滤波效果,所以我们可以尝试将部分电容去掉Cutdown部分

图40、优化后的S参数(黑色虚线优化前;红色为优化后)

表4、最终电容参数

| 电容代号 | C1、C4 | C2 | C3 | C5 | C6 | C12 | C13 |

| 容值 | 100uF | 0.33uF | 47uF | 4.7nF | 1uF | 22uF | 1uF |

| ESR | 46mΩ | 12mΩ | 20mΩ | 120mΩ | 8.5mΩ | 3mΩ | 11mΩ |

| ESL | 0.28nH | 0.43nH | 0.4nH | 0.3nH | 0.61nH | 0.4nH | 0.35nH |

| 电容代号 | C01 | C02 | C03 | C04 | C05 | C06 | C07 | C08 |

| 容值 | 4.7uF | 4.7uF | 0.22uF | 2.2nF | 4.7nF | 15nF | 2.2uF | 4.7uF |

| ESR | 6.8mΩ | 6.2mΩ | 6.5mΩ | 180mΩ | 130mΩ | 57mΩ | 8.2mΩ | 6.3mΩ |

| ESL | 0.33nH | 0.37nH | 0.15nH | 0.45nH | 0.3nH | 0.5nH | 0.32nH | 0.55nH |

将得到的优化结果导入Simplorer进行系统电路仿真,得到的传导结果如下,可以看到,除15MHz位置以外的整个传导噪声幅值均有下降,作为汽车电子产品,该频段结果不做考察,所以这样的结果勉强可以接受,对笔者来讲纯粹是为了偷懒,所以没有继续对电感部分进行优化。如果项目经理对产品的成本或者结构需求做出调整,那时我们就需要考虑每个EMI器件的必要性以及产品PCB布局的优化方向,当然这些需求都可以采用EDA工具进行快速的模拟。

图41、优化前后的传导电压噪声(蓝色)

3.5、可做的其他工作

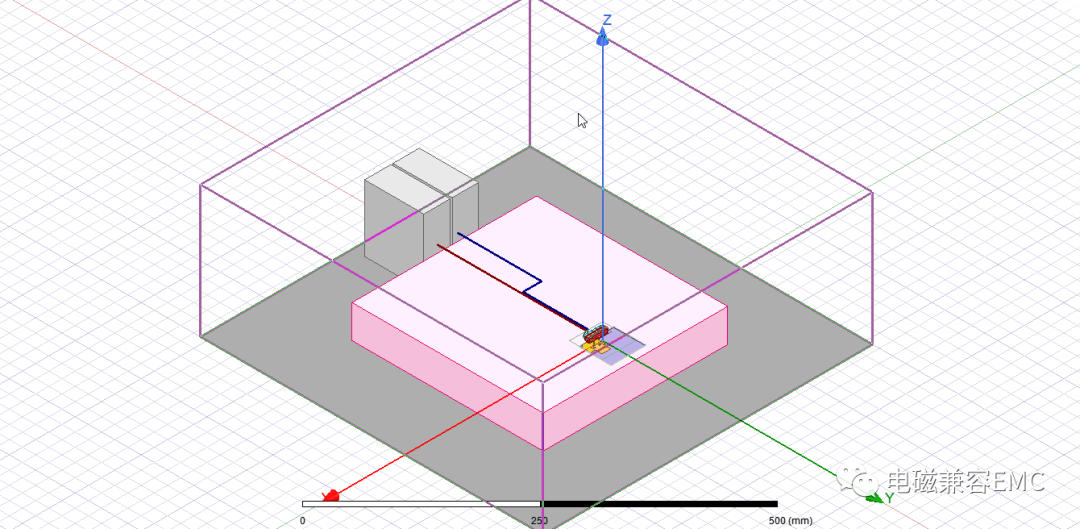

本次仅采用PCB文件对电源部分传导噪声进行仿真,对于需要考虑金属外壳、散热片以及复杂的外接线束所带入的影响,需要采用Q3D或者HFSS进行三维准静态/全波参数的提取,采用SIwave/HFSS与simplorer或者Designer的联合仿真,在仿真结束后可以通过Push Excitations将电路仿真结果作为激励源导入SIwave或者HFSS中,进行近场和远场辐射仿真,以便使用者快速定位噪声泄露途径,优化PCB和结构布局,由于篇幅有限,这里仅贴个图进行简单描述,其余部分不再赘述。

图42、符合CISPR 25标准要求的三维全波仿真

图43、PCB的近场辐射

4、结语

系统电磁兼容的仿真,需要使用者同时掌握较多的软件模块,同时需要对系统关键环路响应状态进行数字建模,在前期基于诸多测试数据的基础上,不断修正仿真中使用到的器件参数和系统仿真模块参数,然后使用ANSYS 3D component将其封装成可重复使用的器件库,利用不断的测试-仿真数据迭代,推进产品逐步走向正向设计。

-

开关电源传导EMI预测方法2023-09-22 846

-

PID回路控制及闭环控制原理2023-05-17 9490

-

PLC的PID控制怎么实现闭环控制呢?2023-03-30 4874

-

开关电源升压电路的闭环控制及其稳定性2023-02-28 2766

-

怎样去设计基于单片机控制的数控开关电源2021-10-28 1702

-

采用了PID控制器的闭环控制策略2021-08-23 1418

-

基于双闭环模糊PID控制器的开关电源控制的设计2018-10-08 2532

-

基于Matlab的闭环控制开关电源研究2018-05-29 1503

-

直流开关电源设计2016-04-19 1835

-

基于PID的电机闭环控制浅析2016-01-28 11512

-

开关电源的PSPICE仿真分析2010-10-04 2204

-

双闭环控制稳流型开关电源的建模与仿真2010-01-20 1016

-

基于UC3875的双闭环控制稳流型开关电源2010-01-11 1699

-

基于DSP芯片的开关电源的改进PID设计2009-12-19 638

全部0条评论

快来发表一下你的评论吧 !