ROMRAMFlash的一些零碎知识点

描述

这一篇主要讲讲ROMRAMFlash的一些零碎知识点,网上也能找到很多资料。

1、ROM1.1 概述只读存储器(Read-only memory, ROM),当然从广义上来讲,也有一些器件,例如Flash,EPROM等等,通过某种手段可以编程的,也属于ROM的范畴的。ROM一般用在一些程序的存储和数据的存储,这里程序多半是比较固定的程序(Firmware,固件,一种跟硬件强相关的程序,例如驱动等等),这里的数据多半是固化的表项,查找表等等不会怎么改变的表项。1.2 基本原理HDL设计中,对于小ROM,深度和位宽都不大,一般使用组合逻辑就可以做一个ROM。如果数据比较大,比如1K*4B这种,就换一种ROM,使用标准单元Mask ROM,来做存储,如下图所示。百度百科对MASK ROM的定义,是制造商为了要大量生产,事先制作一颗有原始数据的ROM或EPROM当作样本,然后再大量生产与样本一样的 ROM,这一种做为大量生产的ROM样本就是MASK ROM,而烧录在MASK ROM中的资料永远无法做修改。

1.3 分类

一种是真的写了就没法改的ROM;一种是可以写一次的ROM(one-time Programmable read-only memory),使用的高压反熔丝技术;一种是可擦出的能、能写多次的ROM(Erasable programmable read only memory),使用紫外线擦除;一种是电擦除的EEPROM(Electrically Erasable programmable read only memory,EEPROM),再到后来东芝搞的Flash。工业界第一种ROM和最后一种的Flash用的比较多。

二、Flash1.1 原理非遗失性的存储,是在ROM的基础上演进出来的。目前主流是NAND和NOR。模拟的团队来做flash。可以任意地址访问。对于连续地址读访问,NAND和NOR的带宽差距不大。NAND是存储块访问,NOR可以Byte访问。总的来说,NOR特点就是比较细的访问,基本启动程序放NOR中,稳定性和可靠性也稍微高一些;NAND访问数据块比较好,通常数据放NAND中,而且成本也较低。

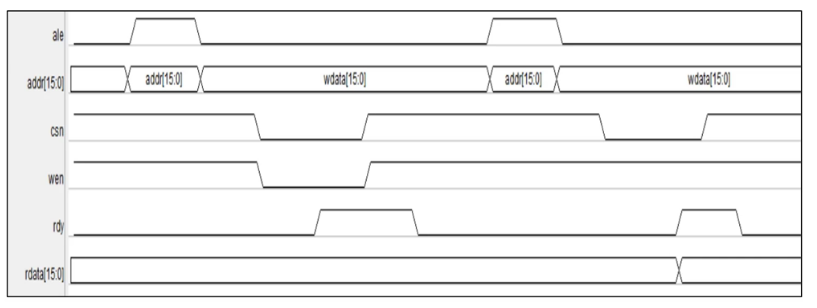

图:NOR Flash的时序

ale: address lock enable;一般Flash不会直接集成到芯片中,如果集成在芯片外面,IO数量增加,NOR解决办法就是数据和地址复用,当ale为高的时候,addr上走的是地址,当ale为低且csn为低的时候,addr上走的是数据。 wen:write enable;用于指示读还是写。 rdy:对于芯片和FLash分离,因为是异步接口,所以使用rdy信号用来握手。对于MCU来讲,如果把小的NOR flash集成到芯片内部,就可以直接使用同步接口,也就是SRAM的接口。

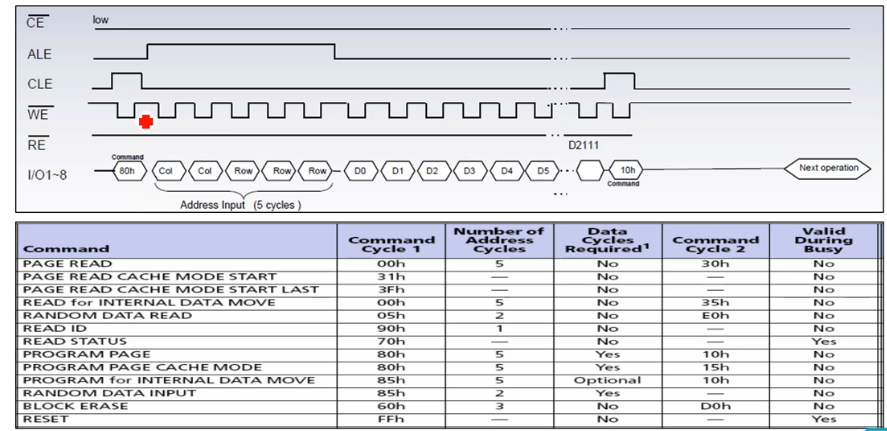

图:NAND Flash时序

CLE:Chip Lock Enable;

可以看到NAND也是数据和地址线复用的。NAND可以大块的数据读写,多了些Command。NAND Flash在MCU中的比较少。Flash跟ROM和RAM不同,不想数字的可以直接用工具生成,这个需要模拟团队自己做。

3、RAM 1.1 基本概念Static Random Access Memory,静态的,随机的访问。静态的,不用刷新,不像DRAM需要随时刷新,但是SRAM没有DRAM的集成度高,面积比较大。另外,速度和功耗比DRAM好一些。

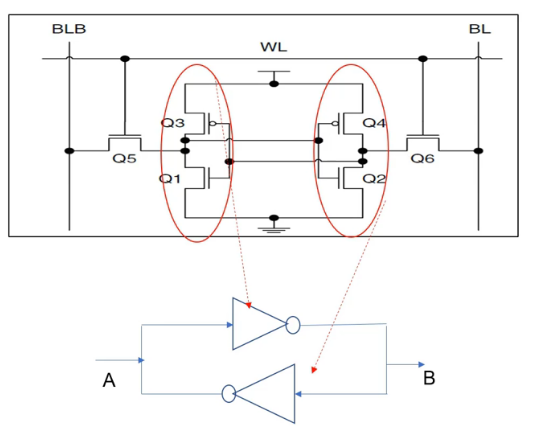

图:存储一个bit的SRAM的结构

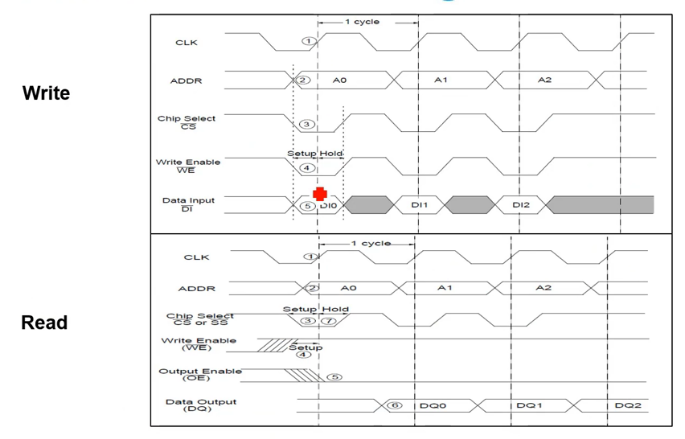

6个CMOS管子组成一个SRAM单元,Q1和Q3组成反相器,Q2和Q4组成反相器,两个反相器组成一个环路,这样,只要不掉电,这个逻辑环就不会变,跟触发器原理有点类似。Q5用于控制输入,Q6用于控制输出,两个管子相当于输入和输出的开关。1.2 分类single port SRAM:不会发生读写冲突,因为之后一个端口,要么读,要么写;尽量做到先写后读,或者初始化再读,否则读出来的数据有可能不对(原因是SRAM的软失效)。对于软失效,可以加一个ECC校验,例如寸10bir,其中2bit是校验位。 Two port SRAM:FOGA的读写冲突允许,但是ASIC不可以,在同一个时刻,读地址和写地址不要一样。FIFO一般是TP SRAM。 Dual port SRAM:也是两个端口A、B,可以A读B写,也可以A写B读,不在局限于只能谁读谁写。可靠性,面积和率都不是很好。 工程上,使用两个SRAM,做乒乓操作,实现TP SRAM的功能,一个读的时候,另外一个写。两个SRAM加起来面积可能比TP SRAM小一些。对于几百几K的bit位,直接用D触发器来存储比较好。1.3 接口SRAM有一个需要注意下,就是Redundancy接口,用于扩展SRAM的,在比较的大的memory中会用,例如cache,这个接口可选的。用法的话,举个例子这个就是说,当SRAM中有一块坏掉了,这个时候就在尾部在接一块SRAM存储,就把坏块的地址映射到新加的存储块中,这个时候就要用的Redundancy了。1.4 时序对于Single port SDRAM的时序,如下图:

读是在一个时钟周期完成,如果是连续写,红点处,write enable是可以一直拉低的;读的话,是要在下一个时刻才能采到数据,注意下。

-

解说、电子元器件汽车目的零碎集成2012-12-15 1477

-

在学习STM32的过程中积累的一些知识点2013-10-04 2782

-

请问学习LLC电源需要掌握一些什么知识点2019-03-05 2298

-

记录一些飞控开发过程的知识点2021-08-09 1160

-

讲讲ROM、RAM、Flash的一些零碎知识点2021-11-03 1968

-

嵌入式开发过程中遇到的知识点记录2021-12-14 1171

-

关于红外通信的一些问题知识点2016-05-05 1068

-

单片机的通信数据传输一些知识点资料说明2019-06-04 1062

-

DSP入门学习必看的一些知识点详细概述2019-11-01 1818

-

机智云入门知识点2021-12-07 825

-

Verilog设计过程中的一些经验与知识点2022-03-15 3232

-

一些小众的C语言知识点2022-09-26 1157

-

单片机开发零基础可不行,还需掌握这些知识点2023-02-17 3049

-

介绍一些基础的电力知识点2023-08-15 2608

全部0条评论

快来发表一下你的评论吧 !