EDA工具分为哪几个模块

EDA/IC设计

描述

一设计输入编辑器

通常专业的EDA工具供应商或各可编程逻辑器件厂商都提供EDA开发工具,在这些EDA开发工具中都含有设计输入编辑器,如Xilinx公司的Foundation、Altera公司的MAX+plusII和QuartusII等。

一般的设计输入编辑器都支持图形输入和HDL文本输入。图形输入通常包括原理图输入、状态图输入和波形图输入三种常用方法。原理图输入方式沿用传统的数字系统设计方式,即根据设计电路的功能和控制条件,画出设计的原理图或状态图或波形图,然后在设计输入编辑器的支持下,将这些图形输入到计算机中,形成图形文件。

二仿真器

在EDA技术中,仿真的地位非常重要,行为模型的表达、电子系统的建模、逻辑电路的验证以及门级系统的测试,每一步都离不开仿真器的模拟检测。在EDA发展的初期,快速地进行电路逻辑仿真是当时的核心问题,即使在现在,各个环节的仿真仍然是整个EDA设计流程中最重要、最耗时的一个步骤。因此,仿真器的仿真速度、仿真的准确性和易用性成为衡量仿真器的重要指标。

几乎每个EDA厂商都提供基于Verilog/VHDL的仿真器。常用的仿真器有ModelTechnology公司的Modelsim,Cadence公司的Verilog-XL和NC-Sim,Aldec公司的ActiveHDL,Synopsys公司的VCS等。

三HDL综合器

硬件描述语言诞生的初衷是用于设计逻辑电路的建模和仿真,但直到Synoposys公司推出了HDL综合器后,才使HDL直接用于电路设计。

HDL综合器是一种将硬件描述语言转化为硬件电路的重要工具软件,在使用EDA技术实施电路设计中,HDL综合器完成电路化简、算法优化、硬件结构细化等操作。HDL综合器在把可综合的HDL(VHDL或VerilogHDL)转化为硬件电路时,一般要经过两个步骤:第一步,HDL综合器对VHDL或VerilogHDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程;第二步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径等。

HDL综合器的输出文件一般是网表文件,是一种用于电路设计数据交换和交流的工业标准化格式的文件,或是直接用硬件描述语言HDL表达的标准格式的网表文件,或是对应FPGA/CPLD器件厂商的网表文件。

HDL综合器是EDA设计流程中的一个独立的设计步骤,它往往被其他EDA环节调用,完成整个设计流程。

电路网表(逻辑图)由元件名N、模型M、输入端信号PI、输出端信号PO四部分组成,是唯一确定电路连接关系的数据结构。即:E=(N,M,PI,PO)

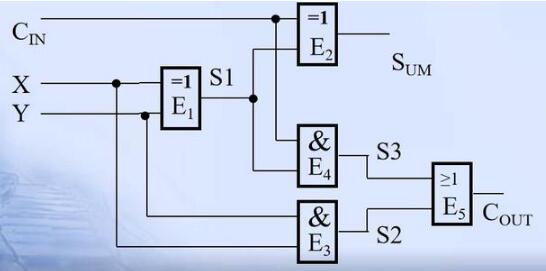

例:一位全加器的电路网表

E1,XOR,(X,Y),S1

E2,XOR,(Cin,S1),Sum

E3,AND,(X,Y),S2

E4,AND,(S1,Cin),S3

E5,OR,(S2,S3),Cout

-

LED封装的具体制造流程分为哪几个步骤?2021-05-11 2769

-

如何去安装Pads VX.2软件?主要分为哪几个部分?2021-06-30 2906

-

航模无刷电机大概分为哪几个系列?2021-07-21 2899

-

嵌入式总共分为哪几个主流方向?2021-09-24 2730

-

STM32的闪存模块是由哪几个部分组成的2021-10-15 1923

-

Centos6的引导过程分为哪几个阶段呢2021-10-19 1650

-

IC的设计过程可分为哪几个部分2021-10-20 2273

-

C语言的开发过程可分为哪几个步骤呢2021-11-02 2528

-

STM32程序的编译分为哪几个步骤?2021-11-26 2337

-

BootLoader启动过程分为哪几个阶段呢2021-11-30 2387

-

stm32f103串口通讯可以分为哪几个步骤呢2021-12-13 1836

-

串口通信的硬件设计可以分为哪几个部分呢2021-12-14 2009

-

rk3288的uboot启动分为哪几个过程呢2022-03-04 2182

-

示波器的组成--示波器由哪几个部分组成的?2009-02-10 5623

-

电动车充电分为哪几个过程2018-03-26 32831

全部0条评论

快来发表一下你的评论吧 !