基于DDR DRAM控制器实现MPMA存取输入/输出端口的设计

存储技术

描述

为了兼具可扩展性和数据处理速度,对于各种应用,如图像数据侦错、视频数据压缩、音频数据增益、马达控制等,可编程数据处理模块(Programmable Data Processing Module)是时势所需。

在处理的数据量越来越大的情况下,所需的内存容量随之增大,以往的先进先出队列(First-In-First-Out, FIFO)无法满足其高速度与大容量的需求,许多硬件工程师开始考虑使用DRAM的可能性。

DRAM具备可快速存取、可依照设计者规划使用空间、大容量等优点,但是内存数组需要重新充电,而双倍数据速率同步动态随机存取内存( DDR SDRAM)有数据相位同步等不易控制的问题,不如FIFO使用方便。因此,在使用FPGA进行设计时,搭配其供货商所提供的RAM控制IP,再加上硬件工程师所开发的控制逻辑,是当前数据控制存取的发展趋势。

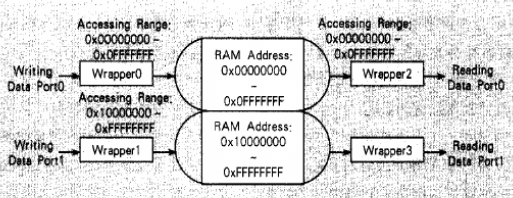

本文的构想是在此DRAM控制IP上增加一层包装(Wrapper),使之拥有FIFO接口,具有多端口内存存取控制(MPMA: Multi-Port Memory Access)功能。既可以保持大容量、存取速度快等优点,也可增添FIFO接口容易的优点。在设计过程中,DRAM空间可随设计师的定义而拥有更高的弹性。如图1所示,此DRAM拥有两个写入端口和两个读出端口。对于每个写入端口,其数据可以从起始地址连续写入,直到结束地址之后,再从起始地址继续写入,形成循环式(Circular)写入方式。对于每个读出端口,其数据的读出可使用类似于循环写入的方式,而且只要写入到内存的数据数量比读出的数据数量多,即是合理的类FIFO存取方式。

图1 有两个写端口和两个读端口的DRAM控制槽

MPMA如何应用于数据处理模块

在许多需要对大量信息进行运算处理的应用中,需要极大的缓存,与一个4KB FIFO的价格相比,买一个32Mb的DRAM更合适些。不过,其复杂的存取控制是一大问题。所以在编写FPGA的HDL算法时,可利用FPGA供货商所提供的IP构成解决方案。

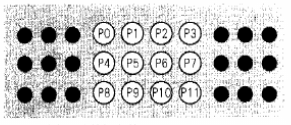

对于所需处理的数据量重复性较高的应用,例如图2所示的图像原始数据用图像侦错处理算法来侦测P4点是否错误,需要将它周围的8个点当作参考数据来对比,若使用FIFO,可能无法同时存取到此三条线(Line)的数据,所以使用DRAM存取大量的数据。

图2 图像原始数据点数组

由于DRAM的控制方式比较复杂,每存取一次就要重新计算其欲存取的数据地址,根据其数据地址的连续性,可在图像原始数据写入后,分为三个端口以连续地址的方式读出。如图2所示,第一端口连续读出P0、P1、P2,第二端口连续读出P4、P5、P6,第三端口连续读出P8、P9、P10,则可以完成P5点侦错的计算;而在计算P6点是否出错时,第一端口只要再读出P3,第二端口读出P7,第三端口读出P11,就可以完成计算前数据的完备,大大提高了数据的使用率,采用连续读取的机制,不用在每次计算前计算数据地址,只要每一端口均先连续读取数据即可完成,也降低了DRAM控制的复杂度。

MPMA的实现

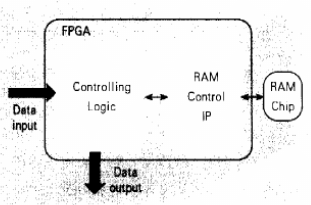

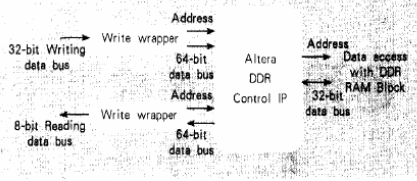

下面以Altera MegaCore IP Generator产生的DDR DRAM控制器为例,再加上自创的Wrapper逻辑,构建一进(32位进)一出(8位出)的MPMA存取端口,图3为其方块架构图。

图3 一进一出的MPMA存取端口

在此架构中,Altera DDR DRAM 控制与写/读wrapper间的数据带宽为64位,而通过wrapper逻辑,更可自由地编写输入与输出带宽。在写/读wrapper中,数据的地址计算采用累进式累加方式,其存取接口类似于FIFO的存取,因而更容易实现大容量数据的存取。

每个wrapper中有一个小容量的FIFO、封装(packing)/反封装(un-packing)机制以及地址累进计数器。FIFO用于调节使用者接口与DRAM频域的差异;封装/反封装机制用于将输入/输出接口数据总线宽度调整至与DRAM控制IP接口相同的水平,以利于提高写入/读出DRAM数据的效率。地址累进计数器是每个wrapper的DRAM地址产生器,只要写入wrapper里的计数器数字大于读出wrapper里的计数器,则所读出的必为先前已经写入DRAM里的合法数据,不会存取到错误地址的数据。

MPMA提高效率

以图2的点P5为例,若不使用wrapper,则此点数据会被写入1次,而在运算的时候被读出1(当作主要运算点)+8(当作参考数据点)次。当一幅有n点数据的图像需要做侦错处理时,则需要n*(1+1+8)次的数据存取,还不包括地址计算所造成的延迟。

当使用一进三出的MPMA wrapper时,P5点只需要被写入1次,而在运算的时候被读出3(3个读wrapper各需要读取1次)次,则同样的n点数据作完侦错处理只需要n*(1+3)次的数据存取,并且采用累进式的DRAM地址计算,不需要花费额外的延迟时间。由此可知,MPMA设计可提高2倍以上的数据存取效率。

结语

本文提出一种架构,在FPGA供货商所提供的IP核上添加写入/读出wrapper,具有数据的高度重复使用率与容易操作的类FIFO接口等优点。设计师更可自行定义MPMA wrapper输入/输出端口的个数与数据总线宽度,以提高数据使用率。

凌华科技已将此技术应用于大数据量的图像采集/处理/传输模块,尤其是线阵扫描(Line-Scan)图像采集系统,因为在检测时,需要在FPGA上执行图像数据计算的算法,一方面需要大容量的图像数据缓存,另一方面需要反复读取图像数据,则此技术是必需的。

责任编辑:gt

-

DRAM动态随机存取存储器DDR2 SDRAM内存解决方案2026-02-28 702

-

PLC输入端口和输出端口的工作原理2024-06-19 8078

-

端口的输入与输出2023-03-02 4232

-

基于FPGA的DDR3SDRAM控制器设计及实现简介2021-07-30 982

-

求一种DRAM控制器的设计方案2021-04-28 1659

-

DDR SDRAM控制器的设计与实现2021-03-28 1228

-

带OPB中央DMA的MCH OPB DDR SDRAM控制器系统的详细说明2019-09-12 1605

-

pid控制器的输入输出_PID控制器的控制实现2018-06-01 31783

-

PIC32 FRM之DDR SDRAM 控制器的详细说明文档资料2018-05-30 1973

-

利用DDR控制器读取重排序缓冲器,将DRAM带宽提高十倍2017-11-18 3596

-

基于VHDL的DRAM控制器设计2012-02-02 1952

-

ADI推出通用输入/输出端口扩展器和键盘矩阵控制器ADP5585和ADP55892011-09-14 3126

-

DDR2 SDRAM控制器的设计与实现2010-02-09 878

全部0条评论

快来发表一下你的评论吧 !