基于DDS技术和标准CPCI总线实现中频信号源的设计

电源/新能源

描述

引言

DDS在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等方面都远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。利用DDS技术可以很方便地实现多种信号。本设计的核心部分正是基于DDS技术,进行所需中频信号源的设计。

硬件电路的设计

该中频信号源的设计基于标准CPCI总线,上位机通过改写板上的控制参数可以很方便地输出不同形式的波形。硬件系统的结构如图1所示。它包括三个模块:A是系统的核心部分,为中频信号产生模块; B是中频正交检波模块,输出检波后的I、Q信号;C为中频正交调制模块,可以输出带有包络的中频调制信号。下面将详细讨论各个模块的具体实现和功能。

信号源产生模块

该模块主要包括PCI总线接口、信号产生控制逻辑电路(FPGA)、DDS芯片以及相应的放大、滤波和衰减电路。上位机通过PCI总线访问FPGA中的寄存器,实现对各种工作模式的控制。其中FPGA选用的是Altera公司的EP1K50TC144。晶振除了提供板上各个模块工作所需时钟外,还提供给其他处理板作为外时钟。设计中采用的DDS是AD9854,片内的4~20倍的时钟乘法器可使内部工作频率达到300MHz,输出信号的频率可达100MHz。

DDS的各种参数控制信号均由FPGA来提供,实现不同形式信号的输出。DDS1输出的chirp(线性调频)信号经过放大滤波后送入数控衰减器,然后进行波束调制,调制后的信号ROUT从前面板输出。DDS2输出的连续波信号经放大滤波后再经过两级功分器输出三个信号F1_out、F2_out和 F3_out,作为正交调制和检波模块的本振信号,通过板内的SMA与相应的模块连接。

正交检波模块

如图1中阴影部分所示,包括两路正交检波电路。被检波的中频信号RF1(RF2)由前面板送到板内,经过运放后输入正交检波器,本振信号由板内的SMA引入,即F1_in和F2_in,由模块A中功分器的输出F1_out和F2_out提供。经过正交检波器后输出I、Q信号,分别经滤波放大后输出,即得到需要的信号。

正交调制模块

该模块完成中频上的正交调制功能。本振信号通过板内的SMA送给正交调制模块,经放大后送给正交调制器,I、Q信号从前面板直接送给正交调制器,调制后的信号经放大滤波后送给功分器,输出两路中频信号。中频信号的幅度由压控衰减器的衰减控制量来控制,实现相应的信号包络调制。压控衰减器的控制量(图1中的Con1和Con2)由前面板输入。

中频信号源在某雷达干扰系统中的应用

中频信号源可以为雷达干扰实验系统提供所需的雷达信号,以及完成对信号的中频正交检波与调制。

中频信号源在雷达模拟器和回波模拟器中的应用

在雷达模拟器和回波模拟器中共用一块中频信号源板,具体应用如下:

模块A:产生雷达定时信号,如雷达重复周期PRT、组领脉冲CPI以及雷达发射信号R_OUT和外时钟CLK,同时给正交调制模块及检波模块提供本振信号。这里的R_OUT就是上文提到的送往雷达干扰机模拟器的雷达发射信号。其具体实现过程为:上位机通过PCI总线访问板上FPGA芯片中的控制寄存器,控制雷达模拟器的各种参数,如PRT的变化方式以及R_OUT的输出形式等。不同模式参数的具体实现由FPGA来完成。FPGA除了产生上述的PRT、CPI等信号外,还要产生DDS的读写及控制信号,来控制DDS1和DDS2的输出。DDS1根据前端FPGA送出的控制字输出相应的雷达发射信号,有单点频模式、循环模式和随机捷变模式,信号的形式为脉冲线性调频信号,带宽为5MHz~20MHz可编程,脉宽10ms~50ms可编程,载频为40MHz~90MHz,具有捷变频的功能。DDS2输出的是正弦连续波信号,也具有捷变频的功能,捷变的方式与DDS1一致。DDS2产生的信号经过放大、滤波和功分电路后从板子内部的SMA输出,作为检波模块和本振模块的本振,从而保证雷达模拟器和回波模拟器的载频与雷达发射信号的一致性。

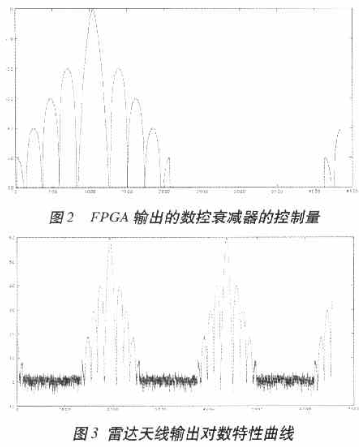

由DDS1输出的雷达信号经放大滤波后送给数控衰减器进行雷达天线扫描的调制,输出具有雷达天线包络的信号。数控衰减器的衰减范围为65dB,可控位数为12bit,最小步进0.5dB。图2所示为FPGA送给数控衰减器的控制量,系统要求干扰机接收信号的动态范围为60dB,因此衰减控制量的最大差值为60 dB。由于天线图的周期太长,为了便于观测,可以对输出的天线图进行A/D采样,采样后如图3所示。横坐标表示采样点,纵坐标为对幅值求对数后的量化值。该图即为天线的包络,读图可以知道天线主瓣与旁瓣的dB差值,主瓣与第四旁瓣的差值为50 dB。外时钟CLK信号是板内时钟经过时钟驱动芯片送往前面板的SMA头输出,可以提供给雷达模拟器处理板和回波模拟器处理板使用。

模块B:完成中频上的正交检波,对雷达回波中频信号和干扰中频信号合成后的信号进行检波,本振信号由DDS2的输出提供,即F1_out和F2_out,分别与F1_in和F2_in相连。该模块设计了两路是因为要对雷达分别进行主天线和辅助天线的处理。对DDS送来的主天线和辅助天线的合成信号分别进行正交检波,输出两路I、Q信号送给雷达模拟器。

模块C:对雷达回波模拟器产生的基带正交信号进行调制,调制到具有捷变功能的中频本振上,本振信号F3_in由DDS2经过功分器输出的F3_out提供,本振变化的规律与DDS1产生的雷达发射信号的变化一致。中频调制后的信号经过功分器分成两路,再经过压控振荡器,分别对两路信号进行天线调制,其中一路作为主天线回波信号,另一路作为辅助天线回波信号。压控衰减器的控制量由雷达回波模拟器经由前面板的Con1和Con2提供。

结语

本设计主要有以下几个特点:

1. 该系统采用DDS技术,可以满足高线性度、高稳定度、高信噪比和低杂散的要求。

2. 用上位机可以简单方便地控制信号波形参数,为不同频率、不同波形的要求提供了通用平台。

3. 能够在产生中频信号的同时,对信号进行任意包络的波束调制。

4. 该系统还能够完成正交检波和正交调制的功能。

5. 硬件结构简单,功能划分清晰,各模块可单独使用。

以上介绍了一种应用在某雷达干扰仿真系统中的中频信号源的设计与实现。只要改写FPGA中控制DDS的部分参数就可以根据要求改变信号的输出形式,简单方便,输出信号的各项指标均能达到很高的要求。

责任编辑:gt

-

基于FPGA和DDS的信号源设计2010-02-21 2176

-

基于DDS和FPGA技术的高动态扩频信号源的研究2012-08-17 3293

-

基于FPGA和DDS技术的扫频信号源设计2019-07-04 4382

-

基于FPGA的DDS信号源设计与实现2010-02-11 1003

-

GPS数字中频信号源一体化FPGA设计2010-07-28 485

-

一种基于DDS_AD9835的高压射频信号源的设计2010-12-23 1274

-

VXI总线专用中频信号源的设计2006-03-24 979

-

基于DSP和DDS的三维感应测井高频信号源实现2010-01-08 1278

-

多载波射频信号源技术2011-11-03 874

-

基于DDS技术的多路同步信号源的设计2016-05-27 9397

-

基于DDS的雷达中频信号源设计与实现2016-10-25 1001

-

基于DDS的信号源设计论文资料2017-07-19 1242

-

矢量信号源与射频信号源的区别?2018-01-08 35621

-

基于GPS中频信号源的FPGA设计实现方案2020-07-31 2499

-

矢量信号与射频信号源有何区别2020-10-30 3348

全部0条评论

快来发表一下你的评论吧 !