上拉电阻和下拉电阻的主要作用

描述

上拉电阻和下拉电阻的主要作用

1. 提高电压准位

当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS电路的最低高电平,这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;OC门电路必须加上拉电阻,以提高输出的高电平值。

2. 加大输出引脚的驱动能力

有的单片机引脚上也常使用上拉电阻。

3. N/A引脚(没有连接的引脚)防静电、防干扰

在CMOS芯片上,为了防止静电造成损坏,不用的引脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。同时引脚悬空就比较容易接收外界的电磁干扰。

4. 电阻匹配

抑制反射波干扰,长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻使电阻匹配,能有效的抑制反射波干扰。

5. 预设空间状态/默认电位

在一些CMOS输入端接上拉或下拉电阻是为了预设默认电位。当不用这些引脚时,这些输入端下拉接低电平或上拉接高电平。I2C等总线上空闲时的状态是由上下拉电阻获得的。

6. 提高芯片输入信号的噪声容限

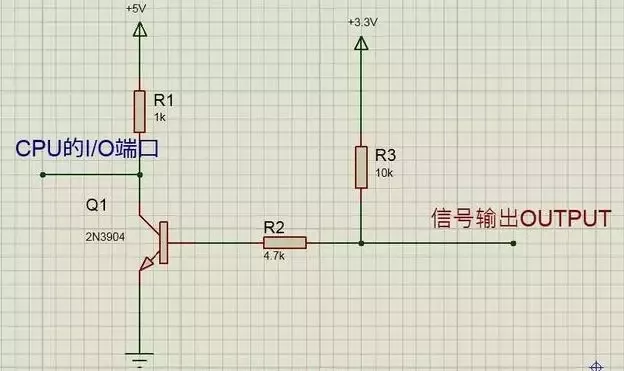

输入端如果是高阻状态,或高阻抗输入端处于悬空状态,此时需要加上拉或下拉电阻,以免受到随机电平的影响,进而影响电路工作。同样,如果输出端处于被动状态,需要加上拉或下拉电阻,如输出端仅仅是一个三极管的集电极,还可以提高芯片输入信号的噪声容限,增强抗干扰能力。 在BJT晶体三极管的基极端,上拉电阻和下拉电阻也起着至关重要的作用。在三极管的电路应用中,串接在基极上的电阻起限制基极电流的作用,如图1中的R2所示:

图1

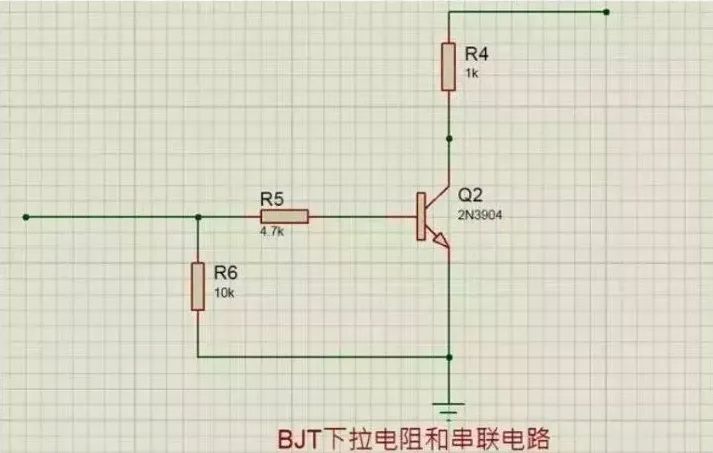

如图2中的R5所示,上拉电阻使三极管基极的输入电平在默认情况下是高电平输入,当CPU有低电平信号输出时,外围电路响应,下拉电阻使晶体管的基极输入在默认情况下拉到低电平,如图2中的R6所示。

图2

-

上拉电阻和下拉电阻的用处和区别2023-06-29 14660

-

上拉电阻与下拉电阻的作用2023-06-07 4623

-

电阻为什么要拉一下---上拉和下拉的作用?2023-05-31 4360

-

上拉电阻和下拉电阻的作用是什么?2023-05-26 4668

-

上拉电阻和下拉电阻作用、区别和应用2023-04-21 19527

-

上拉电阻和下拉电阻原理及作用2023-03-17 8209

-

上拉电阻与下拉电阻2022-01-14 1561

-

数字电路中的上拉电阻和下拉电阻分析2019-08-07 11747

-

电阻的上拉与下拉作用2018-06-28 3509

-

上拉电阻作用及原理2017-10-25 50232

-

上拉电阻和下拉电阻的作用及选择2016-12-15 1261

-

上拉电阻、下拉电阻、限流电阻的原理和作用2016-11-11 3480

-

什么是上拉电阻,什么是下拉电阻?它们的作用是什么?2009-06-28 112961

全部0条评论

快来发表一下你的评论吧 !