FPGA的多芯片封装技术介绍

可编程逻辑

描述

FPGA封装中的存储器一般是在高密度、高带宽、高带宽、高成本的技术中实现,比如HBM。由于我们是通过芯片外的方式来实现(通过互插器或EMIB或其他封装链路),所以延迟和带宽比嵌入式存储器要低,但比通过传统的存储器接口(我们稍后会讲到)在PCB上的芯片外实现要好。

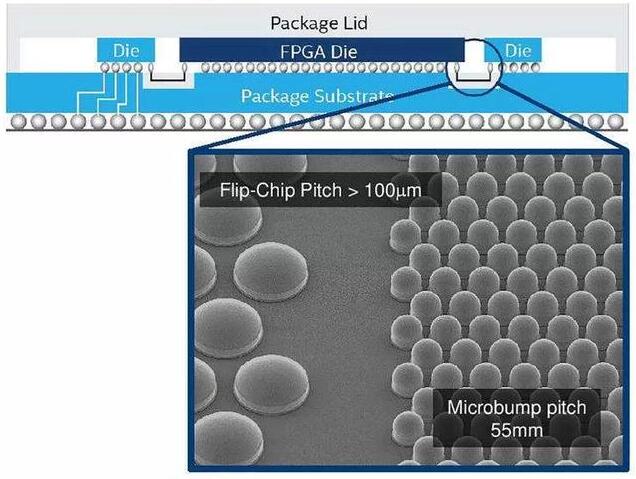

然而,在讨论封装内存储器之前,我们应该先谈谈三家厂商在封装层面的集成方式的根本区别。在这里,我们将以最小的终端用户投资获得英特尔Agilex的最大灵活性。英特尔的Agilex从一开始就为封装内集成的灵活性而设计。英特尔使用了一种名为EMIB(嵌入式多模互连桥)的专有技术来连接封装内的芯片组。FPGA结构本身是一个芯片组,SerDes收发器是另一个芯片组,封装内存储器(如HBM等)是另一个芯片组,还有其他可选的外设。这些外设都可以用不同的工艺技术来实现,这意味着英特尔可以随时更新或刷新任何芯片组,而无需重新设计整个FPGA(就像他们用单片机方法一样)。英特尔在这里的额外优势是他们能够基于最近获得的eASIC技术夹带定制芯片组。这意味着用户的定制逻辑可以添加到FPGA的封装中,只需最小的NRE和设计开销就可以实现。

Achronix已经宣布了Speedster7t作为一个独立的芯片系列,但也有一个Speedcore嵌入式FPGA版本,它包含了与Speedster7t相同的资源,但也可以包含自定义指令,以进一步优化特定类别的应用;这些可能是专用的数据包处理、TCAM或信号处理功能。在这种情况下,在芯片与封装之间的集成决定,以及在FPGA结构的同一块硅片中包含哪些硬化IP,完全由客户的设计团队决定。这种方法为最终用户提供了最大的灵活性和控制权,但对客户端的成本、风险和设计专业技术要求更高。

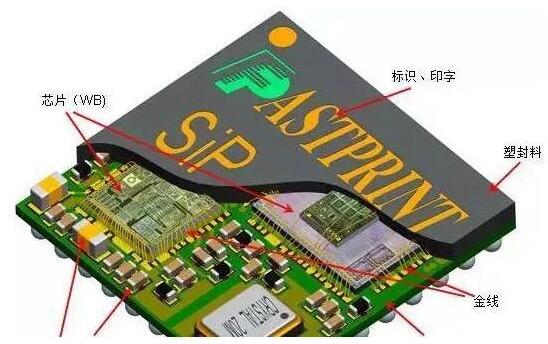

Achronix也从事Chiplet(芯粒)业务,并参与开放计算项目(OCP)的开放域专用架构(ODSA)计划。ODSA正在努力建立标准,以驱动开放的Chiplet(芯粒)生态系统,这将有助于创建混合并匹配来自多个供应商的小芯片的SiP。这将允许与英特尔类似的封装级定制,但不能使用英特尔专有的EMIB互连技术。Achronix的观点是,设计团队通常最初会使用独立的FPGA解决方案,一旦设计通过验证,便会进行降低成本的回合,其中可能包括将一些逻辑强化到也包含可编程FPGAIP模块的标准单元ASIC设计中,或者使用Chiplet(芯粒)构建自定义SiP。

Xilinx在这三种设备中提供最少的设备自定义灵活性,但迄今为止却提供了最多的“开箱即用”选项。赛灵思(Xilinx)是FPGA多管芯集成的先驱,它使用插入器将多个小芯片拼接在一起,形成了三代产品。有趣的是,Xilinx在其他人推动该战略的同时也放弃了该战略。Xilinx现在将其设备的更多功能构建到一个整体式芯片中。这带来了速度,成本和可靠性方面的优势,但降低了混合匹配Chiplet(芯粒)以定制封装内集成的能力。为此,Xilinx正在计划提供大量的Versal系列产品,以期提供具有适当资源集以匹配各种类型应用程序的现成设备。

说回内置内存,那么,据我们所知,Xilinx和Intel都提供了类似的内置HBM堆栈。Xilinx表示会有VersalHBM系列,但还没有正式公布具体的细节,但我们可以根据他们在其他系列的支持来推测。通过Agilex,英特尔提供了最大16GB的HBM2,以及其他类型的内存资源放入包内的能力。Achronix并没有提供内置内存选项,而是声称他们使用了8个GDDR6内存控制器,每个控制器可以支持512Gbps的带宽,给他们的设备提供了4Tbps的GDDR6带宽,这与其他厂商提供的HBM选项相当,但成本更低。与HBM相比,其代价是更多的功耗和PCB设计的复杂性。GDDR6的出现可能会更直接(考虑到图形子系统的目标市场),而HBM2还需要一些时间来实现量产。

寻找对板载内存的支持,所有供应商都支持DDR4,并将支持DDR5。

英特尔Agilex继续他们的方法,即提供带有加固的DDRx内存控制器(HMC,但不提供“混合内存立方体”)的加固的内存控制器。英特尔进入HMC已有多年历史,其历史可追溯至28纳米的AlteraArria5系列。英特尔表示,他们的FPGA集成式硬存储器控制器有助于在硬PHY中实现从内核到外围的紧密传输以及从外围到内核的时序传输,有效地保证了时序收敛并减少了编译时间,并减少了半速率模式下的读写存储器延迟。英特尔还支持其非易失性Optane持久性内存,该内存通过非易失性技术提供类似于RAM的性能。

XilinxVersalAICore系列(也使用加固的内存控制器)可提供高达1.2Tbps的DDR4带宽和高达1.6Tbps的LPDDR4带宽,并支持CCIX。(缓存一致性的加速器互联,即CCIX™(读成“see6”)是一种能够将两个或两个以上器件通过缓存一致性的方式来共享数据的片间互联。CCIX规范的最大优势之一是它建立在PCIExpress规范的基础之上。CCIX的一致性协议只需很少修改或者无需修改就可以通过PCIExpress链路传递。)

有趣的是,英特尔还通过UPI/CXL协议支持对英特尔至强可扩展处理器的低延迟/一致性存储器层次结构访问。在以后的部分中,我们将与其他供应商讨论更多有关集成到异构计算环境中的问题,并与其他供应商进行讨论。

如上所述,Achronix(还利用了硬化的内存控制器)还支持GDDR6。在外部存储器中,端口数量是许多应用程序的关键考虑因素,因为能够从共享内存资源同时执行多个读/写操作的能力可以消除与内存带宽相关的性能瓶颈。

-

一文详解多芯片封装技术2025-05-14 2523

-

一文解析多芯片封装技术2024-12-30 2412

-

多芯片封装的基本概念和关键技术2024-12-04 3160

-

多芯片封装技术是什么2023-05-24 5227

-

Inside iCoupler®技术多芯片封装2021-06-08 738

-

常见的元器件封装技术简单介绍2020-03-16 2943

-

常见芯片封装技术汇总2020-02-24 3316

-

芯片封装技术介绍2018-11-23 4364

-

多芯片LED集成封装的目的及其技术详解2017-10-10 1487

-

详解多芯片LED封装特点与技术2016-11-11 5597

-

寻找一款宏单元数多,封装小的FPGA或CPLD芯片2016-03-28 6111

-

多芯片整合封测技术--多芯片模块(MCM)的问题2009-10-05 7234

-

新型芯片封装技术2009-04-07 5463

-

芯片封装详细介绍2008-06-14 10069

全部0条评论

快来发表一下你的评论吧 !