Vivado仿真器中的通用验证方法学(UVM)支持

电子说

描述

Vivado 集成设计环境支持将通用验证方法学 (UVM) 应用于Vivado 仿真器。

Vivado 提供了预编译的 UVM V1.2 库。

请遵循以下步骤创建示例设计测试案例,以便在工程模式下使用 UVM。

本文随附了 1 个简单示例,可供您下载解压使用。

1. 在 Vivado 2019.2 中创建新 RTL 工程。

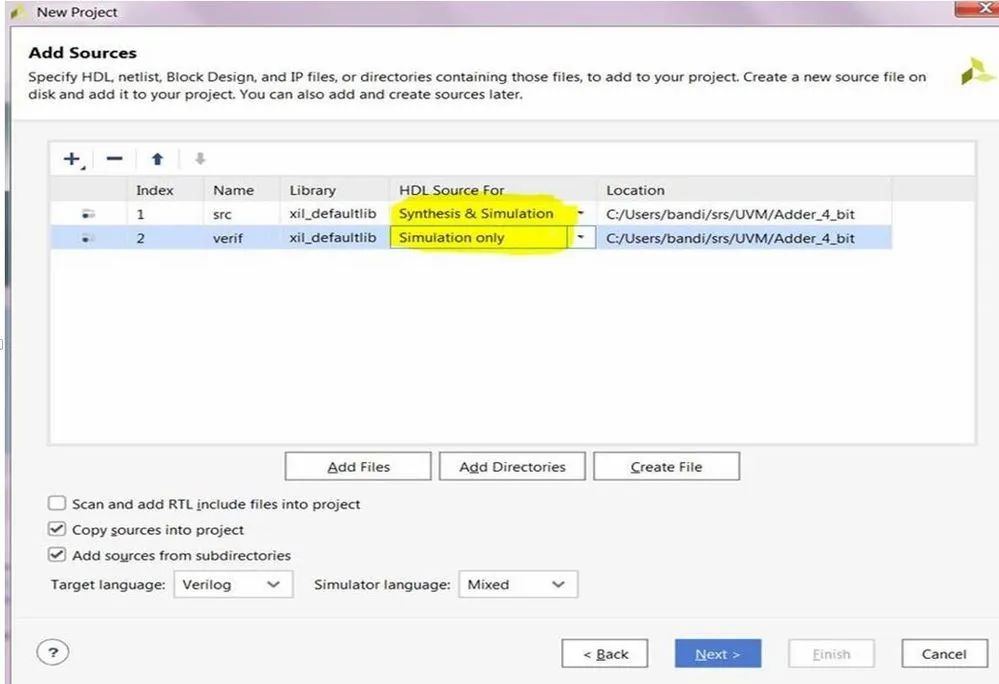

2. 单击“Add Directories”以将“src”和“verif”目录添加至该工程中。指定 UVM 验证文件仅用于仿真 (Simulation Only)。

3. 选择工程所需的器件/开发板,然后单击“Next”。

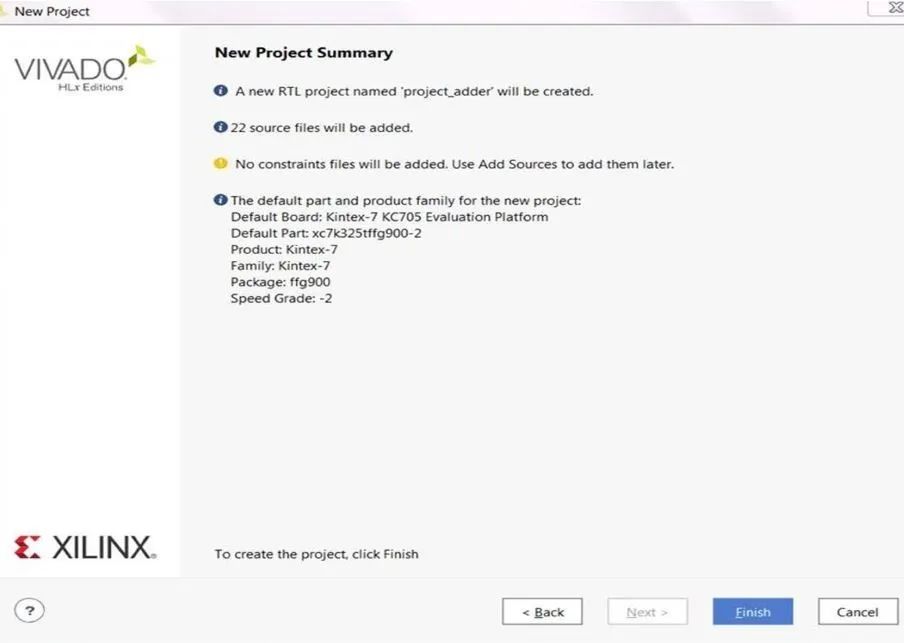

4. 检查“Project Summary”,然后单击“Finish”。

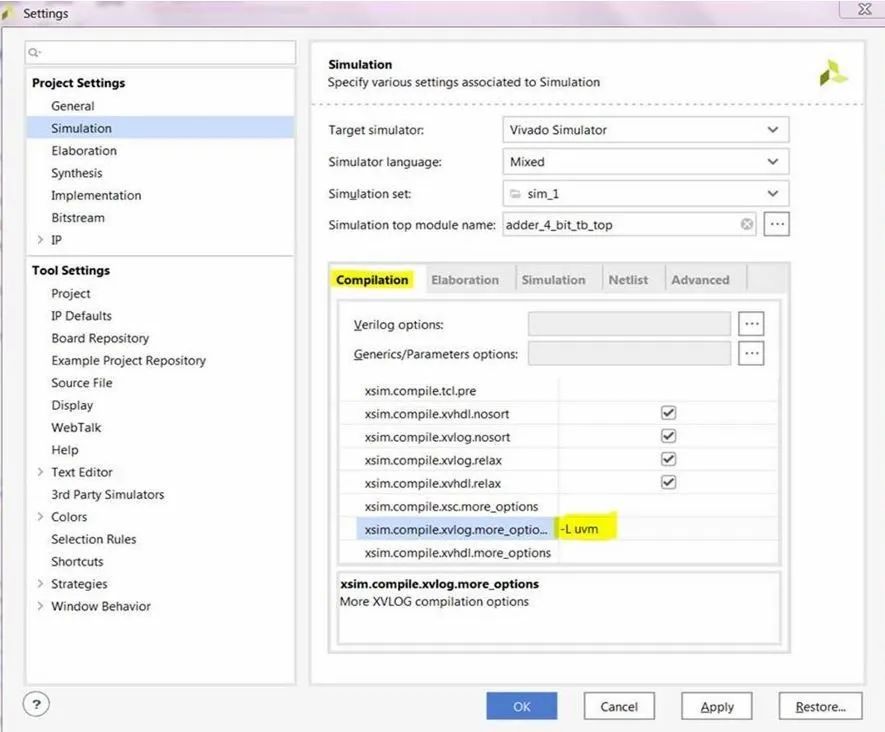

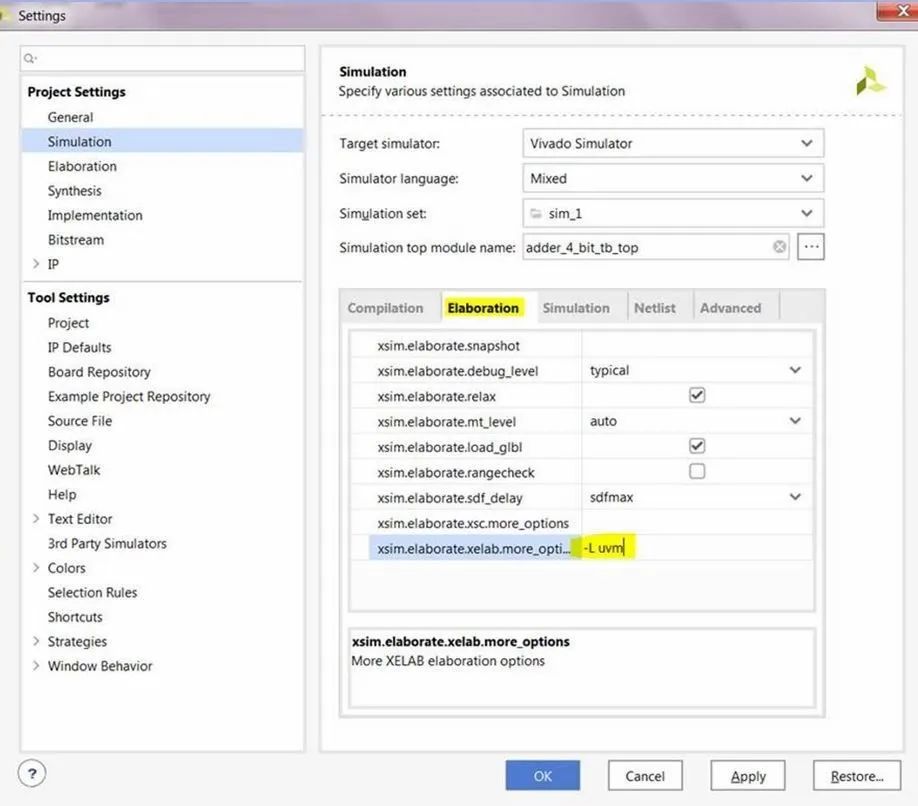

5. 使用来自“src”和“verif”目录的新增源代码创建工程后,请转至“Settings”->“Simulation”。将“-L UVM”开关添加到位于“compilation”选项卡下的 xsim.compile.xvlog.more_options 以及位于“Elaboration”选项卡下的 xsim.elaborate.xelab_more_options(请参阅以下截屏)。此开关是使用预编译的 UVM 库所必需的。

此外,还可通过 Tcl 控制台 (TclConsole) 设置下列属性:

set_property -name {xsim.compile.xvlog.more_options} -value {-L uvm} -objects [get_filesets sim_1]

set_property -name {xsim.elaborate.xelab.more_options} -value {-L uvm} -objects [get_filesets sim_1]

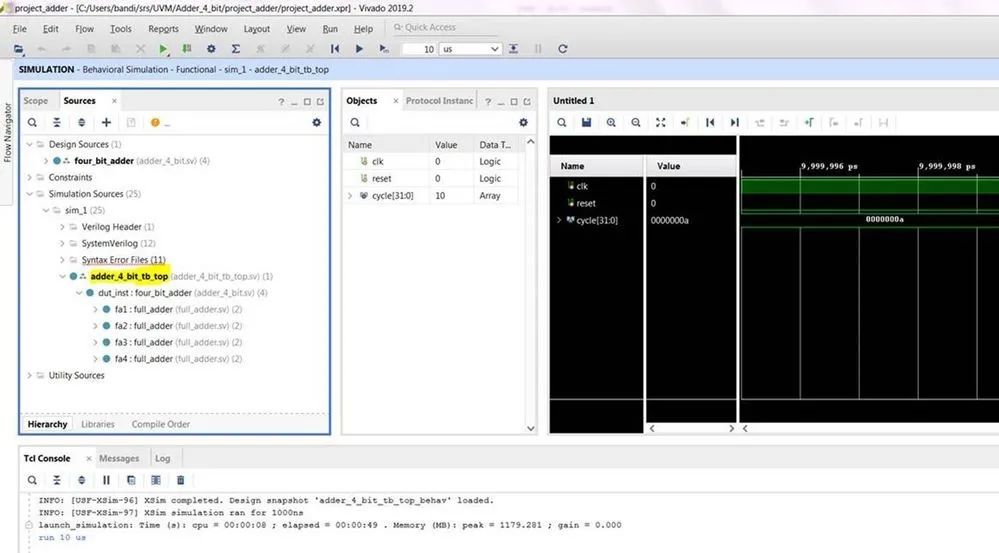

6. 添加以上开关后,请确保已选中“adder_4_bit_tb_top.sv”文件作为顶层模块,然后运行仿真。

仿真应可正常完成运行,但 Vivado“Hierarchy”视图中的“Sources”窗口将显示这些文件上的语法错误。

您可忽略“Hierarchy”视图和Vivado Text Editor 中的有关 UVM 的语法错误,因为 UVM 支持是在 Vivado 2019.2 中专为仿真器新增的。

对应 HSV 的 UVM 支持将于后续版本中提供。

以下是非工程/批量模式下的 UVM 使用步骤:

a, 调用 Vivado 2019.2:

source

b, 要以非工程模式运行仿真,请从当前工作目录切换至“run”文件夹。

cd ./Adder_4_bit/run

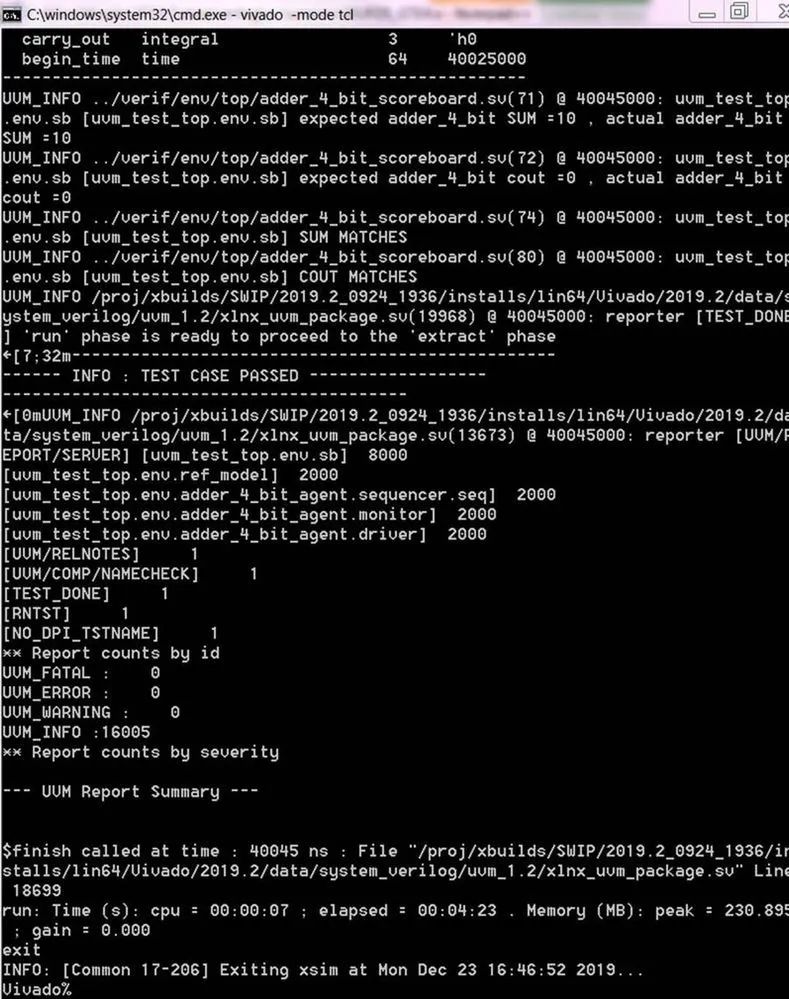

c, 要在Vivado 中运行独立仿真,可运行 run_xsim.csh(在 Linux 上)和 run_xsim.bat(在 Windows 上),或者也可在 Linux/Windows 中使用以下命令来运行 run.tcl。

Vivado –mode batch –source run.tcl

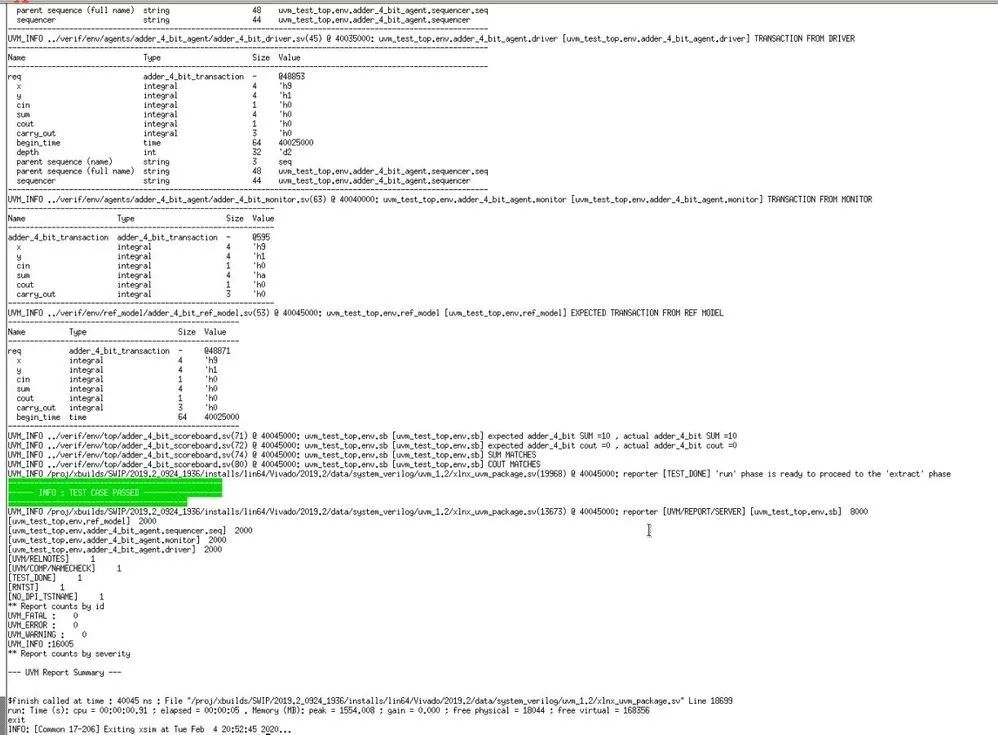

d, 完成仿真后,可以在 shell 中或命令提示符中查看 UVM 测试结果,如下所示:

工程模式和非工程模式的目录结构:

“src”和“verif”文件夹包含设计和验证环境相关的文件。

在非工程模式下,“Run”文件夹是运行仿真的位置。

UVM_test 则用于在 XSIM 中以“工程模式”运行仿真。

-

ASIC芯片设计之UVM验证2022-11-30 2453

-

Vivado仿真器进行混合语言仿真的一些要点2022-08-01 2041

-

使用Vivado仿真器进行混合语言仿真的一些要点2021-10-28 4139

-

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...2021-01-21 4410

-

IC验证"一个简单的UVM验证平台"是如何搭建的(六)2020-12-04 2819

-

如何基于UVM用questa与fpga板子进行软硬件协同仿真?2020-07-27 2851

-

如何基于uvm方法学采用systemc进行IC验证?2019-11-07 2851

-

如何使用Vivado中的Synopsys VCS仿真器进行仿真2018-11-29 8555

-

基于Vivado设计的第三方仿真器版本说明2017-11-15 2639

-

参数化UVM IP验证环境(上)2017-09-15 1496

-

[启芯工作室] 高级验证方法学 VMM 01 OOP review2013-06-16 3107

-

用于SoC验证的(UVM)开源参考流程使EDA360的SoC2010-06-28 2970

全部0条评论

快来发表一下你的评论吧 !