你常用哪种方法去检查3W规则呢?

电子说

描述

为了尽量减小单板设计的串扰问题,PCB设计完成之后一般要对线间距3W规则进行一次规则检查。

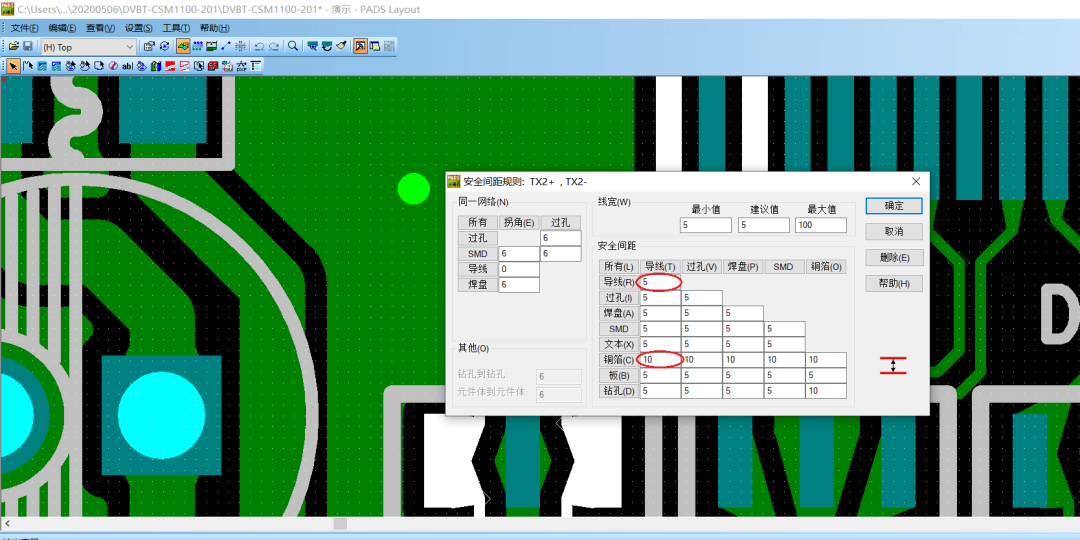

一般的处理方法是直接设置线与线的间距规则,但是这种方法的一个弊端是差分线间距(间距设置大小不满足3W规则的设置)也会DRC报错,产生很多DRC报告,难以分辨,如下图所示。

如何解决这个问题呢?可以利用Altium Designer的高级规则编辑功能、利用PADS的设计规则、利用Allegro、Mentor等对差分线进行过滤。

01

利用Altium Designer ……

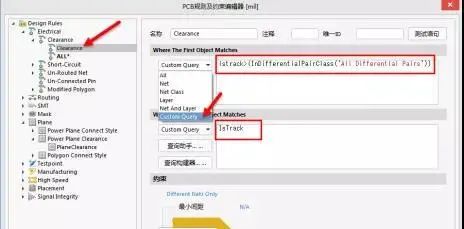

(1)按快捷键“DR”,进入PCB规则及约束编辑器,新建一个间距规则,并把优先级设置到第一位。

(2)如图下图规则设置,在“Where The First Object Matches”处选择“Custom Query”,进入用户自定义界面,然后再选择“查询助手......”,自定义帮助菜单。

(3)PCB规则及约束编辑器中存在高级工具菜单栏,包含“+”“-”“*”等。

这些可用于编辑高级规则,这其实和编写C语言代码类似。由于高级代码的使用频率较低,在此不做说明,如果读者想了解可以参考Altium Designer的官方文档,弄清楚每一个代码的含义再进行编辑。

在此,在自定义代码编辑框中输入“istrack>(InDifferentialPairClass('All Differential Pairs'))”,表示的含义是不包含差分走线的导线。

(4)在“Where The Second Object Matches”处适配“IsTrack”,那么整个规则的含义表述为除了差分线之外的导线和导线之间的距离。

(5)按快捷键“TDR”,重新运行DRC,可以得到下图所示的走线间距规则的结果,差分线之间的间距只有8.6mil,不满足设计的3W规则12mil,但是不再进行报错。

02

利用PADS ……

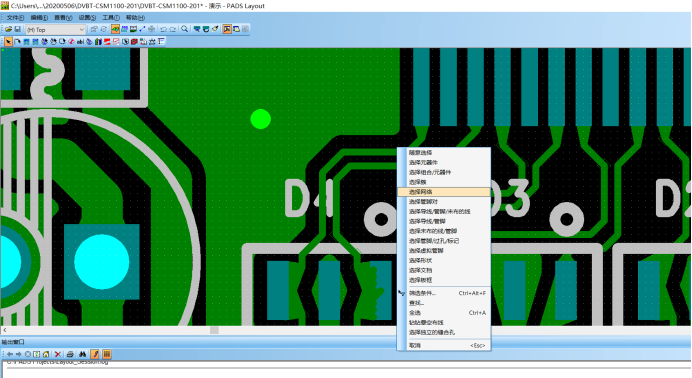

第一步:右键选择网络:

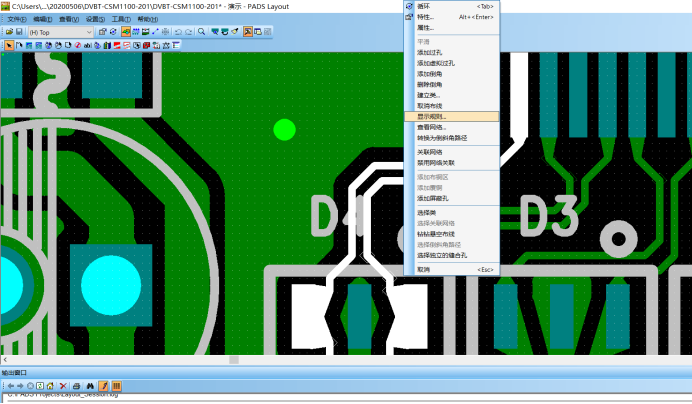

第二步:显示规则:

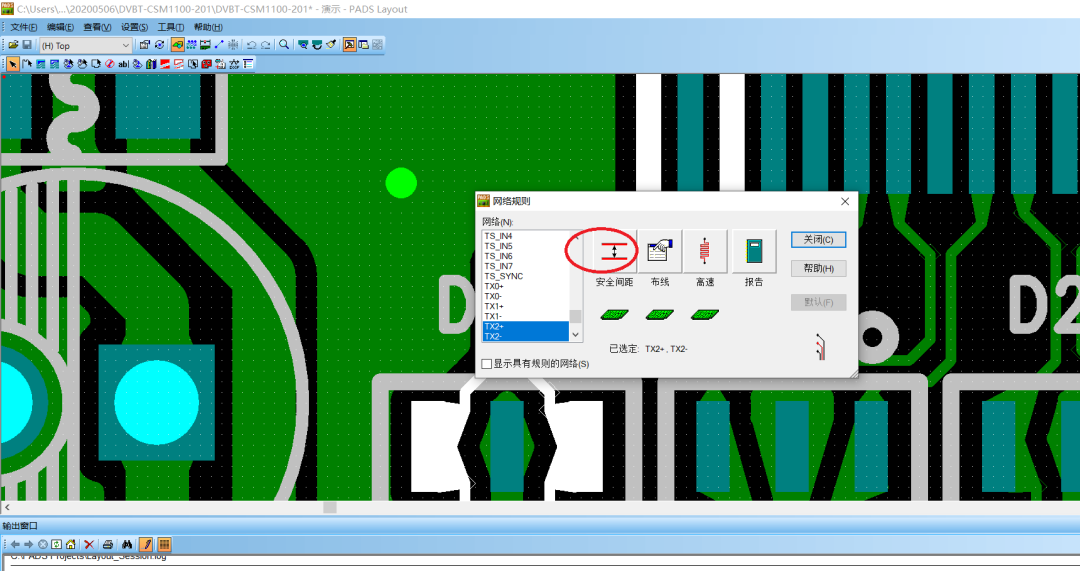

第三步:选择安全间距:

第四步:修改规则:

完成后重新灌铜,就不会再出现DRC了。

03

利用Allegro ……

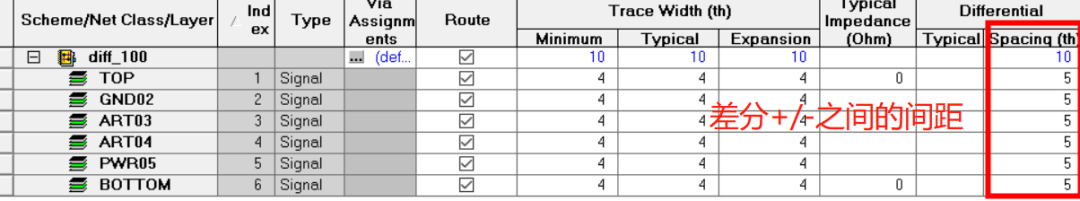

Allegro里面,如果设置了Space约束(比如diff的3w规则),或者默认的space数值大于Primary,就需要添加一个参数,负责差分正负之间也会按照3w规则报drc,解决方法有两个。

方法1:

约束管理器里面,点击Physical---Physical Constraint Set---All Layers,把Min Line Spaceing的数值改小,且必须小于Primary的数值即可。

方法2:

给差分添加一个Diffp_Min_Space的属性,Value值小于Primary的数值即可。

04

利用 Mentor ……

肯定会有网友询问,除了以上三个常用软件,Mentor 如何对线间距3W规则进行规则检查?Mentor软件比较智能,会自动识别差分正负之间的间距和差分对与差分对之间的3w,即:利用规则推动设计。

你常用哪种方法去检查3W规则呢?如果还有更好的“招数”,可以文段后讨论哦~

-

【PCB小知识 6 】3W原则2015-12-12 51823

-

布线3W原则2016-01-09 12130

-

PCB设计的3W规则你了解吗2019-05-21 2026

-

要使用哪种方法去验证 FPGA 的逻辑设计?2021-04-08 1893

-

3W规则是什么?20H规则是什么?2021-04-27 3464

-

3W原则是什么2022-01-26 4731

-

什么是3W规则 20H规则 五五规则2007-12-12 5829

-

Protel硬件开发PCB设计的3W和20H原则及五五规则2016-07-05 7699

-

PCB设计到底哪些信号需要满足“3W原则”?2020-12-09 19709

-

PCB中微带线拐角的“3W规则”是真的吗?2021-02-23 10830

-

为了减小单板设计的串扰问题,设计完成后还要按3W规则检查资料下载2021-04-12 782

-

微带线拐角3W规则,是真的吗?2023-03-02 7224

-

如何理解PCB布线3W规则2023-05-04 4030

-

PCB设计如何对线间距3W规则进行规则检查?2023-05-30 4411

-

如何理解PCB布线的3W规则?2023-07-15 3346

全部0条评论

快来发表一下你的评论吧 !