异步信号边沿检测电路该如何实现呢?

可编程逻辑

描述

所谓边沿检测(又叫沿提取),就是检测输入信号的上升沿和下降沿。在设计数字系统时,边沿检测是一种很重要的思想,实际编程时用的最多的时序电路应该就是边沿检测电路和分频电路了。

那么,边沿检测电路该如何实现呢?

我们知道,在always块的敏感信号列表中可以直接用posedge和negedge来提取上升沿和下降沿,但是如果要在always程序块的内部检测上升沿或者下降沿呢?还是用poesedge和negedge吗?显然是不可以的,因为这样的语句不可综合,我在QuartusII中尝试了,编译时提示 ”multiple event control statements not supported for synthesis !“,意思就是不可综合。实际上,posedge和negedge只能用在always块的敏感信号列表中或者testbench中,所以我们还是通过其他的办法来实现吧。

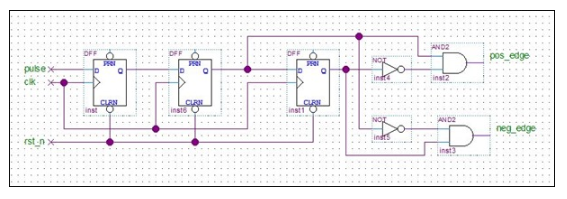

要实现边沿检测,最直接的想法是用两级寄存器,第二级寄存器锁存住某个时钟上升沿到来时的输入电平,第一级寄存器锁存住下一个时钟沿到来时的输入电平,如果这两个寄存器锁存住的电平信号不同,就说明检测到了边沿,具体是上升沿还是下降沿可以通过组合逻辑来实现。如下图所示:

图1 用两级寄存器实现边沿检测

上图使用 block 图表示的,也可以用verilog编写出来,代码如下:

//边沿检测电路

//2014/12/10

module edge_cap

(

input clk, rst_n,

input pulse,

output pos_edge,

output neg_edge

);

reg pulse_r1, pulse_r2;

always @ (posedge clk or negedge rst_n)

if(!rst_n)

begin

pulse_r1 <= 1'b0;

pulse_r2 <= 1'b0;

end

else

begin

pulse_r1 <= pulse;

pulse_r2 <= pulse_r1;

end

assign pos_edge = (pulse_r1 && ~pulse_r2) ?1:0;

assign neg_edge = (~pulse_r1 && pulse_r2) ?1:0;

endmodule

当检测到上升沿时, pos_edge信号输出一个时钟周期的高电平; 检测到下降沿时,neg_edge输出一个时钟周期的高电平。

乍一看,这个电路似乎很简单地实现了边沿检测的功能,但是仔细分析就可以发现这种方法存在一个潜在的风险:当待测信号pulse是一个异步信号时,输出可能是亚稳态,如果pulse信号的变化刚好发生在clk时钟的建立时间和保持时间之内,那么第一级寄存器的输出 pulse_r1 就会进入亚稳态,而pulse_r1的亚稳态会立即传递给pos_edge和neg_edge信号,从而使得整个电路的输出进入亚稳态,进而影响下一级电路的正常工作,甚至导致整个系统崩溃!

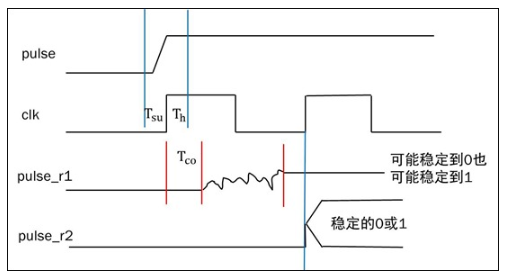

因此,在进行异步信号边沿提取时,不能直接使用上面的这种电路,而应该先将异步信号同步化,一般采用多加一级寄存器的方法来减小亚稳态的发生概率,如下图所示:

图2 异步信号边沿检测

也可以用verilog编写出来,代码如下:

//异步信号边沿检测电路,三级寄存器实现

//2014/12/08

module edge_cap

(

input clk, rst_n,

input pulse,

output pos_edge,

output neg_edge

);

reg pulse_r1, pulse_r2, pulse_r3;

always @ (posedge clk or negedge rst_n)

if(!rst_n)

begin

pulse_r1 <= 1'b0;

pulse_r2 <= 1'b0;

pulse_r3 <= 1'b0;

end

else

begin

pulse_r1 <= pulse;

pulse_r2 <= pulse_r1;

pulse_r3 <= pulse_r2;

end

assign pos_edge = (pulse_r2 && ~pulse_r3) ?1:0;

assign neg_edge = (~pulse_r2 && pulse_r3) ?1:0;

endmodule

经过这样的同步处理后, 可以大大减小电路进入亚稳态的概率,如果第一级寄存器进入了亚稳态,一般也会在一个clk周期内稳定下来(可能稳定为0也可能稳定为1),如下图所示:

图中pulse信号的改变刚好发生在 clk 的建立时间和保持时间之内,因而第一级寄存器的输出pulse_r1可能会进入亚稳态,图中Tco为第一级寄存器pulse_r1的状态建立时间(即clock to output),一般情况下,亚稳态的决断时间(即从进入亚稳态到稳定下来的时间)不会超过一个时钟周期,因此在下一个clk上升沿到来之前,pulse_r1已经稳定下来(可能稳定到0也可能稳定到1),这样第二级寄存器就会采集到一个稳定的状态,从而把亚稳态限制在第二级寄存器之前,保证了整个电路输出的稳定性。

综上所述,在异步信号边沿检测电路中,至少需要采用三级寄存器来实现,在对系统稳定性要求较高的数字系统中,可以采用更多级的寄存器来减小亚稳态发生概率,提高系统稳定性。

-

FPGA设计经验之边沿检测2012-03-01 5474

-

FPGA设计经验:边沿检测2017-08-16 2226

-

fpga应用篇(二):边沿检测2017-04-06 4023

-

STM32定时器怎样通过ETR模式进行边沿检测并计数呢2021-11-24 2861

-

基于AVR单片机的异步串行信号检测装置2009-09-12 519

-

用移位寄存器实现边沿检测的技巧2018-04-15 3756

-

边沿检测的目的及电路原理分析2019-11-19 11955

-

什么情况下我们才会使用边沿信号?2021-05-03 5399

-

FPGA学习-边沿检测技术2022-11-26 2933

-

SIMATIC S7-1500 PLC边沿检测指令与应用2023-04-12 11304

-

Verilog边沿检测的基本原理和代码实现2023-05-12 5798

-

什么是边沿检测2023-06-17 4231

-

Verilog实现边沿检测的原理2023-06-28 4580

-

对于多位的异步信号如何进行同步呢?2023-09-12 2377

-

同步复位和异步复位到底孰优孰劣呢?2024-01-16 2933

全部0条评论

快来发表一下你的评论吧 !