基于FPGA的除法器纯逻辑设计案例

电子说

描述

前边写了很多关于板上外围器件的评测文章,这篇是FPGA纯逻辑设计,是FPGA的另一部分——算法实现,上篇文章做了HDC1000传感器的使用,当时说FPGA是不支持小数的,本篇记述的是FPGA如何去做除法运算。很多人觉得不就是除法嘛,直接打上/即可,但是,FPGA是不能正确综合这个除法器的,综合的结果只是一个固定数值,而不像其他微处理器。可以这么说,用FPGA实现除法运算是比较麻烦的。

用软件编程的时候,用到除法器的时候,一个/就能求商,一个%就能求余,很简单。但是,如果使用硬件来实现除法运算,就需要了解计算机存储结构,二进制的除法和平常使用的十进制除法是一样的,都是通过辗转相除的原理,

原理如上所述,现在需要把这个原理转换成可实现的设计方案,从图可以看出,首先是将除数与被除数的最高3位做比较,如果除数(110)大于被除数(101),则将商赋值为0(最高位是0可以省略),被除数向右增加1位再进行比较;当被除数增加1位,除数(110)小于被除数(1010),则将商赋值为1,接着进行二进制减法运算,被除数(1010)减去除数(110),变成100;然后被除数向右再增加1位,变成1001,再与除数(110)比较,以此类推,最后输出结果。

设计好代码,用Modelsim仿真验证,

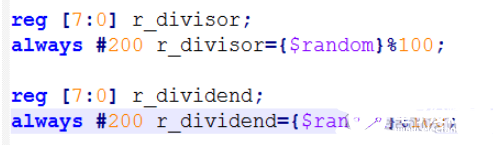

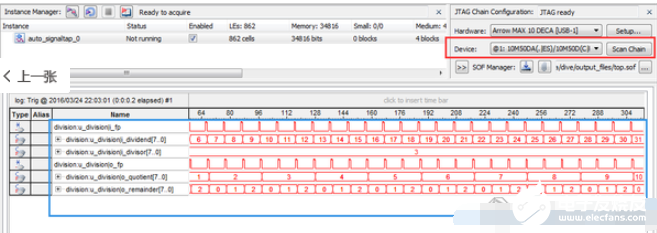

用$random产生随机数,实现效果如下:

i_dividend为被除数,i_divisor为除数,o_quotient为商,o_remainder为余数(下同)。

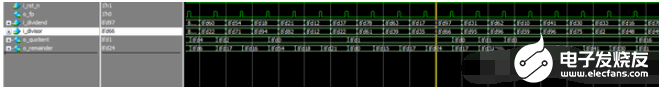

$random是不能综合的,所以,只能用其他的进行代替,被除数用一个计数器,除数用数字3,再进行Modelsim仿真验证:

由2个图可知,除法器设计满足需求。

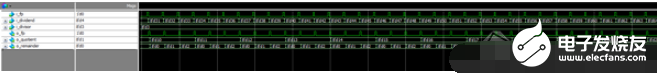

进行板上调试,

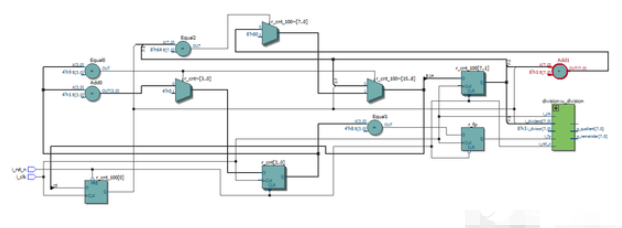

综合后的RTL图,

用Quartus ii软件查看结果,一切与预期一致,设计成功。

总结:用FPGA实现除法器真麻烦!

-

如何对蜂鸟e203内核乘除法器进行优化2025-10-24 268

-

FPGA培训--FPGA高级逻辑设计研修班2009-07-24 3689

-

基于FPGA的除法器2014-05-15 3065

-

高速硬件除法器2020-12-17 11017

-

FPGA逻辑设计中的常见问题有哪些2021-04-29 1352

-

除法器的设计资料分享2021-11-12 2098

-

如何去实现FPGA的逻辑设计呢2021-12-21 1397

-

基于FPGA的MDIO接口逻辑设计2009-12-26 1204

-

并行除法器 ,并行除法器结构原理是什么?2010-04-13 16636

-

除法器对数运算电路的应用2010-04-24 3157

-

FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明2019-03-27 1556

-

实例九— 除法器设计2021-11-07 1074

-

FPGA常用运算模块-除法器2023-05-22 5745

-

FPGA基于线性迭代法的除法器设计2023-07-04 2470

-

基于FPGA的高效除法器设计2025-10-28 2512

全部0条评论

快来发表一下你的评论吧 !