超前进位产生器74182

数字电路图

133人已加入

描述

超前进位产生器74182

打开APP阅读更多精彩内容

多位数的超前进位加法器的进位是并行产生的,大大提高了一算速度。但是随着位数的增加,超前进位逻辑电路越来越复杂。为了解决这一矛盾,设计出了专用的超前进位产生器,用多个超前进位产生器连接,既可扩充位数而又不使逻辑电路太复杂。集成超前进位产生器74182的逻辑图和引脚图分别如下图所示。

对74182的引出端信号说明如下:

74182的输入、输出信号有进位输入端Cn,进位输出端Cn+x、Cn+y

、Cn+z,进位产生输出端FG(低电平有效),进位传输输出端FP(低电平有效),进位产生输入端G0~G3(低电平有效),进位传输输入端P0~P3(低电平有效)。74182的逻辑功能如下列诸表所示。

74182FG输出功能表

74182FP输出功能表

74182Cn+x输出功能表

74182 Cn+y输出功能表

74182 Cn+z输出功能表

根据这些功能表可得到:

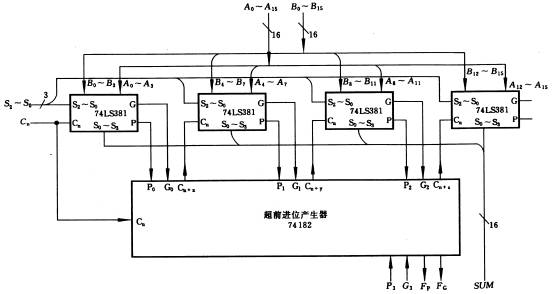

16位全超前进位算术/逻辑运算电路图如下所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 产生器

-

超前进位加法器是如何实现记忆的呢2022-08-05 2523

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 1585

-

Verilog数字系统设计——复杂组合逻辑实验2(8位全加器和8为带超前进位的全加器)2021-12-05 664

-

AD9522 时脉产生器参考设计2020-12-31 692

-

怎么设计一个32位超前进位加法器?2018-07-09 22141

-

超前进位全加器的开关级设计2010-05-28 669

-

脉波产生器电路(Pulse generator)2009-10-22 2270

-

智能延迟触发产生器的设计2009-06-20 770

-

超前进位集成4(四)位加法器74LS2832009-04-07 30251

全部0条评论

快来发表一下你的评论吧 !