为什么语句的不完整会导致锁存器的产生?

电子说

描述

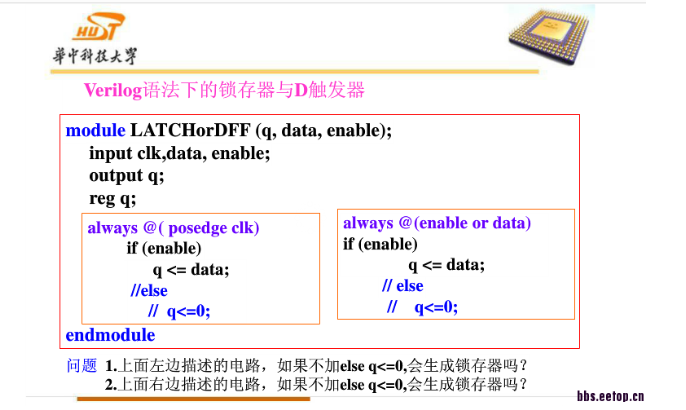

verilog中if与case语句必须完整,即if要加上else,case后要加上default语句,以防止锁存器的发生,接下来就来说说其中原因。

锁存器与触发器最大的区别在于,锁存器是电平触发,而触发器是边沿触发。锁存器在不锁存数据时,输出随输入变化;但一旦数据锁存时,输入对输出不产生任何影响。

为什么语句的不完整会导致锁存器的产生?

解:

老阮 (2014-10-21 19:30:10)

1、时序电路,生成触发器,触发器是有使能端的,使能端无效时数据不变,这是触发器的特性。

2、组合逻辑,由于数据要保持不变,只能通过锁存器来保存。

楼主位的第二个代码就是在enable为低时,数据不变,因此要生成锁存器。 第一个代码,由于是时序逻辑,生成的触发器在enable无效时就可以保存数据。跟锁存器无关。

walkman416

个人理解: 所谓生成latch其实是针对使用always语句描述一个组合逻辑而言,因为如果描述时序逻辑总是使用时钟或者时钟+复位作为敏感列表条件,所生成的电路总是组合逻辑+DFF;如果是描述组合逻辑,敏感列表中必然没有时钟复位,而是组合逻辑的输入信号。在FPGA设计,避免使用latch,不利于时序分析和仿真。 楼上有提到latch比DFF省资源, 这个在FPGA设计中其实还好, 因为在FPGA中DFF就是一个专用的硬件资源,并且数量也比较多。

使用always描述组合逻辑时,好的习惯是使用always @(*)作为敏感列表, 并且需要检查每个分支都有明确的赋值,从而避免生成latch.

黎释注

我是这么理解的,在一份资料看的,

时序电路=组合逻辑电路+储存电路;

储存电路有两个:锁存器(latch)和触发器;

边沿触发产生触发器,

电平触发产生锁存器,

多个触发器组成寄存器,

当描述的是时序电路,寄存器变量对应的寄存器,

描述的是完整的组合逻辑电路,对应为硬件连线,

当描述的是不完整组合逻辑,则寄存器对应的是锁存

总结:

1,存储单元按照触发的方式分为电平触发和边沿触发,电平触发的为锁存器,边沿触发的触发器。 2,对于if,case的完整性,@老阮已经说的很清楚了,在FPGA建议使用触发器。

-

BMP解码显示图片不完整2019-07-10 1617

-

QT解决串口数据接收不完整问题2021-08-18 2927

-

如何解决串口接收数据不完整?2021-11-22 4082

-

stm32 printf打印出错导致信息不完整怎么解决?2021-12-02 2034

-

怎样去解决stm32串口DMA数据接收不完整的问题呢2022-02-21 1389

-

verilog中if与case语句不完整产生锁存器的原因分析2017-09-16 1959

-

不完整地址转发表的拓扑发现方法2018-01-12 799

-

stm32串口DMA数据接收不完整问题说明2021-12-24 3250

-

APM32F091RCT6_SPI_从机接收数据不完整2022-11-09 598

-

浅谈C语言中的三种不完整类型2022-12-16 929

-

如何获取ChatGPT回答不完整的内容2023-02-10 2179

-

C语言中的不完整类型是什么2023-02-21 2291

-

时序逻辑会产生锁存器吗2024-08-28 1560

-

Simulink模型测试典型问题分享-接口定义不完整2025-09-22 1220

全部0条评论

快来发表一下你的评论吧 !