Model是否需要统一的规范?

描述

EDA 是芯片之母是IC 设计最上游、最高端的产业。也是中国集成电路产业最薄弱的环节。为向集成电路专业师生和从业者中系统介绍EDA技术的前沿进展,芯人类将分多期全文引入《电子报》EDA前沿技术专栏。专栏特邀行业多位专家,全面系统地介绍国内外EDA 的状况和国产EDA 的发展。本文为电子报授权发表。包含混合SOC的设计,验证和实现的方法流程三方面内容,并重点介绍了验证所需要了解的仿真器原理,和行为级建模相关的知识。共分三次发表。

Table Model

有点类似于大数据的概念。既然传统的Model和硅工艺联系不怎么紧了,那么直接把Silicon测试出来的数据都列举出来,建立一个数据库(温度、电压和Silicon数值)表格,仿真器用的时候直接查表就行了。你只要关心输入什么值,能输出来什么值就行了,一表在手,有input有output。

放弃对因果关系的过分渴求,取而代之去关注“相关关系”,只是根据实际测试到的silicon的数值,直接做一个数据库,当外界加什么电压、有什么温度时候,就来什么对应的输出电流等。这就类似于大数据的概念,不关心为什么,只在乎是什么。对于不在table里面的数据,仿真器需要插入数值(interpolate)或者外推推断数值(extrapolate) 。短板是离散数据的连续性和光滑性差,需要Analog仿真器做些处理。

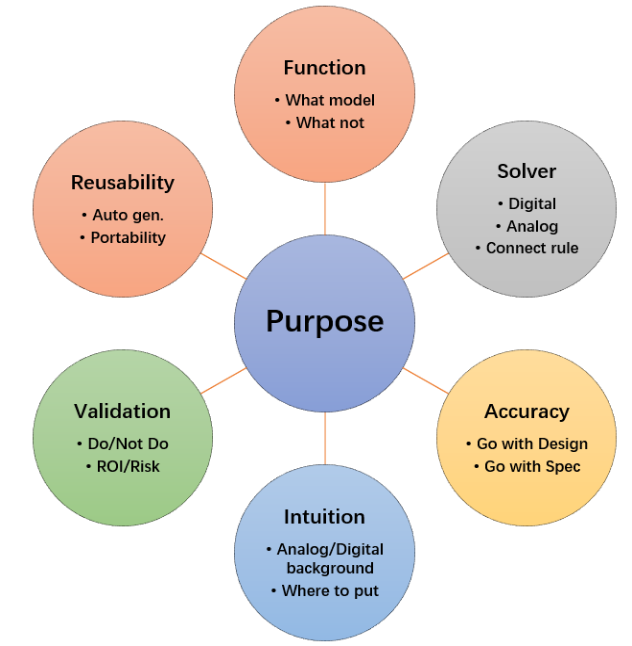

建模前要plan! Plan! plan!

在做Model之前,一定要想清楚做Model的目的是什么。

建模需要考虑的因素

Model是否需要统一的规范?因为验证本身希望能够Reuse。但是一旦想统一规范,可能就需要花费更长的时间和精力,项目是否有时间/值得付出不?哪些Model不要是需要放弃建模的?例如对于非线性(Non-linear)的因素, 是否可以转化为线性。对于弱相关因子(weak dependencies)是否可以忽略;如果进入一个Model的input control/signal不符合Model里面的预期,需要有Assertion来要报错。

Model到底是让Analog Background的人来写?还是Digital的工程师?放在电路的哪个层级?

对于Model要不要做Validation?怎么做Validation?对Model的验证,包括利用相同的Test Bench,对于Model和Schematic出来的结果的验证。验证Model和电路类似,有Block级Schematic和Model的吻合,还有Sub-System能够能通畅的利用Model仿真、以及Model和Sub-System的吻合,更有Model和整个Top的吻合度。为了提高项目效率,是不是可以跳过某些层级?

总之就是做Model也是一门艺术,需要在服务其目的的情况下,做各种trade off。

与Model相关的工具

SMG-1

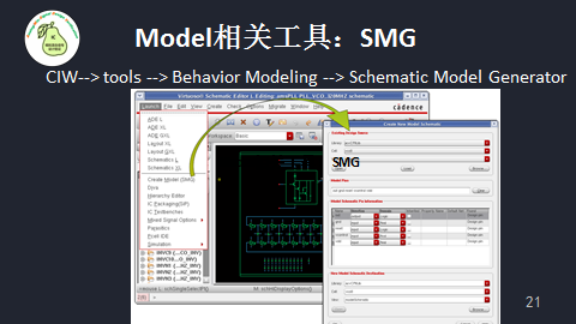

A、SMG

Schematic Model Generator的工具在Virtuoso里面,只要用图形的界面填写一下pin的性质,IO代码就自动生成。

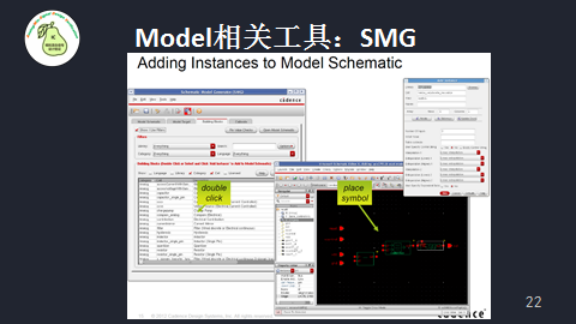

SMG-2

很多内置的小模块BBT(Building Block Text),提供了例示的code,你根据自己的schematic,去搭建设计。

在Model自动化的道路上,设计者和EDA工具开发者需要进一步努力,例如电路设计时候的合理Partition,和考虑标准化Model的电路分层等。

SMG-3

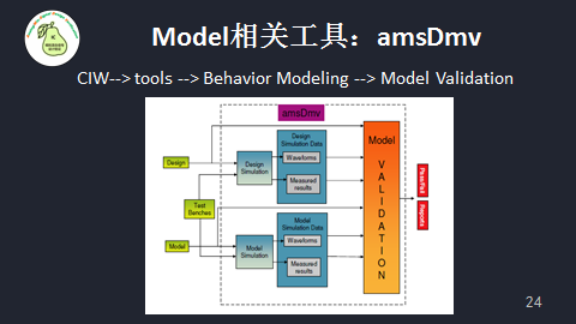

B、amsDmv

Model要和Schematic吻合,amsDmv(AMS Design and Model Validation)提供Model的验证功能。

amsDmv

它利用ADE的结果按一定的误差精度(Tolerance),对比schematic和Model仿真的波形,也可以做最基本的Pin check,以及设置不需要对比的参数(exclude)等信息。

C、Xmodel

有一个xmodel的工具,集成于Cadence Virtuoso环境,有Python和Skill的接口,也是方便做Model的小工具,生成SV语言的Model。

数模混合芯片的物理实现

物理实现将电路转换成芯片物理版图,称之为Tape Out(TO)。数字设计把相同的节距和高度标准单元,通过综合工具得到门级网表,再通过自动布局布线工具(P&R)实现版图。模拟设计将自动生成的参数化的MOS管搭建Pcell。Pcell搭建模块,模块组成定制单元模块,自动邻接、器件走线、虚拟单元并插入阱单元。模拟版图一般是定制的。

对于复杂的数模混合SOC,芯片布局至关重要。在物理实现的初始要自上而下的大局观,定制单元和数字单元同时考虑。自上而下设计中,各模块的面积和摆放位置需要预估,信号流方向和电源布线需要考虑,端口需要优化。在自下而上的Layout中,首先实现包括电阻电容和MOS管的基本器件的版图,然后在考虑其摆放和连线,从而形成一个版图单元;再与其他模块联合。对于低功耗设计,由于输入电源数目不断增加,所以需要自上而下设计。对于较小设计或者可以复用的AMS IP,一般用自下而上的流程。当然目前越来越多的在混合使用两种流程。版图的IP包括硬模块和软模块两类。

基于约束(Constraints)的方法学,正在用于模拟和数字物理实现。约束可以捕捉设计者的意图,并将其传递给掩模版工程师,从而知道和验证版图是否和符合要求。常见模拟约束有:匹配器件,敏感信号的标记和处理,高电压或高功耗信号,保护环和其他隔离结构。数字IC中,设计定义时序约束,从而进行门级网表综合。布线结束后,会抽取线上寄生,进行静态时序分析STA,来检查物理实现是否符合要求。

物理实现之后,需要进行后仿真。模拟IC常见的抽取方法有只提取电容C,只提取电阻R,电阻电容都提取(RC),电阻电容电感(RCL)提取。数字IC,将线延迟转换到标准延迟格式(Standard Delay Format)SDF当中,从而进行后仿真,获知寄生对电路性能的影响。

到真正流片之前,还要做设计规则检查DRC(Design Rule Check);电学规则检查ERC(Electrical Rule Check);版图对照电路检查LVS(Layout Versus Schematic)来保证版图符合电路的连接关系;和针对制造的设计检查DFM(Design For Manufacture)来发现影响制造质量与良率的因素。

电学特性感知设计(Electrically Aware Design)EAD代表了范式转移的方法,将电学特性分析和验证前馈到设计过程中。

例如,考虑先进工艺引入的邻阱效应(Well Proximity Effect, WPE);浅沟隔离效应(Shallow Trench Isolation, STI),和电迁移效应。为数模混合验证提供电学特性感知设计的解决方案以及方法学的优化将是一场持久战。

作者简介

邵亚利,模拟混合信号设计验证专家。浙江大学本硕,“模拟混合信号设计验证”公众号(yaliDV)创始人。曾就职于德州仪器(TI),现就职于亚德诺(ADI)半导体公司。ADI(Analog Devices) 是全球领先的高性能模拟技术公司,凭借杰出的检测、测量、电源、连接和解译技术,搭建连接现实模拟世界和数字世界的智能化桥梁。

责任编辑:pj

-

龙芯CPU统一系统架构规范及参考设计下载2024-06-20 2678

-

为什么国产MCU的工程生态很难统一?2026-01-28 1781

-

刚柔板设计是否需要专用设计软件与规范?国内何处可以承接该类电路板加工?2009-09-06 2841

-

液晶面板接口是否统一2012-10-26 3802

-

Verilog HDL代码书写规范2017-12-08 10071

-

Android开发统一规范2017-11-28 602

-

自动驾驶的最终量产 需要统一的标准来把关2018-11-19 2025

-

pcb设计需要遵循哪些规范2020-03-20 3995

-

特斯拉Model 3和Model Y电池将统一规格,成通用产品2020-07-22 2135

-

如何看待未来 手机接口是否统一2020-07-27 607

-

华为:如何定义5G是否清洁、是否安全,需要一个理性的标准2020-09-23 2129

-

IEEE SystemVerilog标准:统一的硬件设计规范和验证语言2022-08-25 790

-

什么是统一色彩?如何实现全文档色彩的规范统一呢2022-08-30 3747

-

Instruct-UIE:信息抽取统一大模型2023-04-25 2897

-

中铁建智能安全帽与统一视频平台smarteye配奥维地图是否绝配?2024-04-17 1108

全部0条评论

快来发表一下你的评论吧 !