基于CPLD器件实现双主设备PCI总线仲裁器的设计

接口/总线/驱动

描述

PCI(Peripheral Component Interconnect)总线是现今最为流行的工业控制总线之一。它广泛地应用在计算机中,并且由于众多厂商对PCI的良好支持,使得目标嵌入式设备中的很多解决方案都包含了PCI总线。在多主设备的PCI系统应用中,必须对各个主设备提供仲裁授权信号。很多厂家有针对性地发布了PCI仲裁逻辑的专用芯片或者集成了PCI重载逻辑的专用芯片,但使用不够灵活,为了使PCI设备能够更方便地应用在嵌入式系统中,本文介绍了一种基于CPLD(复杂可编程逻辑器件)的PCI总线仲裁器的设计方法,此方法可以为系统量身定制适合于系统本身的PCI总线仲裁器。而不必局限于特定的芯片要求,在体积、功能、成本等诸多方面都有很好的应用前景。

1、 PCI总线仲裁简介

1.1 PCI总线的仲裁原理

PCI总线是一种共享式的总线,可以连接多个主设备,但由于数据传输的独占性,每一时刻只能由一个主设备占用总线。因此,为了有效地利用PCI总线宽带,必须设置一个总线仲裁器,按照一定的算法协调系统中各个主设备的操作。

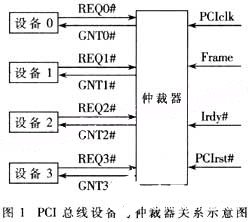

每个具备主设备功能的PCI设备必须提供两个与仲裁有关的信号:REQ#和GNT#。其中REQ#为请求总线信号,由需要发起PCI传输事务的设备发出,GNT#为总线授权信号,由PCI总线仲裁器裁决后给出,接到GNT#信号的PCI设备将在下一次总线空闲后开始操作。

PCI总线仲裁的裁决过程可以在PCI传输期间完成,并不占用PCI总线的宽带,这称为隐式仲裁,即需要发起PCI操作的设备可以随时发出请求REQ#,PCI仲裁器立即批准该请求被给出GNT#,但是真正的传输操作一定要等到当前传输完成,即总线空闲后才可以开始,图1描述了PCI总线设备与仲裁器的关系。

1.2 PCI总线仲裁规则约定

(1)仲裁器的仲裁算法必须保证所有的设备都能得到授权的机会,否则将会出现某个优先级低的设备永远不能占有总线进行事务操作的情况。

(2)如果FRAME无效,GNT可以在任意时间撤销,以便服务于另一个主设备或者作为对主设备车REQ的响应。

(3)如果GNT信号被撤销但FRAME有信号,当前的总线正在传输数据,则操作合法。

(4)如果总线不处于空闲状态,则允许一个GNT的撤销和另一个GNT的发生在同一个周期,如果处在空闲状态,则要求一个GNT撤销到下一个GNT的发出之间必须有一个时钟周期间隔,否则可能会在AD线和PAR线上出现冲突。

(5)GNT信号的每次发出,只限于相应的总线主控器可以使用总线进行一次总线操作(一个FRAME发出到撤销),如果该主控器需要多次总线访问,它可以保持REQ信号一直有效。仲裁器会按照特定的仲裁算法来决定是否仍判给该主设备。

(6)一个主控器可以在任意时刻撤销其REQ信号,REQ信号一旦撤销,仲裁器将认为该设备不再请求使用总线,因而撤销其GNT信号(参考上文(1))。如果一个主控器只希望做一次总线传输,则它应当在发出FRAME的同一时钟周期撤销REQ。

(7)如果当前的主控器在它的GNT信号发出后,持续16个空闲周期还没有开始总线操作,则仲裁器视其为超时,仲裁器可以在任意时刻撤销GNT信号,以便服务于另一个设备。

1.3 PCI总线仲裁的算法

目前,应用于PCI总线仲裁的算法主要有固定优先级算法和动态优先级算法两种,在固定优先级算法中,各个设备的优先级是事先确定好的,仲裁器针对事先设定好的优先级为每个设备分配使用权。这种算法的缺点是:一旦PCI总线事务非常繁忙,优先级高的设备会占有总线不放,将导致优先级低的设备无法申请到总线。可见这是一种并不公平的算法,只适用于总线利用率非常低的情况,动态优先级算法是在每次仲裁授权后动态改变各个设备的优先级。在保证每个设备都有机会获得总线的情况下,优先级改变的算法可以是各式各样的。最常用的是循环优先级算法,即每次仲裁授权后将排队中的设备优先级加1。因其算法简单,且对大部分应用都十分有效。本设计采用循环优先级算法。

1.4 总线停靠

当PCI总线空闲时,一个设备从申请总线到被授权使用,最小也需要2个时钟周期,这对于PCI总线是一种浪费。因此仲裁器通常选中一个最经常占用总线的设备,PCI总线空闲时将GNT#赋予它,这叫做总线停靠。当总线空闲时,该设备需要占用总线时可马上得到批准。

2、 双主设备PCI总线仲裁器的实现

下面描述了一个具有两个设备的总线仲裁器的硬件实现,其一为TriMedia嵌入式DSPCPU PNX1300,其二为Intel i82559网络控制器,系统结构如图2所示。

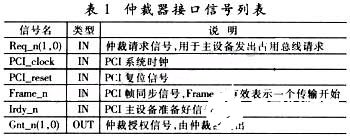

该仲裁器的接口信号如表1所示。

为设计方便起见,在程序中设计三类状态机:总线状态状态机、总线主设备查询状态机、仲裁状态机。

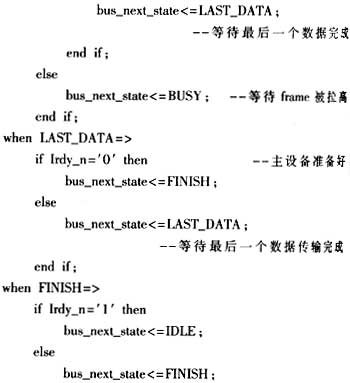

2.1 总线状态状态机

总线状态状态机用于记录总线事务的状态,定义如下:

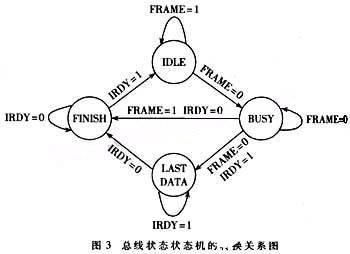

type bus_state is(IDLE,BUSY,LAST_DATA,FINISH)

四种状态分别表示总线空闲、忙、最后一个数据传输期以及传输完成。状态图如图3。

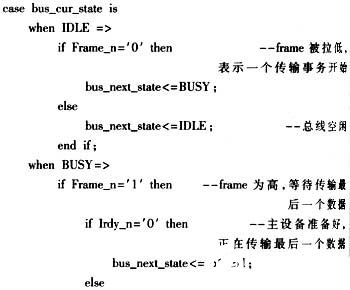

下面是以VHDL代码形式实现的该状态机的状态转换关系。

2.2总线主设备查询状态机

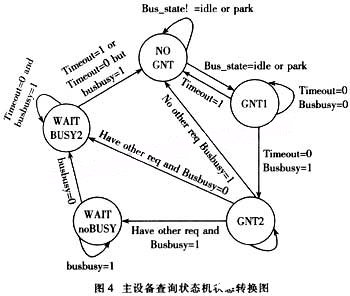

总线主设备查询状态机用来决定当前是否需要重新指定一个主设备,重新指定一个主设备的条件是:(1)当前被授权的设备已开始传输;(2)当前被授权的设备没有开始传输并且超时。将主设备查询状态分为IDLE、GNT1、GNT2、WAIT_NOBUSY和WAIT_BUSY2五个状态,并设置计数器count,当总线上某个设备被授权,但16个周期仍然没有开始操作,count超过16,被视为超时,仲裁器可以撤销其仲裁授权,并传授其他设备,程序根据这个状态机的输出结果决定仲裁状态机是否改变。

状态转换如图4所示,状态机描述的VHDL代码略。

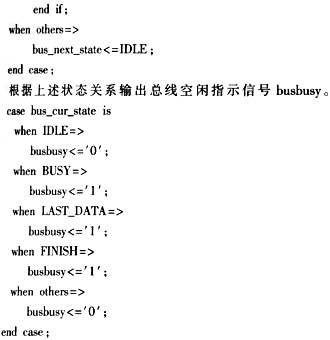

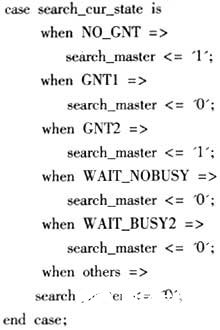

主设备查询状态机的输出信号search_master:

该状态机的驱动条件是由总线状态状态机的输出结果(busbusy)、仲裁状态机的状态(idle,park)和计数器的产生的超时信号(timeout)组成,设置WAIT_BUSY2的目的是为了避免可能会在AD线和PAR线上出现的冲突。该状态机的输出search_master作为仲裁状态机状态转换使能信号,只有该信号有效时,仲裁状态机才进行当前状态的改变。

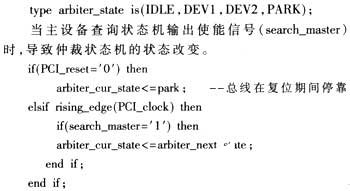

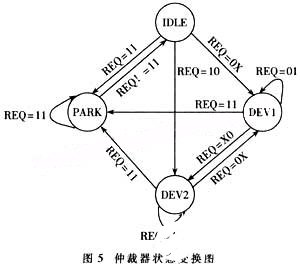

2.3 仲裁状态机

仲裁状态机表示总线仲裁器的状态,定义如下:

状态转变过程如图5所示,状态机描述的VHDL代码略。

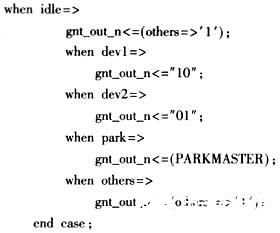

仲裁器根据仲裁状态机当前状态控制仲裁授权信号(GNT)的给出。

注:PARKMASTER是事先设置的停靠状态。

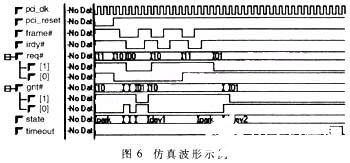

2.4仿真波形图

由图6可以看出,测试文件模拟了一个设备申请和两个设备同时申请的情况,并给出了总线授权信号(GNT),验证了仲裁器逻辑的正确性。

2.5 资源占用情况分析

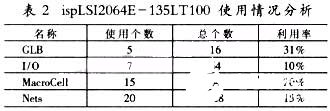

可编程逻辑器件使用Lattice公司的ispLSI2064E135LT100,在ispLever中综合本例程序,结果如表2。

综合后的延迟分析显示,该逻辑的时钟周期最小为7.5ns,即该逻辑可以运行在133MHz以下的系统中,完全可以胜任33MHz PCI总线的仲裁工作。

本PCI总线仲裁器已成功地应用在基于PNX1300的IP会议电视终端系统中,用于处理嵌入式CPU PNX1300和网络控制器I82559的总线占用仲裁。该会议电视终端已于2005年1月在国家泰尔实验室通过测试并取得入网许可证。

责任编辑:gt

-

PCI总线特性及信号说明2012-04-06 7530

-

PCI接口设计原理2019-04-24 2158

-

基于PCI总线的CPLD实现2019-05-29 1729

-

简易通用型PCI接口的VHDL-CPLD设计2019-06-17 2326

-

采用CPLD实现32 bit 33 MHzPCI从设备接口2019-06-20 2096

-

PCI总线仲裁参考设计Verilog代码2008-05-20 1377

-

基于PCI总线的开放性接口设计2009-06-01 555

-

PCI总线仲裁器的设计及实现2009-09-03 831

-

PCI总线至UTOPIA接口控制的CPLD设计实现2006-03-11 1253

-

基于EPLD的PCI总线仲裁器的设计与实现2009-06-20 1459

-

用双端口RAM实现与PCI总线接口数据通讯2011-01-07 2371

-

PCI总线传输的终止方式2011-05-18 740

-

PCI总线从设备接口的CPLD实现2011-11-30 900

-

利用CPLD实现的PCI从设备接口设计2012-08-06 2596

-

总线仲裁的名词解释_总线仲裁分类2020-12-14 6465

全部0条评论

快来发表一下你的评论吧 !