三星和联发科7纳米5G智能手机芯片

描述

ISSCC是半导体行业历史最悠久的技术会议之一,每年二月在美国旧金山举行。这次会议汇集了学术界和产业界人士,讨论芯片电路设计的最新挑战。该会议主要是一个电路设计会议,每个厂商都专注于他们的处理器中独特电路设计的一个或多个特定方面。

今年的会议涵盖了一系列深入主题,包括锁相环、低功耗电路、内存、SerDes、DSP和处理器设计。处理器部分出现了领先的供应商,也有来自研究机构和学术界的项目。会议内容覆盖了密集的芯片设计细节,下面介绍了处理器环节中有趣细节的突出部分。

三星和联发科7纳米5G智能手机芯片

这两款5G智能手机的SOC设计分别来自联发科和三星,它们关注的是为大公司混合不同Arm内核的CPU设计问题。此外,还解决了处理单元在重载时内部电压下降检测的问题。

第一个演示来自三星,该公司选择构建一套三集群的CPU核心。三星在三个集群中的两个使用了Arm授权的内核,但是性能最好的内核是由三星自己在Arm的架构许可下设计的——双M4内核。双M4核心有一个单独的3MB L3缓存,核心目标是达到Intel i5的性能水平。

对于中等功率/性能范围,三星使用了Arm Cortex-A75内核。“小型”节能内核是古老的Cortex-A55。三星M4核与Cortex-A55核之间的功率/性能差距太大,增加了Cortex-A75核来弥补这一差距。三星还在1024台MAC电脑上增加了一个神经处理单元,但没有提供太多细节。

高性能处理器中的电压下降可能是一个问题。如果增加太多的保护带,保持较高的电源电压,那么会消耗更多的能量。在一个更节能的额定电压下,当一个特定的耗电单元处于负载之下时——比如一个运行高分辨率游戏的GPU——内阻下降会导致内部电压低于正常值。SOC供应商构建专门的电路来检测这些压降,并采取行动来缓解问题。他们的方法是延长时钟,通过有效降低时钟速度来降低电路速度和功耗。三星采用环形振荡电路,可以根据电压改变速度。压降检测在时钟管理单元(CMU)中设置一个标志,并将时钟速度减半。

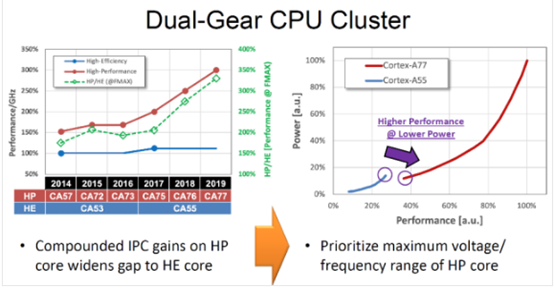

联发科采取了不同的方式来选择CPU核心,坚持ARM的big.LITTLE方案,联发科称之为双齿轮设计。联发科使用较新的Cortex-A77 CPU内核实现较强的性能内核。联发科还指出,Cortex-A55小内核并没有跟上性能内核的发展,他们没有增加性能中等的核心,而是努力将A77的电压范围扩大到较低的速度。三星只有两个性能核心,联发科有四个A77核心。4个A77和4个A55内核共享一个2MB L3缓存。

联发科对压降的最初反应是在die上提供储存电荷,可以提供一些瞬时电流,但这需要宝贵的die面积。因此,它决定将时钟拉伸以节省die空间。

联发科的一个重大变化是使用了锁频环(FLL),而不是锁相环(PLL)。FLL设计有双时钟,但这个设计包含不确定性,因为它允许振荡器随电压变化。有了FLL电路,联发科Vmin大约有35mV的改进,节省了10%的功耗。联发科还为该芯片构建了一个新颖的JTAG解决方案,该解决方案带有一个网关TAP,用于分层访问测试电路。

联发科芯片还支持WiFi6,支持5G独立和非独立模式。A77核心支持高达2.6 GHz的时钟速度,该芯片有一个Arm Mali G-77九核GPU。

-

联发科位列全球智能手机芯片市场份额第一2020-12-29 3188

-

打败高通,联发科首次跃居全球最大手机芯片厂商2020-12-28 2751

-

Counterpoint:三季度联发科首次成为全球最大智能手机芯片厂商2020-12-25 2157

-

联发科推出一款5G智能手机芯片天玑7002020-11-11 4493

-

三星A系列智能手机将有望搭载联发科5G芯片2019-12-11 3632

-

台媒:联发科5G芯片打入三星供应链2019-12-09 2163

-

高通/联发科/三星2017年的手机芯片大战2017-03-06 5908

-

联发科逆袭:智能手机芯片出货量1年增长11倍2012-12-15 1628

-

智能手机芯片之争一触即发2012-10-25 3388

-

mt6577_联发科智能手机芯片深解2012-08-20 46509

-

联发科年底推四核杀手级芯片2012-08-11 3854

-

智能手机芯片排位赛:高通大幅下滑 联发科进前五2012-08-09 2696

-

联发科称今年重点推3G及智能手机芯片2010-01-13 700

全部0条评论

快来发表一下你的评论吧 !