Cortex-M3是一款ARM处理器内核

电子说

描述

大家都应该知道STM32、Cortex-M3、ARMv8-M与ARM有关,但可能分不清他们是什么关系,或者具体是什么东西。

一、总述ARMv8-M:是一款ARM架构。ARM架构分为:ARMv1、 ARMv2 ··· ARMv8。而ARMv8分为:ARMv8-A、 ARMv8-R、 ARMv8-M。

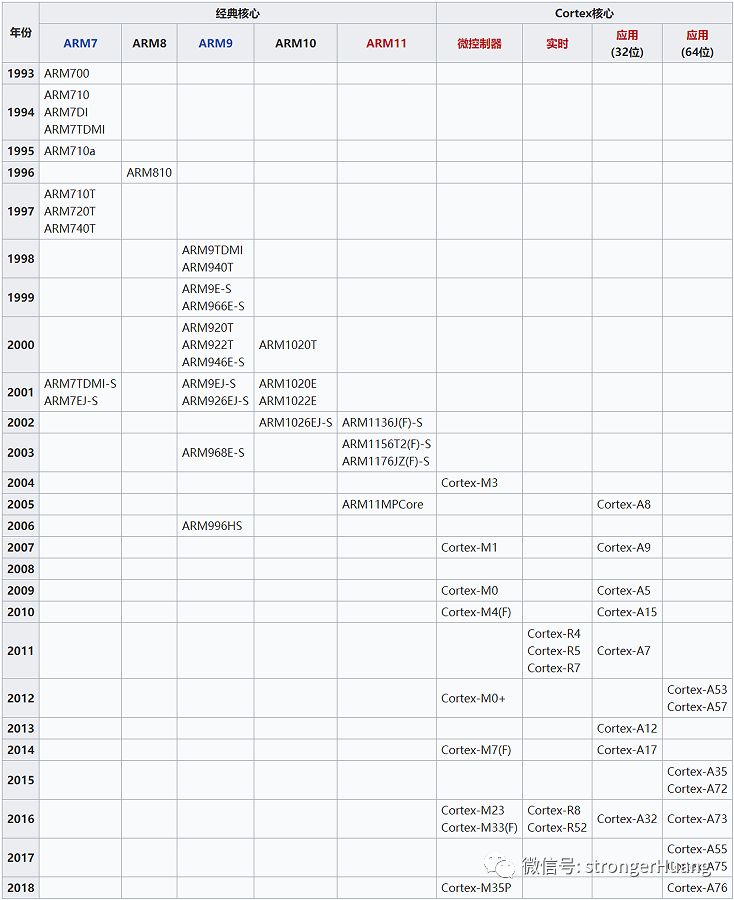

Cortex-M3:是一款ARM处理器内核,也可以理解为ARM处理器家族之中的一个成员。ARM处理器内核分为:经典核心和Cortex核心。传统的核心:ARM7、ARM9等。Cortex核心:Cortex-A、Cortex-R、Cortex-M等。

STM32:是一款ARM内核的处理器芯片。STM32绝大部分是Cortex-M内核,也有少部分包含Cortex-A7(比如:STM32MP)。

如图:

其实还可以细分很多内容,除了这些,还有一些我们常见的内容,比如ARM指令集、Thumb-2指令集等。

以上是总述的内容,下面再进一步描述其中的一些细节。

二、架构

从1995年开始,《ARM体系结构参考手册》是ARM文档的主要来源,提供了关于ARM处理器架构和指令集,区分接口,所有的ARM处理器的支持(如指令语义)的实现细节可能会有所不同。该体系结构随着时间的演变,并与Cortex系列的核心开始,存在三个“配置”的定义如下:

“应用”配置: Cortex-A 系列

“嵌入式”配置: Cortex-R 系列

“微处理器”配置: ARM Cortex-M 系列。

每个配置允许有其子集的架构。例如,用于ARMv6-M配置(所使用的Cortex M0 / M0+/ M1)的一个子集ARMv7-M架构(支持较少的指令)。

三、CPU模式

在任何时刻,CPU只可处于某一种模式,但可由于外部事件(中断)或编程方式进行模式切换。

用户模式:仅非特权模式。

系统模式:仅无需例外进入的特权模式。仅以执行明确写入CPSR的模式位的指令进入。

(svc) 模式:在CPU被重置或者SWI指令被执行时进入的特权模式。

Abort 模式:预读取中断或数据中断异常发生时进入的特权模式。

未定义模式:未定义指令异常发生时进入的特权模式。

干预模式:处理器接受一条IRQ干预时进入的特权模式。

快速干预模式:处理器接受一条IRQ干预时进入的特权模式。

Hyp 模式:armv-7a为cortex-A15处理器提供硬件虚拟化引进的管理模式。

四、ARM授权方式

ARM公司本身并不靠自有的设计来制造或出售CPU,而是将处理器架构授权给有兴趣的厂家。

标题中的STM32就是属于ARM公司授权Cortex-M内核给ST公司生产的一款处理器。

ARM提供了多样的授权条款,包括售价与散播性等项目。对于授权方来说,ARM提供了ARM内核的集成硬件叙述,包含完整的软件开发工具(编译器、debugger、SDK),以及针对内含ARM CPU硅芯片的销售权。

许多半导体公司持有ARM授权:Atmel、 ST、NXP、 TI、 IBM等。

在知识产权工业,ARM是广为人知最昂贵的CPU内核之一。单一的客户产品包含一个基本的ARM内核可能就需索取一次高达美金20万的授权费用。而若是牵涉到大量架构上修改,则费用就可能超过千万美元。

五、ARM核心时间线

早在1993年,经典的ARM7就问世了,直到现在大家看到的Cortex-A系列处理器。

其实,在ARM7之前,都还有一些相关的处理器,感兴趣的朋友可以上网了解。

责任编辑:pj

-

EVAL-ADuCM350EBZ是一款16 MHz ARM Cortex-M3处理器,具有高精度AFE2019-08-28 3048

-

STM32 的核心Cortex-M3 处理器是什么2021-07-23 1776

-

Cortex-M3简述2021-11-10 1589

-

基于ARM Cortex-M3内核的STM32处理器有何性能2021-12-06 2845

-

制造一种基于Cortex-M0和Cortex-M3处理器的SoC2022-07-27 4295

-

STM32系列ARM Cortex-M3微控制器原理与实践2010-01-12 2315

-

Cortex-M3内核浮点型运算的研究与实现2011-03-11 13307

-

STM32 微处理器及接口技术及cortex-m3与ARM7的对比2017-09-12 1179

-

STM32系列ARM Cortex-M3处理器微控制器原理与实践2017-09-22 1357

-

选择ARM处理器,ARM7还是Cortex-M32017-12-04 994

-

Cortex-M3内核的ARM处理器的应用资料说明2020-09-24 1914

-

ARM Cortex-M3 处理器的主要特性分析2021-06-17 15148

-

Cortex-M3处理器内核与基于Cortex-M3的MCU关系2021-11-05 2138

-

STM32 的核心Cortex-M3 处理器2021-12-01 1215

-

Cortex-M3芯片有哪些2024-03-11 2952

全部0条评论

快来发表一下你的评论吧 !