解决方法论问题可提升实现的一致性

电子说

描述

改进设计时,如果 QoR 不升反降,那么您势必将面临如下选择。

是继续修复?还是重新寻找新的解决方案?您可能忽视了某些问题,或者可能工具在运行给定轮次时性能有所下降。能否快速准确解答这一问题恰恰是判断 FPGA 工程师是否足够出色的标准之一。

这里有一个好办法- 解决方法问题即可简化这一任务。在最近赛灵思内部调研中发现,29 种客户设计的方法问题得到了解决。这些设计被归到一起并与其原始版本进行比较。

随后对这两类设计稍作调整:

将关键时钟的周期收紧 1ps 和 2ps

小幅更改网表

更改工具运行时使用的设置

结果毫无疑义地证明,采用经过清理的方法完成设计所产生的实现结果比未采用此类方法的设计的实现结果的一致性更高。

| 实验 | QoR 离散值减少 |

| 网表更改 | -48% |

| 约束更改 | -10% |

Report Methodology 的检查对象

report_methodology 将基于约 150 条规则进行检查,这些规则与约束使用错误、欠优化时钟设置、原语中缺少流水线寄存器问题等有关。

它是 (UG949) 中详述的“UltraFast 设计方法”的补充工具。可用于自动执行诸多检查

https://china.xilinx.com/support/documentation/sw_manuals/xilinx2019_2/c_ug949-vivado-design-methodology.pdf

Report Methodology 所在位置

您可在流程中任意阶段运行 report_methodology。

通常只需在流程初期执行 opt_design 后运行此工具,布局或布线后将看到相同的结果。

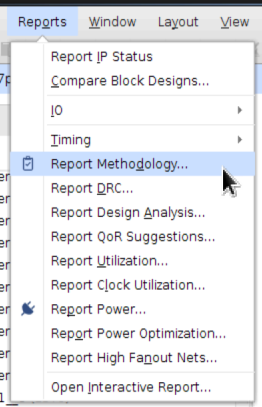

您可通过以下方法找到 Report Methodology:

1.从 Vivado IDE 中的“Reports”->“Report Methodology”下拉菜单中

2.使用 Tcl 命令:report_methodology。

3.您还可在 Report QOR Assessment 中查看 Report Methodology 的精简版本。RQA 报告将详列影响 QoR 和工具变化的不合规的方法检查。要获取完整报告,请运行 report_methodology 命令。

解决方法问题意义非凡

总而言之,解决方法问题时,毋庸置疑,所付出的时间同样有助于得到更为一致的实现结果,从而使您能够作出更准确的决策。这也将使您能够减少运行轮数,并比对结果,同时仍可确信 QoR 修复有效且工具正予以响应。

参考标签:

qor

https://forums.xilinx.com/t5/tag/qor/tg-p/board-id/support_blog

report_methodology

https://forums.xilinx.com/t5/tag/report_methodology/tg-p/board-id/support_blog

report_qor_assessment

https://forums.xilinx.com/t5/tag/report_qor_assessment/tg-p/board-id/support_blog

-

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别2024-03-11 2226

-

DDR一致性测试的操作步骤2024-02-01 4279

-

如何保证缓存一致性2023-10-19 2682

-

顺序一致性和TSO一致性分别是什么?SC和TSO到底哪个好?2022-07-19 2672

-

如何实现信号电压幅值的一致性?2021-05-20 1787

-

什么是霍尔元件的一致性2020-10-12 2756

-

LTE基站一致性测试的类别2019-06-06 1959

-

自主驾驶系统将使用缓存一致性互连IP和非一致性互连IP2019-05-09 4081

-

c6678cache一致性2018-06-24 3491

-

Cache一致性协议优化研究2017-12-30 1179

-

加速器一致性接口2017-11-17 4545

-

EMI一致性测试调试方法2017-09-12 1053

-

CMP中Cache一致性协议的验证2010-07-20 1019

-

一致性规划研究2009-04-06 675

全部0条评论

快来发表一下你的评论吧 !