COT电源控制芯片控制模式介绍

控制/MCU

描述

众所周知,开关电源的控制方式主要包括了传统的电压模式、峰值电流模式、平均电流模式。这些主要流行的控制模式统统归属于 PWM 控制模式。而 PFM 模式基本出现在下列的情况中:

电压滞环控制芯片,如 TI-TPS5211, TI-LM3485,ON-CS51031, MP-2905。

电流滞环控制芯片,如 Microchip-HV9930,TI-LM27212。

在一些电源控制芯片中,轻载工况下,还会切换至 burstmode 以及 pulse skipping mode,这两种模式也归属于 PFM 控制模式,用于提高轻载工况下的效率。也有其他学者指出 Pulse Skipping mode,另归一类。

谐振控制器基本都是 PFM 控制模式。在之前的推文中,帅锅也介绍过基于 bang-bang control 的 LLC 控制芯片,bang-bang 也即是 PFM 控制模式的一种。(VMC 和 CMC 的 LLC 控制器仿真对比 第四节 (Ti UCC25640x 混合滞回控制))

今天要介绍的 COT 控制模式,即是 Constant-on-time mode,恒定导通时间控制,它由滞环控制模式发展而来。顾名思义,其在整个控制过程中会保持开通时间 Ton 恒定不变。当然,相应也有 constant-off-time mode,不做过多介绍。

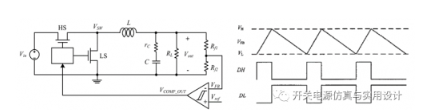

滞环控制

滞环控制如下图,分压电阻得到的反馈电压 vfb 和参考电压 vref 通过一个滞环比较器比较,我们假设滞环比较器的环宽为 h, 一般来说,滞环带宽一般在 15mV~20mV 之间。当 Vfb 低于 vref-(1/2)h 时,比较器输出为高,HS 打开,电感电流线性上升,由 ESR 带来的输出电压纹波此时也会线性上升,vfb 亦复如是。当 vfb 高于 vref+(1/2)h 时,比较器输出为低,LS 打开,电感电流下降,输出电压和 vfb 纹波下降。

迟滞控制的优势在于其环路极其简单,无需误差放大器,也不需要考虑复杂的补偿问题,因此可以达到非常大的带宽,瞬态响应速度极快。

图 1 滞环控制模式

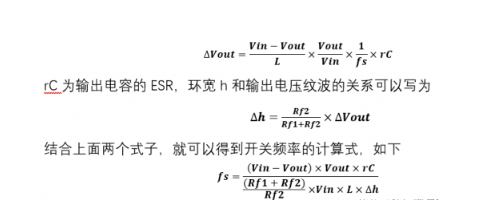

当 Buck 工作在 CCM 模式下,其输出电压纹波可以计算为

可以看出,开关频率和选择的电感、滞环环宽以及电容 ESR 都有关系。Vin 变化时,以及 ESR 会受到温度的影响而变化,比较器的传播延迟等,都会影响到开关频率,这会使得 EMI 的处理变得比较困难。

图 2 输出纹波电压细节

而实际上,输出电容还有 ESL 存在,ESL 带来的纹波会在输出电压纹波上形成一个小尖锋,有可能在开关状态切换的时候,导致反馈电压 vfb 会超出滞环的上限。再考虑耦合到输出纹波上的噪声,可以想象,控制器会变得非常敏感。另一方面,当输出电压较高时,其输出纹波会增大。因此,其商用的 IC 总体来说并不多。

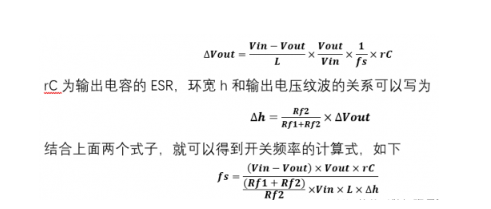

恒定导通时间(COT)

COT 控制模式基于滞环控制模式发展而来。在基本的迟滞控制中增加一个单稳态计时电路(One Shot)控制功率管的导通时间,使功率管导通一个恒定的时间。

图 3 COT 控制模式

当反馈电压 vfb 低于参考电压 vref 时,比较器的输出 vcomp_out 会拉高,SR latch 被置位,Q 输出也拉高,HS 就被打开,电感电流线性上升,输出电压纹波以及 vfb 上的纹波也会上升,因此,vcomp_out 会立马拉低,形成一个脉冲。而 Q 输出拉高同时,也启动了单稳态计时器,直到这个固定开通时间结束。单稳态定时器输出 vone_shot 翻转拉高,复位 SR latch。当结束 HS 开通过程后,电感电流下降,输出电压纹波也下降,直到 vfb 再一次低于 vref,开启新的周期。

可以看出,COT 是一种纹波电压谷底控制方式。如果系统已经开通了一个 Ton 的时间,发现 vfb 仍然低于 vref,怎么办呢?从逻辑控制图中可以看出,此时 vcomp_out 会一直高电平,当 Ton 结束,Q 拉高之后,S 和 Q 均为高电平,根据 SR latch 的真值表,此时 SR 处在 invalid 状态,是不允许出现的逻辑错误。因此,可以再 Ton 结束后,增加一个最小关断时间 Toff_min,强制关断 HS,然后再进行下一次 Ton 开通。一方面增加 Toff_min 可以保证逻辑正确,另一方面也可以避免 HS 一直导通情况下的电感器的饱和。

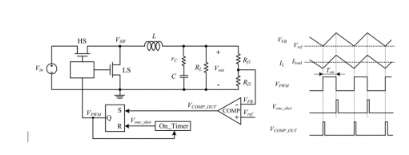

COT 的稳定性问题:

从上面的逻辑控制图中可以发现,COT 的稳定性建立在 vfb 纹波上,也即输出电压纹波上。当输出电压纹波足够大时,可以保证足够的稳定性。因此直观地看,COT 是一种基于 power stage 大信号的非线性控制。利用环路分析仪扫描伯德图仅仅适用于电压模式、电流模式之类线性控制系统,此时对 COT 控制已经不再适用。

-

COT控制模式的电源稳定性验证原理揭秘2026-01-23 1160

-

COT控制模式的前世今生2023-09-17 9174

-

开关电源常用控制芯片有哪些?2023-08-18 15031

-

COT控制模式简述-12023-02-08 11720

-

如何采用 COT 稳压器动态控制输出电压2022-11-07 808

-

开关电源的电压和电流控制模式介绍2022-02-10 20235

-

控制单芯片端和推挽开关模式电源开关电源2021-08-31 1342

-

COT控制模型逻辑是怎样的2021-03-11 2559

-

COT控制模式的详细资料说明2021-01-12 3052

-

常用的几种电源芯片控制模式解析2020-03-20 12724

-

采用COT稳压器动态控制输出电压2018-09-19 2762

-

浅谈COT控制BuckBuck为什么是天然稳定的?稳定条件是什么?2018-02-15 47709

-

[转帖]开关电源变换器工作模式–COT固定开通时间模式2017-03-08 5189

-

开关电源变换器工作模式--COT固定开通时间模式2016-10-27 12745

全部0条评论

快来发表一下你的评论吧 !