PCB设计的EMC有哪些注意事项

EMC/EMI设计

描述

一、前言

随着对高速电路需求的不断增加,PCB设计变得越来越具有挑战性。对于PCB上的设计,工程师必须考虑影响电路的几个方面,如功耗,PCB尺寸,环境噪声和EMC。以下将介绍硬件工程师如何解决EMC相关问题的方式方法。

二、模拟电路

携带模拟信号的布线应远离高速或开关信号,并且必须始终保持接地信号。应始终使用低通滤波器来消除与周围模拟走线耦合的高频噪声。此外,重要的是不要共用模拟和数字子系统的地平面。

三、去耦电容

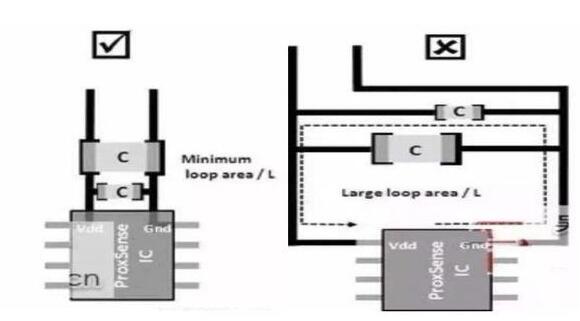

电源上的任何噪声都会影响正在运行的器件的功能。通常,耦合在电源上的噪声具有高频特性,因此需要旁路电容或去耦电容来滤除该噪声。去耦电容可以为电源平面上的高频电流提供低阻抗路径。电流流向地平面GND的路径会形成一个接地回路,也就是会形成环形回路面积。通过在IC电源的附近放置一个去耦电容,并且尽可能靠近IC电源端放置,可以减小环形回路面积。减少环形回路面积可以减少辐射发射的能量,并可能减少潜在的辐射发射源。

同时需要注意的是,在一定频率范围内,虽然随着频率的增加,理想电容的电抗接近于零。但是,市场上没有绝对的理想电容。此外,电容的引线和IC封装的引脚也会增加寄生电感,所以最好使用具有低ESL(等效串联电感)的电容来改善去耦效果。

四、电缆

大多数与EMC相关的问题都是由电缆传输数字信号引起的,这些信号线可以作用为辐射天线,从而向外辐射发射。使用双绞线电缆有助于消除感应磁场带来的共模干扰。当使用带状电缆时(比如排线),必须提供多个接地回路。对于高频信号,必须使用屏蔽电缆,屏蔽层在电缆的起始端和末端都要接地。

五、串扰

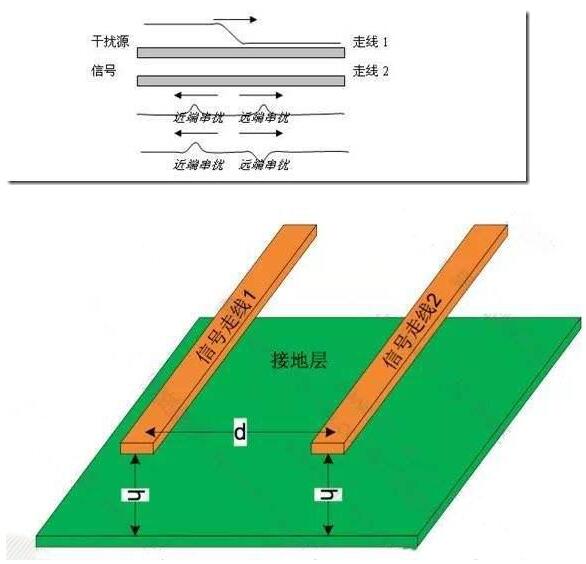

串扰可以存在于PCB上的任何两条布线之间,并且可以产生互感和寄生电容。在数字系统中,由互感引起的串扰通常大于由寄生电容引起的串扰。可以通过增加两条布线之间的间距或通过减小与地平面的距离(比如多层板的层叠顺序)来减少互感。

六、屏蔽

屏蔽不是电气解决方案,而是降低EMI的机械方法。金属屏蔽(导电铜箔或磁性材料)用于防止EMI从系统中辐射出来。根据需求,可以使用金属屏蔽罩覆盖整个系统或其中一个部分。金属屏蔽罩就像一个连接到地面的封闭的电容器,它通过吸收和反射一部分辐射来有效地减小环形天线的尺寸。同时,这种屏蔽还可以减弱辐射的Eenergy从而避免EMI影响到另一个区域而充当两个空间区域之间的金属隔离。

随着EMC需求的增大,对EMC的整改措施和手段也提出了更高的要求。希望这篇文章能给各位看官在EMC整改设计方面带来一定的助力和借鉴。

-

PCB设计的EMC有哪些注意事项2024-06-12 1966

-

VGA OUT 的PCB设计注意事项2023-11-23 2022

-

PCB设计涉及的参数及注意事项2023-04-13 3496

-

触摸按键测试板PCB设计注意事项2022-10-25 1216

-

滤波电路的PCB设计注意事项2021-11-11 2920

-

混合信号PCB设计注意事项是什么2021-04-26 1739

-

混合信号PCB设计有什么注意事项?2021-04-25 2366

-

PCB工程师注意事项2020-03-01 5337

-

PCB设计有哪些注意事项!2012-12-14 9145

-

PCB设计EMC方面电源注意事项2010-04-17 1022

-

PCB设计中对电流回路的注意事项2010-04-16 4688

-

PCB参考设计规范 PCB设计注意事项2009-11-30 6844

-

pcb设计注意事项2009-01-18 1240

全部0条评论

快来发表一下你的评论吧 !