介绍使用IBERT调试FPGA芯片高速串行接口性能的步骤

可编程逻辑

描述

随着高速数字系统的发展,高速串行数据被广泛使用,内嵌高速串行接口的FPGA也得到大量应用,相应的高速串行信号质量的测试也越来越频繁和重要。通常用示波器观察信号波形、眼图、抖动来衡量信号的质量,Xilinx提供的IBERT(Integrated Bit Error Ratio Tester)作为一种高速串行信号测试的辅助工具,使得测试更便捷,其具有不占用额外的I/O管脚和PCB空间、不破环接口信号的完整性、无干扰、使用简单和价格低廉等特点。

1、 IBERT简介

IBERT是Xilinx提供用于调试FPGA芯片内高速串行接口比特误码率性能的工具,具备实时调整高速串行接口的多种参数、与系统其他模块通信及测量多通道误比特率等功能,支持所有的高速串行标准,包括:PCI Express、RapidIO、千兆以太网、XAUI等。使用IBERT核测试,只需通过JTAG接口下载设计并测试硬件,无需额外的管教和接口;大幅缩减了高速串行接口测试场景的建立和调试时间,是高速串行接口开发中理想的调试工具。

文中所述使用方法基于Xilinx的工具CoreGenerator12.4和ChipScope Pro Analyzer12.4进行描述,下面介绍使用IBERT的步骤,IBERT的操作分为两个阶段。

1.1 配置IBERT核,生成配置文件

(1)打开Core Generator12.4工具,新建设计工程,指定待测器件类型、封装、速度等级,生成工程文件。在IP Catalog窗口\View by Function\Debug&Verification\Chipscope Pro\下,双击IBERT,配置线速率、GTP位置和参考时钟、系统时钟等IBERT核参数,生成可JTAG加载的bit配置文件。与生成其他核不同,IBERT核不是插入到用户的设计中去的ngc或edn文件,而是生成自身的bit配置文件。

(2)IBERT核和ILA核(Integrated Logic Analyzercore),也需要连接到ICON核(Integrated Controllercore)上,但其自身具备控制、监控以及改变高速串行接口参数的逻辑,并能完成误比特性能测试。需注意的是,IBERT核只能作为一个独立的设计,不可在用户设计中例化。不同系列芯片的IBERT核在Core Generator中的配置不同。

1.2 IBERT核的主要组件

(1)BERT(比特误码率测试)逻辑:BERT逻辑中例化了高速串行接口组件,并包括了测试模式发生器和检查器。利用Comma和Comma检测器,可提供从简单的时钟信号到完全的PRBS模式以及成帧计数模式。可产生各种PRBS数据作为高速串行发送器的数据源,可设置多种环回,由接收通道接收,对高速串行接收器的接收数据进行相同编码的检测,计算比特误码率。

(2)DRP(动态重配置端口)逻辑:每个高速串行接口均有一个动态重配置端口,因此每个收发器属性都可在系统中改变。所有的属性和DRP地址在IBERT核中均可读可写,且可独立访问。

(3)控制盒状态逻辑:管理IBERT核的操作。

1.3 配置到FPGA中完成测试

测试时,建立JTAC连接,使用ChipScope Pro Analyze12.4下载bit配置文件。下载成功后,在New Project窗口会出现IBERT Console点击即进入Console Window,该窗口可以设置高速串行接口的参数,进行开环或闭环的误码测试,同时提供高速串行接口参数的控制和监视接口。Console Window有4个界面:MGT/BERT Settings、DRP Settings、Port Settings和Sweep Test Setting。下面分别介绍每个界面的功能。

(1)MGT/BERT Settings:MGT Settings部分可以设置摆幅、预加重、均衡以及接收采样点的位置等参数,同时可设置开环或闭环的测试方式,测试进行中可以显示线速率和所测试的高速串行接口的锁相环状态。BERT Settings部分可以设置测试发送和接收数据的编码方式,并显示测试的误码率结果。Clock Setting部分显示收发线路的时钟信息。

(2)DRP Settrags:可查看并设置高速串行接口的属性。

(3)Port Settings:可查看并设置高速串行接口的接口状态。

(4)Sweep Test Setting:本界面用于自动扫描测试,是IBERT提供的一项便利高效的测试方式,可设定发送和接收的可控制参数范围,自动逐个地进行遍历性的误码测试,参数包括发送摆幅、预加重、接收均衡器、CDR采样数据的位置等。用户可设定每组参数重复测试次数以及测试时间,最后点击Start即可进行扫描测试。测试数据保存在.csv文件中。只能在近端环回和远端环回测试模式中使用。

2、 实例说明

设计实例使用Xilinx公司Spatan6系列的xc6slx150t-3fgg676芯片,根据上述使用说明,下面具体说明使用IBERT进行测试的过程。

(1)打开Xilinx ISE DesignSuite12.4/ISEDesignTools/Tools/Core Generator,新建工程,设置芯片信息如图1所示,点击确认,生成核的工程文件。

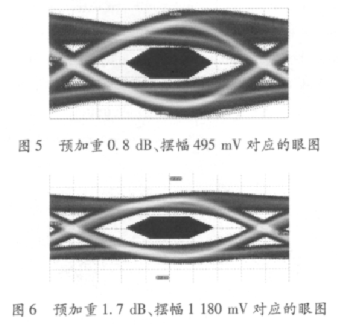

在IP Catalog窗口\View by Function\Debug&Verification\Chipscope Pro\下双击Ibert,如图2所示。按顺序设置Ibert核线速率2.457 6 Gbit·s-1,数据宽度20 bit,参考时钟频率122.88 MHz,选择被测试的GTP DUAL,设置系统时钟频率66 m、位置R7等参数,IBE RT Core Summary如图3所示,点击generate生成Ibert核的可下载bit配置文件。

(2)将生成的bit文件加载到单板上,显示界面如图4所示。

首先关注PLL Status状态和Clocking Setting显示的收发时钟频率,PLL Status状态Locked表明GTP_DUAL的PLL已锁定GTP的参考时钟,GTP可正常工作。如状态是Unlocked,则要检测待测GTP的参考时钟是否正常输入。

测试高速串行信号的信号质量,通常使用足够带宽和采样率的示波器测试信号眼图来评估,一但测试的眼图不符合模板要求,需要调整高速串行接口的参数。使用IBERT核可以快速完成参数修改的任务,设置Loopback Mode在开环的模式下,TX Data Pattern为PRBS7-bit,调整摆幅、预加重参数,观察示波器上的信号眼图是否符合模板要求。图5和图6分别为调整摆幅预加重参数前后的眼图,图5所示眼图对应预加重0.8 dB、摆幅495 mV,眼图的眼高太小且图形碰撞模板,调整为预加重1.7 dB、摆幅1 180 mV,眼图满足的要求如图6所示。

为确定高速串行接口的参数是否满足硬件及多种环境的需求,可通过在对端器件高速串行接口设置远端环回,设置待测试芯片的收发data pattern为统一模式,常温及高低温拷机,观察误码率是否满足要求,误码率需满足E-10。例中与图6对应的参数值条件下,对端器件高速串行接口设置远端环回误码率为4.36E-10,满足误码率要求。

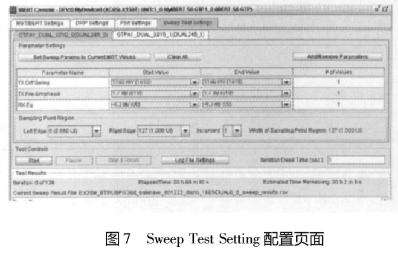

Sweep Test Setting(扫描测试)其配置页面如图7所示,以Rx Sampling Point来进行误码率测试定性分析信道质量为例,较为容易理解,当同定在某个采样点进行误码测试时,误码率达到E-10时,可判定信道质量良好。在整个UI范围内进行采样点的扫描测试时,误码率达到E-10的采样点越多,信号眼图的眼睛张得越大,距离模板的余量越大,信道质量越好。

3、 结束语

通过以上实例,可见IBERT具有可操作性较强的GUI图形界面,可操作性强、准确、易用,可方便地设置高速串行收发通道的各项参数,并提供了多种环回模式及多种测试激励源,并可通过自动扫描测试,确定收发的最佳参数。可以满足硬件测试时对高速串行收发通道信号测试的大部分需求,在故障定位等场合均可使用。在单板的硬件测试初期,使用IBERT可以辅助硬件测试,例如设置发送通道的各项参数,协助示波器测量信号质量,而完全不需额外的开发FPGA逻辑。进行误码率测试,作为定量测量眼图质量、jitter等指标的补充。从示波器看图确定出的参数并非就是最佳参数。如示波器对于均衡后的信号质量无法测试,而通过IBERT测误码率能够测试到均衡之后的节点,测试范围更大。可以预见,集成比特误码测试仪IBERT将在FPGA设计中获得广泛应用。

责任编辑:gt

-

FPGA与高速ADC接口简介2025-06-12 3476

-

fpga开发板使用教程之在K7上用Ibert实现基本的GTX测试2020-12-31 9497

-

谁介绍一款FPGA出串行高速2711串行接口芯片2015-05-25 6382

-

利用 IBERT 进行 GTX 信号眼图测试 精选资料分享2021-07-20 1315

-

基于FPGA的高速串行传输接口研究与实现2010-09-22 642

-

设计和调试高速存储器接口的高效设计流程模型介绍2018-01-12 1773

-

集成式比特误码率测试仪的原理、功能及在FPGA芯片调试中的应用2018-11-29 5084

-

使用Vivado 2016.3中IBERT调试的好处及步骤2018-11-20 6619

-

如何设计实现Xilinx FPGA高速串行接口2020-08-24 1783

-

关于ZC706评估板的IBERT误码率测试和眼图扫描详细分析2021-04-27 9653

-

ZC706评估板IBERT误码率测试和眼图扫描2023-06-21 6043

-

基于IBERT的GTX数据传输测试2023-08-31 4938

-

FPGA与SRIO调试步骤2024-04-19 2951

-

高速串行总线系列-IBERT使用介绍2024-12-20 4392

-

智多晶XSBERT让高速串行接口调试化繁为简2025-05-30 1309

全部0条评论

快来发表一下你的评论吧 !