时序逻辑电路需要了解的关键点

可编程逻辑

描述

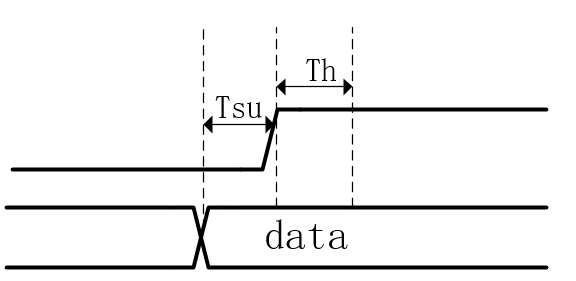

题目:简述建立时间和保持时间,作图说明

建立时间Tsu(setup):触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间Th(hold):触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

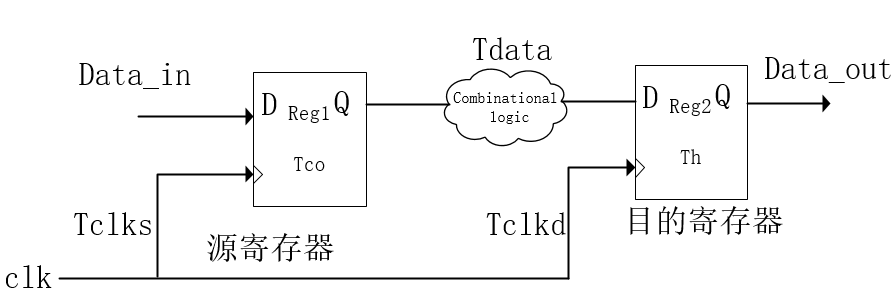

题目:最小周期计算

Tco:寄存器更新延迟。clock output delay,时钟触发到数据输出的最大延迟时间

最小时钟周期:Tmin = Tco + Tdata + Tsu - Tskew。最快频率Fmax = 1/Tmin

Tskew = Tclkd – Tclks。

题目:什么是Clock Jitter和Clock Skew,这两者有什么区别。

时钟抖动(Clock Jitter):指芯片的某一个给定点上时钟周期发生暂时性变化,使得时钟周期在不同的周期上可能加长或缩短。

时钟偏移(Clock Skew):是由于布线长度及负载不同引起的,导致同一个时钟信号到达相邻两个时序单元的时间不一致。

区别:Jitter是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。Skew是由不同布线长度导致的不同路径的时钟上升沿到来的延时不同。

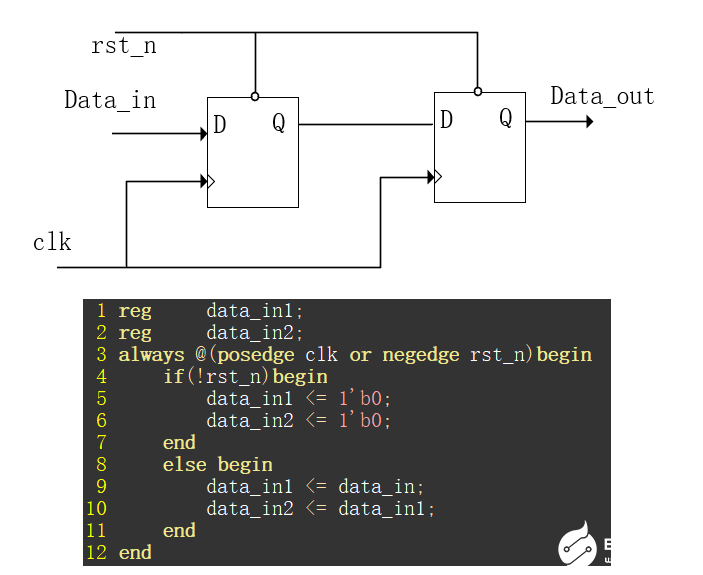

题目:什么是亚稳态,产生的原因,如何消除?

亚稳态:是指触发器无法在某个规定时间段内达到一个确定的状态。

原因:由于触发器的Tsu和Th不满足,当触发器进入亚稳态,使得无法预测该单元的输出,这种不稳定是会沿信号通道的各个触发器级联传播。

消除:两级或多级寄存器同步。理论上亚稳态不能完全消除,只能降低,一般采用两级触发器同步就可以大大降低亚稳态发生的概率,再加多级触发器改善不大。

题目:同步和异步

同步复位和异步复位的区别

同步复位是复位信号随时钟边沿触发有效。异步复位是复位信号有效和时钟无关。

同步逻辑和异步逻辑的区别

同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系

同步电路和异步电路区别

同步电路有统一的时钟源,经过PLL分频后的时钟驱动的模块,因为是一个统一的时钟源驱动,所以还是同步电路。异步电路没有统一的时钟源。

题目:谈谈对Retiming技术的理解

Retiming就是重新调整时序,例如电路中遇到复杂的组合逻辑,延迟过大,电路时序不满足,这个时候采用流水线技术,在组合逻辑中插入寄存器加流水线,进行操作,面积换速度思想。

-

时序逻辑电路有记忆功能吗2024-08-29 2886

-

逻辑电路与时序逻辑电路的区别2024-07-30 2672

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14404

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9247

-

时序逻辑电路设计2019-05-16 9271

-

什么是时序逻辑电路2019-02-26 33203

-

时序逻辑电路由什么组成_时序逻辑电路特点是什么2018-03-01 112366

-

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别2018-01-30 95129

-

时序逻辑电路概述2010-08-12 847

-

时序逻辑电路2010-08-10 956

-

同步时序逻辑电路2009-09-01 1143

-

时序逻辑电路的分析方法2009-04-07 9316

全部0条评论

快来发表一下你的评论吧 !