Verilog HDL之多路选择器设计

EDA/IC设计

1078人已加入

描述

任务描述

设计一个2选1多路选择器。进一步熟悉Verilog HDL设计流程,组合电路的设计和测试。

相关知识

逻辑原理

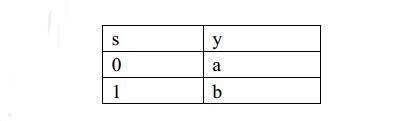

在数字信号的传输过程中,有时需要从多路输入数据中选出某一路数据,完成此功能的逻辑器件称为数据选择器,即所谓多路开关,简称MUX(Multiplexer)。2选1多路选择器能在选择信号的控制下,从2路输入信号中选择其中的一路数据送到输出口。其真值表如下表所示。

多路选择真值表

编程要求

为了完成判断学生成绩等级的任务,编写的程序要能根据s输入的值给出相应y输出的值,满足多路选择器的真值表

源代码

测试平台:EduCodermodule mux21(a,b,s,y);

input a,b,s;

output y;

reg y;

always @(a,b,s)

// 请在下面添加代码,实现当选择信号S为0时选中a,为1时选中b;

/********** Begin *********/

begin

case(s)

1‘b0:begin y = a;end

1’b1:begin y = b;end

default:begin y = 0;end

endcase

end

/********** End *********/

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- Verilog HDL

- 多路选择器

-

基于FPGA的多路选择器设计2023-05-12 2647

-

基于FPGA的多路选择器设计(附代码)2023-03-01 2200

-

组合逻辑基础之多路复用器设计2022-08-04 4310

-

4选1多路选择器是什么?2022-02-09 1093

-

Verilog HDL入门教程-Verilog HDL的基本语法2022-01-07 2389

-

Verilog数字系统设计——简单组合逻辑2(4选1多路选择器)2021-12-05 1300

-

使用Verilog语言实现持续赋值方式定义2选1多路选择器的程序2020-10-28 1335

-

8选1多路选择器电路图(五款8选1多路选择器电路)2018-04-28 143413

-

一文解析多路选择器的工作原理及电路实现2018-04-27 63751

-

八选一多路选择器Verilog代码及仿真结果MUX_82016-03-28 6370

-

多路选择器(MUX)功能实现Verilog HDL源代码2012-10-15 23114

全部0条评论

快来发表一下你的评论吧 !