电磁兼容设计要点有哪些

EMC/EMI设计

描述

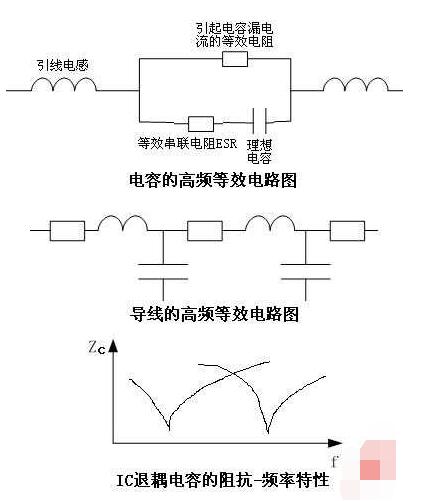

电磁兼容的问题往往发生于高频状态下,个别情况除外(Dips电压暂降与中断)除外。高频思维,总而言之,就是器件的特性、电路的特性,在高频情况下和常规中低频状态下是不一样的,如果仍然按照普通的控制思维来判断分析,则会走入设计的误区。比如:电容,在中低频或直流情况下,就是一个储能组件,只表现为一个电容的特性,但在高频情况下,它就不仅仅是个电容了,它有一个理想电容的特性,有漏电流(在高频等效电路上表现为R),有引线电感,还在导致电压脉冲波动情况下发热的ESR(等效串联电阻),(如图)。从这个图上分析,能帮我们设计师得出很多有益的设计思路。

首先,按照常规思路,1/2πfc是电容的容抗,应该是频率越高,容抗越小,滤波效果越好,即越高频的杂波越容易被泄放掉,但事实并非如此,因为引线电感的存在,一支电容仅仅在其1/2πfc=2πfL等式成立的时候,才是整体阻抗最小的时候,滤波效果才最好,频率高了低了都会滤波效果下降,由此就可以分析出结论,为什么在IC的VCC端都会加两支电容,一支电解的,一支瓷片的,并且容值一般相差100倍以上多一点。就是两支不同的电容的谐振频率点岔开了一段距离,既利于对稍高频的滤波,也利于对较低频的滤波。

其次是线缆或PCB布线的高频等效特性(如图),无论高低频,走线电阻都是客观存在,但对于走线电感,则只在较高频时候才可以显现得出来。另外就是还有一个分布电容的存在,但是,在导线附近没有导体的时候,这个分布电容有也是白搭(在离Earth距离足够远至不影响产品的EMC测试时),一般我们将考虑到骚扰源、路径、敏感源(发射/接收天线)如果在骚扰源附近有路径、敏感源、发射/接收天线的时候,我们一定要考虑耦合、也就是互感的问题存在,否则将造成预期之外的骚扰。但,很多开发电子工程师、结构工程师,都不能将其完全考虑进去。例如,最近一块带HDMI的音柱,因为内部空间问题,却不顾各电路单元之间的线缆布局,各器件布局等问题。后续在进行EMC测试的时候,出现装机前后的数据近15dB的差异存在。

另外,磁环和磁珠的高频等效特性却不得不提一下,因为磁环对高频脉动的吸波作用,与电感的表现有点类似,所以经常被认为是电感特性,但事实上错了,磁环是个电阻特性,不过这个电阻有点特别,它的阻值大小是频率的函数R(f),如此的话,在一个带有高频波动的信号穿过磁珠的时候,高频波动会因为I2R的作用而发热,将波动干扰经过电能——磁能——热能的转化过程,所以在导线上波动比较强烈的时候,磁环摸起来会是温的。

以上是EMC专业中高频思维的基础知识,有了这些,一系列的设计经验都可以迎刃而解了。

比如:IC的VCC端为何加装两只电容,一只电解电容,一只瓷片电容,是因为电容的高频等效特性,引线电感和电容的串联导致其综合阻抗随频率而变化,而在WL=(1/WC)的频率点上,是其阻抗最小的点(如图)。而且两个电容分别有自己的最小阻抗点,分别对应不同的频率点,以便于为IC不同频率范围的供电需求提供电流。

静电工作台的接地导线用宽的铜皮带和金属丝网蛇皮管,而不是黄绿的圆形接地线缆,圆形接地线缆的走线电感量偏大,不利于高频静电电荷的泄放。

线缆和线缆之间的间距不宜太近,否则会因为导线分布电容的存在而导致信号线缆之间出现串扰,当然,信号线对地线的耦合那又最好是近一点,这样,信号线上的波动干扰可以方便的泄放到地线上去。

-

电磁兼容简明教程(2)电磁兼容标准2023-12-05 2735

-

【电磁兼容知识要点分享】因芯片NC引脚线路导致RE测试超标问题案例2023-04-14 2441

-

浅谈电磁兼容及测试2023-04-13 2292

-

开关电源的PCB电磁兼容设计要点分析2021-05-26 1591

-

电磁兼容的设计要点和测试的相关内容详细说明2020-08-05 984

-

电磁兼容与电磁兼容性有什么区别2020-07-28 3791

-

医疗机械电磁兼容EMC整改的要点有哪些2020-05-31 2013

-

高频电子电路的电磁兼容设计有什么要点?2019-10-18 3278

-

电磁兼容设计基本要点2019-07-25 1792

-

电磁兼容的设计要点与屏蔽技术2019-05-30 2603

-

电磁兼容的重要性_电磁兼容技术应用2018-04-03 22502

-

PCB电磁兼容设计2016-04-25 764

-

EMC电磁兼容测试及其电路设计2012-07-19 2467

-

电磁干扰与电磁兼容技术2009-10-06 1353

全部0条评论

快来发表一下你的评论吧 !