12位并行高速A/D转换芯片THS1206的功能构造和工作原理分析

模拟技术

描述

1、概述

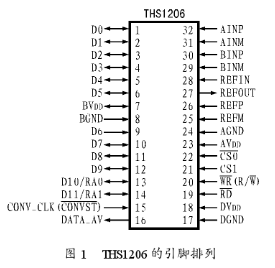

THS1206有4个模拟信号输入端,每个输入端既可作为4个单独的非极性信号的输入通道,也可作为2个差分信号输入通道,而且两种方式可同时混合使用,具体的输入通道模式可由内部控制寄存器控制。THS1206采用5V单电源供电,内置的16字深度环形FIFO可存储多次连续采集的数据,从而避免每次采集数据都要读取。且在采集多次数据之后才通知CPU读取数据,减少了CPU读取数据的中断次数,提高了系统的实时性。THS1206既可采用内部标准电压,也可采用外部输入标准电压,并可由内部寄存器控制。 图1为其引脚图,各引脚定义如下:

AINP、AINM、BINP、BINM:模拟输入通道,这四个引脚既可用做4个单独的非极性模拟输入信号,也可作为差分输入通道A和B的正负模拟信号输入端。

AVDD、AGND:ADC模拟电压和模拟地。

BVDD、BGND:FIFO的数字电压和数字地。

DVDD、DGND:ADC数字电压和数字地。

CONV CLK?CONVST?:启动转换信号输入端。

CS0、CS1:片选信号,低电平有效。

DATA AV:AD转换结束信号,数据输出有效。

D0~D9:十位双向数据线。

D10/RA0:既可作为数据线D10,也可作为内部控制寄存器的地址线RA0。

D11/RA1:既可作为数据线D11,也可作为内部控制寄存器的地址线RA1。

REFOUT:2.5V参考电压输出。

REFIN:共模输入参考电压,作为AD转换的标准参考电压,可直接将此引脚接至REFOUT引脚以输入2.5V标准电压。

REFP、REFM:外部输入参考电压的正负极接入。

RD、WR(R/W):读写控制信号。

2、内部结构及功能

2.1 内部结构

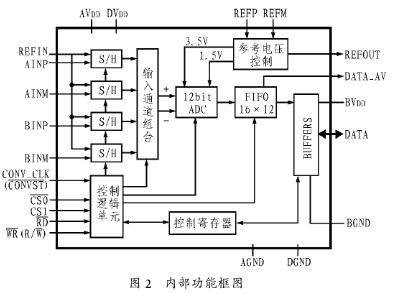

THS1206内部由采样保持器、逻辑控制单元、控制寄存器、FIFO、参考电压控制单元等部分组成。其内部功能框图如图2所示。

THS1206有4路采样保持器,可同时对4路信号进行采样保持,并按顺序依次对各通道的采样保持值进行转换。THS1206单个通道的最高采样频率可达6MSPS。同时采样多个通道的模拟信号时,其采样频率与输入信号的通道数有关。多通道采样信号的采样频率与模拟信号的输入通道数成反比。

2.2 内部控制寄存器

THS1206内置2个控制寄存器(CR1和CR0),通过向内部控制寄存器写入特定的控制命令可设定ADC的具体工作状态。D11/RA1和D10/RA0两个输入引脚可作为内部控制寄存器的地址线,通过输入来选择控制寄存器CR0或CR1。

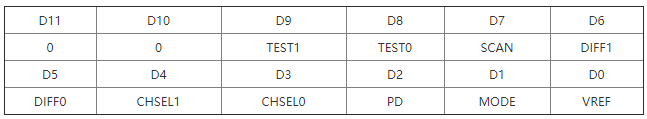

CR0各位定义如下:

TEST1、TEST0:启用测试功能,用于选择ADC 的测试电压。THS1206有VREFP、(VREFM+VREFP?/2、VREFM 三个测试电压,通过测试3个不同电压下的AD转换值来检查AD与CPU的连接是否良好,并测试AD是否正常工作。THS1206处于测试模式时,DATA AV输出无效。THS1206从测试模式返回正常工作模式后,必须重新初始化。

SCAN:自动扫描模式。就是在有多个模拟信号输入时,ADC同时采样各信号并同时保持各通道采样值,然后依次对扫描的各采样值进行AD转换。多通道输入模拟信号时都采用自动扫描模式。SCAN为1,禁止自动扫描模式,SCAN为0?启用自动扫描模式。

DIFF1、DIFF0:定义差分模拟信号输入的通道数。

CHSEL1、CHSEL0:定义ADC所有模拟信号输入的通道数。

PD:节电模式选择,PD=‘1’? ADC处于正常工作状态,PD=‘0’,ADC处于节电模式。

MODE:转换模式选择,MODE =‘0’,ADC处于连续转换模式;MODE=‘1’?ADC采用独立的转换模式。

VFEF:参考电压选择,VFEF=‘0’,选择内部参考电压;VFEF=‘1’,选择外部参考电压。

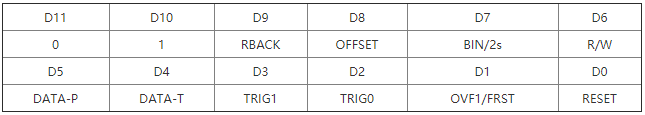

控制寄存器CR1的各位定义如下:

RBACK:调试模式 ,PBACK=‘0’,ADC处于正常工作状态,PBACK=‘1’,ADC处于调试状态。当ADC处于调试状态时,可依次读取内部控制寄存器CR1和CR0的值。

OFFSET:零偏移补偿模式,OFFSET=‘0’,ADC处于正常工作状态;OFFSET=‘1’,ADC处于校准补偿模式。ADC采用零偏移补偿模式时,输入模拟信号置为零电平并进行转换?转换值(即零偏移补偿值)存入内部补偿寄存器;而当ADC正常工作时,其转换数值减去零偏移值以得到校正后的AD转换值。通过零偏移补偿有利于提高信号采集的准确度。

BIN/2s:输出数据表示模式,BIN/2s=‘0’,输出数据以补码形式表示;BIN/2s=‘1’,输出数据以二进制码表示。

R/ W:读写选择,R/ W为1时,WR为读写信号,RD输入引脚禁止。R/ W为0时,RD输入引脚为读信号,WR输入引脚为写信号。

DATA P:DATA AV极性控制,DATA P为1时,高电平有效,DATA P为0时,低电平有效。

DATA T:DATA AV输出方式控制,DATA T为0时,DATA AV为电平触发;DATA T为1时,DATA AV为边沿触发。

TRIG1、TRIG0:设置FIFO触发门限,通过TRIG1和TRIG0 设置不同输入通道时FIFO的触发门限。

OVFL/FRST:读写显示信号,当作为读信号OVFL时,显示FIFO的溢出状态,OVFL为1时, 表示FIFO 没有溢出,OVFL为0时,FIFO溢出。当作为写信号FRST时,复位FIFO,对FRST写入1可复位FIFO。

RESET:复位信号,对该位写1,将对内部控制寄存器CR1、CR0设置复位值,同时也对FIFO和补偿寄存器复位。

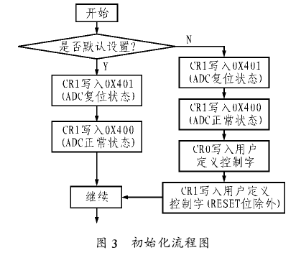

应当注意的是,在ADC正常工作前,必须对其内部控制寄存器初始化,并设定其具体的工作模式。初始化的流程如图3所示。

2.3 FIFO的使用

THS1206内置一个灵活的环形FIFO,AD转换数据可直接写入FIFO?最多可存入16个字。使用内部FIFO 时,ADC无需每采样一次都产生中断,因而可减少微处理器读取采样数据的中断次数。为了控制FIFO的读写,FIFO用其设置的读指针来指示下一读取数据的位置?而用内置的写指针来指示最后一次采样数据放置的位置。若有多个模拟信号输入,各个通道的转换值依次写入FIFO中。通过内部寄存器控制FIFO的触发门限,触发门限设定存入采样数据的深度,存入数据达到此深度时,DATA AV有效。

2.4 AD转换

THS1206通过内部控制寄存器来设置ADC的转换模式是单独转换模式,还是连续转换模式。单独转换模式时,启动内部振荡电路产生内部时钟。在外部输入CONVST的下降沿触发ADC采样,并保持各模拟输入信号,同时依次对各信号进行转换并存入FI-FO。AD转换开始到DATA AV有效的时间段为转换时间,转换时间大小为ADC内部振荡器产生的内部时钟和FIFO触发门限的乘积。当转换时间达到FIFO的触发门限时间时,数据存入FIFO,此时,DATA AV输出有效,以通知微处理器读取数据。输入不同模拟信号通道时,FIFO的触发门限不同,通过内部控制寄存器CR1中的控制位TRIG1、TRIG0可设定具体的FIFO触发门限。相邻CONVST的输入时间应足够长,以保证ADC在此时间内完成AD转换。

ADC处于连续转换模式时,内部振荡电路关闭。外部时钟信号可输入CONV CLK引脚,并在CONV CLK的上升沿触发AD转换,以便ADC依次采集保持各输入信号。转换时间为外部输入时钟信号和FIFO触发门限的乘积。经过触发门限时间后,其转换值存入FIFO,DATA AV有效,以通知CPU读取数据。此时CPU读取的数据为一段AD采集数据,数据个数等于触发门限值。

3、采集系统构成

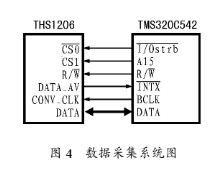

利用THS1206和TMS320C542构成的数据采集系统如图4所示,ADC作为DSP的I/O存储空间。通过设定控制寄存器使ADC处于连续转换模式,DSP的缓存串口输出时钟作为ADC的输入时钟,并用其上升沿触发ADC转换。DATA AV连接TMS320C542的外部中断引脚,ADC转换数据存入FIFO,在溢出时发出中断,然后由DSP响应中断并读取I/O空间即FIFO的数据。

责任编辑:gt

-

THS1206采样并非连续,请问这是为什么?2025-02-13 340

-

AD转换器THS1206在红外成像系统中的应用2025-01-21 575

-

THS1206THS1206应用问题?2025-01-20 418

-

THS1206模数转换器(ADC)数据表2024-07-15 479

-

高速D/A转换芯片MX7541的工作原理是什么?2021-04-14 1581

-

可编程多路A/D转换芯片THS1206的原理及应用,总结的太到位了2021-04-12 1586

-

THS1206 12 位 6MSPS ADC,具有四通道 (配置),DSP/uP IF,集成 16x FIFO、信道自动扫描功能和低功耗模式2019-04-18 606

-

THS1206AD转换器的数字和模拟部分的使用中的指导详细概述2018-05-29 1485

-

同步THS1007、09和THS1207、09、06数据转换器的数据输出所需的步骤2018-05-24 1426

-

数模模数转换芯片THS12062017-02-28 1181

-

THS1206, THS12082. THS10064, T2010-06-05 1268

全部0条评论

快来发表一下你的评论吧 !