采用交流耦合仪表放大器实现共模抑制比性能的设计电路应用

模拟技术

描述

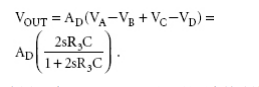

现代的电池电压为3~3.6V,这就要求电路能在低压下高效工作。本设计提出的一种交流耦合仪表放大器,具有很大的共模抑制比(CMRR)、很宽的直流输入电压容限以及一阶高通特性。这些特性大多是由高增益第一级设计提供的。电路采用普通参数值和普通容限的元件。图1a示出简化的放大器电路。该电路的一般原理是电容器C和电阻器R3对输入信号进行缓冲和交流耦合。第二级由两个差动放大器AD组成。每个差动放大器放大差动输入信号的一半。求和运算可以得到求VOUT的如下公式:

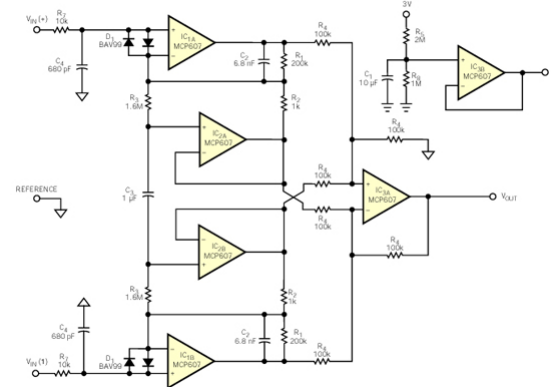

在图1a中, VA、VB、VC和VD是两个差动放大器的输入电压,AD是增益。时间常数2R3C决定高通的截止频率。图1b示出了详细的电路。 输入级由运算放大器A1、A2、A3和A4组成。A1和A2是主要的增益级。因为A1和A2的反相输入端和非反相输入端的电位相同,所以A1和A2的输入电压都供给电阻器R3。缓冲器A3和A4与电阻器R2一起,可使R3的电流放大1+R3/R2倍,因为R2和R3都连接到相等的电位。这种电路结构是本设计的核心。电容器C上的电压没有交流分量,而A1和A2各放大差动输入交流信号的一半。C滤除出现在A3和A4输出端的输入直流分量。第二级是一个增益为1的、四个输入加法器—减法器级。它能实现上述的公式,式中的AD等于1+R1/(R2||R1) 。假定R3》》R2, AD=1+R1/R2。

图1 电容器C对简化的放大器电路(a)进行交流去耦;详细的电路(b)采用几个增益级和一个加法器—减法器级。

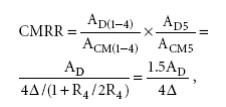

第二级的另一种可能的实现方法是采用两个差动通道ADC,产生一个数字化的VOUT,供微处理器处理。如果使用一个±5V的电源,则就有可能利用一块芯片上的两个差动放大器,如INA2134来获得VOUT。你可以计算出共态抑制比的最小值:

式中AD(1-4) 分别是放大器A1到A4的差动增益,ACM(1-4) 分别是这四个放大器的共模增益,AD5是放大器A5的差动增益,ACM5则是A5的共模增益。Δ是电路中电阻器R4的容限。一个非常重要的参数是运算放大器的输入失调电压,对于A3和A4来说尤其是这样。A1和A2的失调电压不会引起差错,因为它们只增加输入信号的直流分量,而电容器C则将这些直流分量去掉。

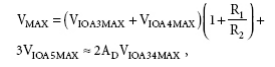

由运算放大器失调电压引起的最大输出电压误差为:

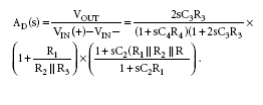

式中,V10MAX为相应运算放大器的最大失调电压。在选择运算放大器时,你应该注意以下两点:A3、A4和A5应为低失调电压和高共模抑制比(CMRR)的运放,而A1和A2应具有很高的开环增益、共模抑制比(CMRR)和增益带宽乘积。图2示出了一种实用的放大器电路。电源是一块3V锂电池。你可以选用几种运算放大器,如MCP607系列或OPA2336系列。由于输入共模电压范围的缘故,你要把信号地电位调到电源电压的三分之一。二极管D1能防止电路闭锁。R7-C4网络在输入端滤除射频噪音。 你可以根据下述的考虑因素推导R7-C4网络的参数:如果R7C4=(R1||R2||R3)C2~R2C2,则放大器传递函数中的高频零就会消去:

该电路具有以下的优点:

● 第一级确保总增益,从而在第二级不采用高精度电阻器的情况下也可提供高共模抑制比(CMRR);

● 只要把确定低频的RC网络连接到两个放大输入信号的运算放大器的反相输入端,该电路就不需要另外的输入缓冲器;

● 该电路利用具有普通参数值和容限的无源元件就可提供标准的一阶高通特性;

● 采用3V电源,差动输入信号范围可高达2V;

● 该电路消耗的电源电流和功率都很小,分别为120μA和0.4mW左右。

责任编辑:gt

-

放大器共模抑制比参数定义及影响电路共模抑制的因素分析2020-10-14 13799

-

高共模抑制比(CMRR)仪表放大器电路原理图讲解2023-08-09 6603

-

求分享仪表放大器共模抑制比的测量方法?2024-08-01 665

-

如何测定仪表放大器的共模抑制比?2024-09-03 845

-

关于仪表运放共模抑制比的问题2018-08-03 2374

-

放大器的电源抑制比和共模抑制比2018-09-19 6441

-

仪表放大器AD620的共模输入范围超过电源电压会影响共模抑制比吗?2023-11-15 648

-

具有高共模抑制比的仪器用放大器电路图2009-04-01 1294

-

放大器的共模抑制比的定义2009-04-22 2604

-

仪表放大器的特点和电路设计原理2010-03-10 3585

-

共模抑制比和输入阻抗高的仪表用差动放大电路2010-04-27 3782

-

仪表放大器共模抑制比怎么计算?2023-09-05 4823

-

带恒流源的差分放大器如何提高共模抑制比的?2023-10-23 3280

-

同相比例放大器为什么对共模抑制比要求高?运放的共模抑制比如何仿真?2024-01-26 3840

-

仿真分析仪表放大器共模抑制比2025-12-25 700

全部0条评论

快来发表一下你的评论吧 !