基于FPGA解决方案的SOPC技术实现二维条码识别系统的设计

可编程逻辑

描述

二维条码PDF417中PDF为Portable Data File的缩写,每一个PDF码的储存量可高达1 108字节,若将数字压缩则可存放2 729字节。作为一种新的信息存储和传递技术,PDF417具有成本低、信息可随载体移动、不依赖于数据库和计算机网络、保密防伪性能强等优点,广泛应用在国防、公共安全、交通运输、医疗保健、工业、商业、金融、海关及政府管理等领域,PDF417码的例子如图1所示。

1 系统总体设计

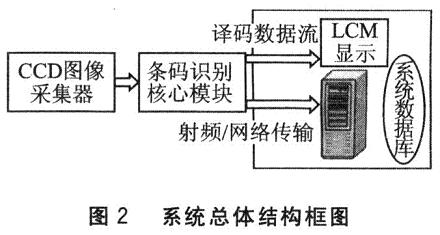

本系统在FPGA上使用SOPC技术来实现无线手持二维条码识读器,与传统一维条码识读器最大的区别在于完全脱离后台数据库,以及在高达50%破损率的情况下能够进行高效率识别。

SOPC技术是一种基于FPGA解决方案的SOC,由美国Altera公司于2000年提出。基于SOPC平台的开发结合了FPGA灵活可编程与片上。NioslI软核处理器的用户可配置等特点。在实现某功能时,通过在NiosII处理器下编写C程序运行,也可以使用硬件模块来加速。本系统综合两种实现思路,采用高性价比的Cyclone II EP2C35系列FPGA实现,系统总体结构如图2所示。

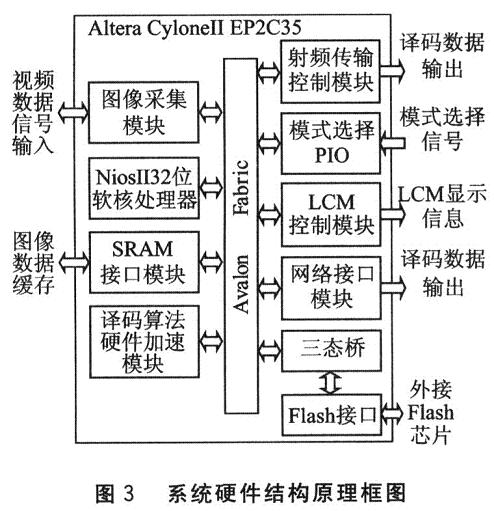

整个系统由低到高分为三个层次:条码识别的硬件平台、μC/OS—II操作系统、条码译码核心算法。最底层硬件平台采用Altera公司的Cylone II EP2C35与ADI公司的视频解码芯片ADV7181B,具有8 MB的Flash存储器,1.MB的SRAM等外设;中间层μC/OS—II操作系统提供任务调度和设备驱动,以及提供各种中断来实现对外界请求的响应,如模式切换、LCM.显示、射频传送等,有效地提高了系统运行速率;最顶层条码译码核心算法包括了对条码图像的预处理和对译码数据的RS纠错,采用C语言在NiosII的集成开发环境中(IDE)实现。

1.1 系统硬件结构

系统通过配置视频采集芯片ADV7181B,通过图像采集子系统将CCD采集到的条码数据存储在SRAM中后,产生硬件中断,处理器响应中断,Nios对SRAM中的数据进行图像预处理、译码及纠错,通过译码算法硬件加速模块对耗时较多部分算法进行优化,在实现条码数据译码及纠错后,产生射频传送和LCM显示中断,进入中断程序将译码数据通过射频传输模块发送到上位机,并且在LCM实时显示。其硬件平台结构原理如图3所示。

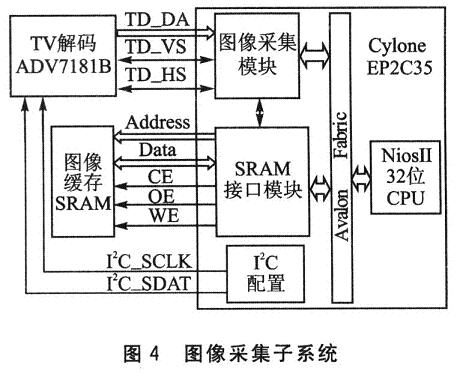

1.2 图像采集子系统

由于本设计采用的是灰度图,因此图像采集子系统的主要功能是:配置采集芯片,从解码芯片读出数据流,根据行场同步信号对数据流进行分离,提取出亮度信号,并将采集到的亮度信号通过乒乓缓存存入SRAM中。

在设计中,采用ADI的解码芯片ADV7181B进行图像信号的数模转换,FPGA中的I2C模块是作为主设备来对ADV7181B进行配置的,而ADV7181B作为从设备来接受I2C总线传来的数据,实现芯片的初始化、寄存器的配置等。图4中T_DA为数据信号,TD_VS为场同步信号,TD_HS为行同步信号。

系统上电时,I2C配置模块将对ADV7181B的内部寄存器进行配置,ADV7181B将模拟信号转换为Y:U:V为42:2:2的8位CCIR656数字信号,其中输出的时序包括行场同步、行场消隐、行频场频及场识别等信号。

CCD摄像头采集的图像实际尺寸为768×576像素,每帧图像由奇场数据和偶场数据交错组合而成,奇场数据与偶场数据在时间上是先后输入的。本设计使用的是320×240的液晶显示屏,在处理过程中也采用的是320×240的图片格式,所以要对摄像头采集的图片进行提取。在设计中仅采奇场数据的中间240行,并对每行中间的640个数据每两个像素抽取一个像素,从而得到符合系统要求的图像大小。由于一帧图像的奇场数据与偶场数据实际上非常接近,而每行的相邻两个像素值也几乎没有差异,因此可以得到原输入图的缩小图像而不会有失真。

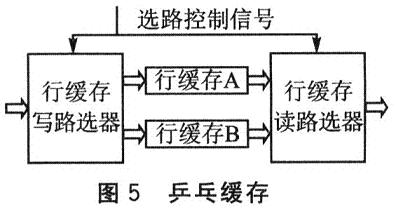

图像存入SRAM采用了乒乓缓存,如图5所示,是为了防止写出速度快于写入速度而导致出现错误数据。采用两个行缓存进行乒乓切换,在数据提取子模块向行A写入数据时,数据写出子模块读取行缓存B中的数据输出到总线;在对下一行进行采集时,对行缓存A读数据,对行缓存B写数据。因此行缓存写路选器与行缓存读路选器在同一时刻选通的一定是不同的行缓存。

2 条码识别核心算法

条码译码主要流程是首先对条码进行自适应二值化,然后对条码进行定位、旋转、分割。分割出单个码字后,通过边缘检测,得到条码条空序列模块宽度后,再进行纠错解码。

传统条码识别算法在对条码定位时多采用Hough变换,通过Hough变换提取条码图像中的直线倾角来旋转条码。但是Hough变换的大运算量并不适用于实时性要求高的的嵌入式设备。笔者结合PDF417条码自身的特点,采用4点定位的方法来分割条码,有效提高条码识别速度。核心算法流程详细步骤如下:

(1)条码定位

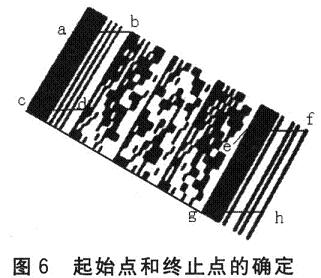

实际采集条码时会出现各种倾斜,如图6所示。如何定位条码是关键的问题。可以利用条码起始头特有的比例来定位。按照国标的定义,PDF417二维条码的起始符黑白条空比是81111113,终止符黑白条空比是711311121。扫描图像的每一行,分别匹配起始符和终止符的条空比。考虑到条码采集过程中,边缘受高斯点扩展函数的影响,只要黑白条空比例的误差不超过三位,可近似认为符合比例。标记所有符合起始符条空比比例条码线段,可以得到4个控制点a、b、c、d,用同样的方法可以寻找符合终止符条空比的条码线段,确定点e、f、g、h。判断a、c、e、g是否为正确控制点的标准是,平行边长度误差在5个像素点内,且相邻边角度为90°,其误差角度为2°。

(2)行条码分割及行高确定

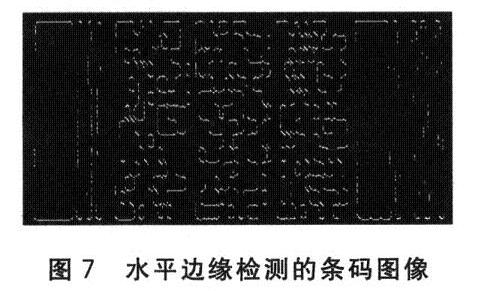

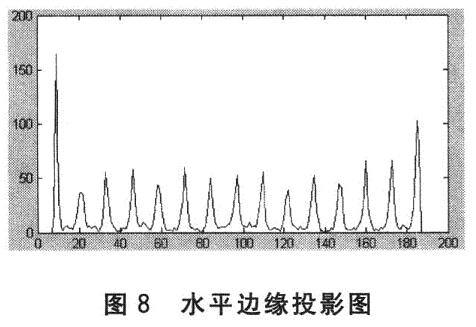

由于PDF417条码是层叠式条码,在对单行条码码字进行识别时,必须得到条码的行数,然后分离出每一行。首先对条码使用Sobel算子进行水平边缘检测,如图7所示,然后向水平方向投影,如图8所示。

已知p(x)对应投影的峰值,也就条码的边界,通过对投影下来的每个值求一次差分▽ p(x),然后逐个判断各个差分值,如果连续两个投影的差分值前一个是负数而后一个是0或者正数,则说明此点是峰值。峰值处的坐标即为条码分层的地方,考虑到条码层与层连接的地方在二值化时会出现噪点,则取每层条码图像中间的50%作为有效图像。

(3)码字识别

分割出单个码字后,得到条空的像素个数,记为{M1,M2,…,M8},因为4个条和4个空的总模块数为17,可以根据式(1)得出条模块数的集合{T1,T2,T3,T4)。同样,用Ki替代式(1)中的Ti,可得到空模块数的集合{K1,K2,K3,K4}。

因PDF417条码用了三个簇的数据来组成一个条码,三个簇的数据量较大,且每个簇中的数据与条空比无一致对应关系,所以就涉及把条空比转换成条码数据的问题。本算法采用的解决方案是:用哈希算法来查找:

F=Z×1400+K2×216+T3×36+K4×6+T (2)

式(2)中Z为空1模块数和条2模块数的组合,再利用F的值进行查找,实现数据流的译码。数据流译码不是本文重点,这里不再详细阐述。

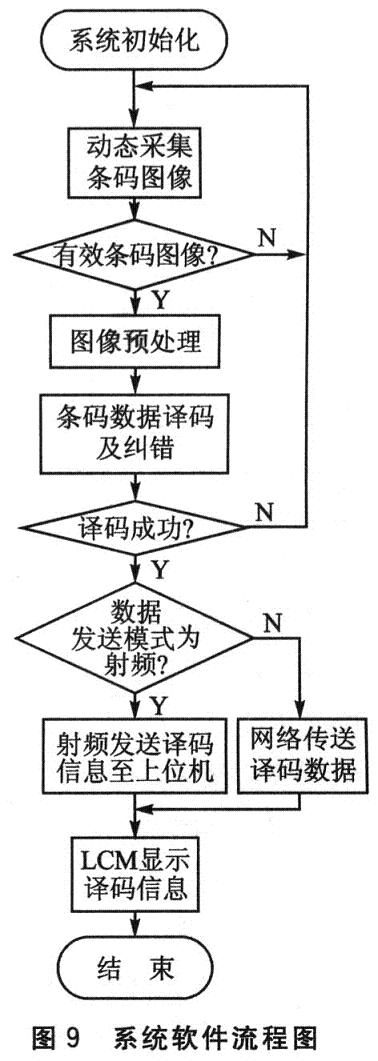

3 系统软件设计

系统软件是在Nios II的μC/OSII操作系统下进行C语言编程的。系统初始化主要包括对采集芯片、射频传输控制模块、网络接口的初始化,整个系统动态扫描条码图像和实时译码。系统主要流程如图9所示。其中,系统初始化时利用函数IOWR(SIGNAL_CAP_O_BASE,O,1)将采集模块全局信号复位,然后使用函数alt_irq_register。(SIGNAL_CAP_0_IRQ,NULL,sig_cap_irq_proc)来建立一个用户中断程序,对按键中断响应进入中断服务程序sig_cap_irq_proc,向摄像头发送采集指令。当采集模块完成一幅条码图像采集后,产生一个硬件中断,将标志FLAG置1。当主循环程序判断FLAG为1时,就可以从外扩的SRAM中将图像数据读入SDRAM中,接着进行图像预处理和译码,其中包括用自定义用户指令和硬件模块实现的一些运算量大的部分。射频传输与NiosII的PIO口相连,通过函数IOWR_ALTERA_AVALON_PIO_DA_TA来实现。

4 实验与分析

本识别系统工作频率为100 MHz,图像采样分辨率为320×240,一幅条码图像识别时间为60 ms。本系统有如下几个特点:

①利用PDF417码本身的特点来定位分割条码,与传统的条码定位分割算法相比,大大提高了条码识别速率。传统二维条码定位分割多采用Hough变换来确定条码倾斜角度,不能满足手持式嵌入式条码识读器的实时性要求。

②在FPGA中嵌入NioslI软核处理器,简化硬件设计,同时使系统更加稳定。FPGA的可重配置以及SOPC的可裁减使系统具有很高的资源利用率,而且方便升级和维护。

③利用自定义模块、自定义指令、C2H硬件加速等方法刮对部分耗时算法进行优化,大大提高了整个系统识别速率。

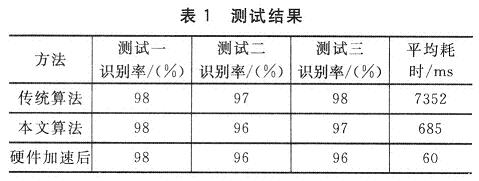

笔者针对不同环境下采集的300幅条码图像进行了三次测试:第一次是在条码无破损的情况下,第二次是在条码有5%破损和污染的情况下,第三次随机识别100幅条码。本文所采用的算法平均识别率达96.7%,耗时60ms,如表1所列。

结 语

二维条形码诞生后,条码技术的应用领域更加广泛,不仅应用于物流运输,还渗透到生产、生活的各个领域。本文介绍了一种基于SOPC的二维条码识别系统的设计,提出了一种软硬件综合的解决方案,由于涉及底层的硬件系统设计和相应的软件设计,在系统性能优化方面有着很大的空间。

责任编辑:gt

-

基于FPGA的车辆牌照识别系统的设计2012-08-11 9222

-

如何利用SOPC去设计二维条码识别系统?2021-04-08 1673

-

二维条码的识别方法2009-08-12 1425

-

二维条码技术在路桥ETC系统中的应用2010-01-27 765

-

二维条码的编解码及系统实现2011-09-20 1003

-

手机二维码识别系统的设计与实现.pdf2016-06-03 999

-

基于ARM的二维条码识别与语音播报研究2017-12-20 944

-

ATK QR二维码和条码识别库的模块资料和使用C语言代码合集免费下载2019-09-17 1888

-

扫码头、条码识别模块、二维条码扫描模块在物联网领域中的应用2023-02-27 1688

-

条码识别模块为各行各业带来了高效精准扫码解决方案2023-03-06 1735

-

二维码扫码读头有什么功能?如何选择二维码读头?2023-03-30 3091

-

条码识读器支持嵌入式应用,了解几款高性价比的嵌入式二维条码识读器2023-04-26 1919

-

工业视觉在条码/二维码识别领域的应用2024-11-18 1420

-

GM861条码二维码识别模块用户手册2025-07-09 472

-

扫描条码模块、二维码模块,广泛应用于定制的手持设备2025-08-18 761

全部0条评论

快来发表一下你的评论吧 !