采用串行外设接口的数据转换器双线控制电路的设计

模拟技术

描述

多数现行微处理器、DSP、现 场可编程门阵列都集成了硬件和软件资源,它们支持两种常见接口标准——SPI(串行外设接口)和I2C /SMBus——中的一种或两种。两种双线接口标准都有几个关键缺点。例如,I2C在标准模式、快速模式、高速模式中的吞吐速率分别是 100kbps、400kbps或3.4Mbps,因此限制了快速外设数据转换器的采样速率。不包括成帧比特和开销比特的话,一个 100ksps的12比特ADC在接口上必须以至少1.2Mbps 来传输数据,只有I2C的高速模式才支持这个速度。许多处理器和控制器目前不提供 I2C高速模式,因此不能支持快速数据转换器。

I2C的一个主要优点是减少了主机至目标的互连线路数量。主机控制器只使用两根线,外加接地,就能应付目标器件和交换数据,而 SPI 需要三根线——数据、时钟、芯片选择——外加接地。多个 SPI 目标器件能共享数据和时钟线路,但是每个器件都需要自己的专用芯片选择线路。

由于人们始终需要更高的采样速率和分辨率,因此I2C的有限速度也许会限制它在某些应用中的使用,这迫使设计师选择SPI。然而,SPI需要主机控制器上有一根额外的I/O引脚。在无法提供额外引脚,但是应用需要快速SPI总线转换器的情况下,你可以利用图1中的技巧。

例如,德州仪器公司的 ADS7816包含200ksps的12比特采样ADC,它需要3Msps的性能,从而以200ksps速率连续采样(参考文献1)。如果选择ADS7816的低电平有效CS(芯片选择)引脚,就会引起一个转换周期。在数据传输期间转换并保持CS为低电平之后,CS在传输数据之后返回高电平,完成整个过程。

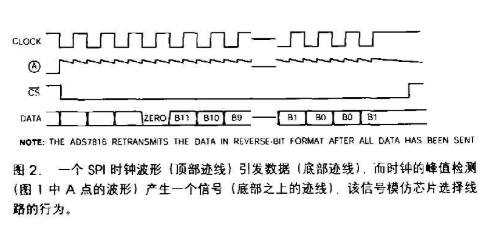

当时钟线路变为低电平时,它还使CS保持低电平状态。峰值检测器(由D1、R1、C1组成)的时间常数确保了CS不会变为高电平,直到时钟线路保持高电平的持续时间超过一个时钟周期(图2)。虽然时钟线路转换并从 IC2取回数据,但CS保持为低电平,并且,在数据取回任务完成时,时钟线路变为高电平,CS随后也变为高电平,使电路为另一个转换周期准备就绪。

由于C1必须在转换周期结束时放电,因此控制器应该延迟下一个转换周期的启动,直到C1完全放电。仔细选择R1和C1的话,就会使延迟缩短到最少的3个时钟周期。另外,在下一个时钟脉冲到达并刷新电容器的电压之前,C1两端的电压一定不能降到逆变器IC1B的输入阈值以下。逆变器IC1A的输出电压和电流能力会影响C1的再次充电时间,而R1和IC1B的输入阻抗会影响放电时间。为了确保实现耐用的设计,应该包含元件的公差和温度系数,以及逻辑输入和输出阈值的变化情况。

责任编辑:gt

-

简易USB与LVDS接口转换器2018-11-22 7164

-

数据转换器串行接口JEDEC标准十问十答2018-12-10 2793

-

浅析高速转换器转FPGA串行接口2018-12-25 2527

-

互连数量极少的双线串行接口产品2019-05-05 2071

-

高性能串行接口模拟多路转换器ADG731/ADG725的特点2019-05-24 2663

-

用于高速数据转换器的串行接口有哪些选择?2021-04-09 1214

-

20位Σ-Δ串行AD转换器AD77032009-04-27 761

-

串行外设接口SPI2009-09-15 454

-

高速DSP串行外设接口设计2010-01-20 487

-

串行数据转换器接口2010-01-04 2180

-

理解ATE SPI (串行外设接口)2010-01-26 3202

-

dsPIC33E/PIC24E器件之串行外设接口(SPI)2018-06-03 1687

-

dsPIC30F系列参考手册之串行外设接口(SPI)2018-06-22 1206

-

PIC24F系列参考手册之串行外设接口(SPI)2018-06-24 1141

-

DC-DC转换器控制电路大约多少钱?2024-05-11 1671

全部0条评论

快来发表一下你的评论吧 !