基于AD9776/78/79 TxDAC系列实现生成差分波形的控制功能

模拟技术

描述

高速 DAC,比如模拟器件(Analog Devices)公司的 AD9776/78/79 TxDAC 系列,能提供差分输出,但对于低端交流电应用或高精度电平设置应用,配备差分转换电路的单端电流输出 DAC 提供了一种新颖的方法来生成差分波形控制功能。图 1 中的基本电路组合了电流输出 DAC(即 IC1,如 8 位AD5424 DAC)和一个单端至差分运算放大级IC2、IC3A、IC3B——来产生要求的输出。对于双电源应用,可选择 DAC 的单极工作模式来达到 DAC 的最优性能。DAC 利用单一运算放大器提供了双象限倍增或单极输出电压摆动。DAC 的输出需要缓冲器,这是因为对施加到 DAC 输入端的代码进行改变,就会改变它的输出阻抗。

以下公式定义了电路的输出电压:VOUT=-VREF×(D/2N),其中 N 定义了输入位数,VREF 是基准电压,D 是二进制代码的十进制等价值。为了生成正共模电压,可把负电压用作 DAC 的基准电压。DAC 的内部设计可容纳 -10 V ~ +10V 的交流电基准输入信号。在这种模式中,当您依靠一个 5V 电源对DAC 供电时,它为四分之一满刻度代码变化提供 5Msps 最大更新速率。只有当您的应用需要可调增益时,才使用电阻器 R1 和 R2。

单端至差分级由两个交叉耦合运算放大器组成,电阻器 R5 和 R6 配置成一个单位增益跟随器。为了实现对称电路,各输出还作为单位增益反相器通过 R7 和 R8 互相驱动。向运算放大器 IC2 的正端子施加的电压设定了电路的共模电压。电阻器 R3 和 R4 控制着差分电压的大小。请注意应用的输出负载要求以及运算放大器的输入电压和输出电压能力。

对于单电源应用,可在反向模式中使用电流输出 DAC,其中,把基准电压 VIN 施加到 DAC的IOUT1引脚,并从 DAC 的 VREF 端获得输出电压(图2)。在这种配置中,正基准电压产生正输出电压。该电路不使用 DAC 的反馈电阻器 RFB,并且它与 IOUT1 之间的连接防止了杂散电容效应。DAC 的基准输入有一个阻抗,该阻抗随施加的代码而变化,因此需要一个低阻抗源。

请注意:DAC梯型电路中的各开关不再具有相同的源极至漏极驱动电压,这又把输入电压限制在低电压。结果,各开关的接通电阻各有不同,并降低了DAC的线性度。另外,该模式还把最高更新速率限制在1.5Msps。您可以使用双运算放大器的若干部分来缓冲 DAC 的输入,并放大 DAC 的输出电压(图 3)。该电路的预定应用决定了您对配套放大器的选择。对于低速的精密应用,运算放大器需要很低的输入偏置电流和输入偏移电压,以避免 DAC 的 DNL(差分非线性)性能的恶化。例如,AD8628 在室温和5mV最高输入偏移电压下提供 100pA最大偏置电流。运算放大器的低频噪声在精密电平设置应用中很重要,而AD8628规定的0.1 Hz ~ 10Hz噪声低于 0.5mV p-p。它的满摆幅输入和输出使它非常适用于单电源电路。

对于高速系统应用,运算放大器的转换率不得主导 DAC 的转换率。运算放大器的带宽必须宽到足以驱动反馈负载,并且不得限制电路的总带宽,而 DAC的输出电压稳定时间应该决定电路的最高更新速率。图1和图2中的AD8042提供170MHz 带宽和 225V/ms转换率,使它很容易实现这些结果。其它高速运算放大器,如 AD8022、AD8023、AD8066,在本应用中也工作得很好。

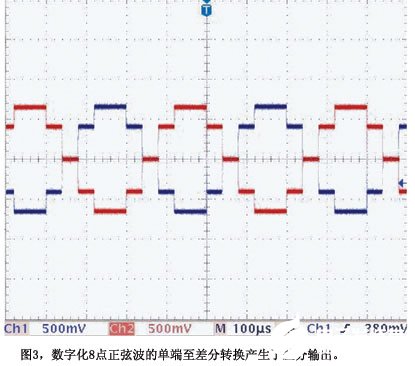

DAC 只消耗 0.4mA 电源电流,因此运算放大器主导着电路的功耗。为了尽量缩小电路在 印制电路板上的占位面积,您可用单一 AD8044 四芯运算放大器来代替图 2 中的所有四个运算放大器。在 1.4V 共模电压和 0.6V 差分信号下,数字化 8 点正弦波的单端至差分转换产生了差分输出(图 3)。

责任编辑:gt

-

LM78 79系列在Altium哪个库中2011-10-12 15666

-

如何通过LABVIEW实现两个波形的乘、除、差分、微分?2020-05-11 3356

-

什么是高压差分探头?高压差分探头具有哪些功能2021-11-05 3526

-

使用AD8138实现单端转差分功能的疑问2023-11-27 1071

-

AD9776/AD9778/AD9779,pdf datasheet (Digital-to-Analog Convert2009-09-18 982

-

三端稳压器(78、79系列)管脚序号判断技巧2006-04-16 8307

-

AD9776_datasheet2015-11-10 577

-

三种SPWM波形生成算法的分析与实现2016-08-24 1096

-

AD9776/AD9778/AD9779:双12/14/16位、1 GSPS数模转换器数据表2021-04-29 1038

-

如何生成PWM波形呢?2023-02-14 6320

-

使用STM32微控制器系列中的DAC生成音频和波形2023-09-21 624

-

差分晶振的输出波形解析2024-01-25 2549

-

生成SPWM波形的方法2024-02-06 4984

-

STM6717/18/19/20及STM6777/78/79/80系列电压监控器:设计与应用指南2026-01-18 694

-

深入解析AD9776/AD9778/AD9779:高性能数模转换器的卓越之选2026-04-16 366

全部0条评论

快来发表一下你的评论吧 !