12b双通道模数转换器AD9238的功能特点及应用系统设计

模拟技术

描述

AD9238是美国模拟器件公司(ADI)在2002年8月推出的业界最快的12b双通道模数转换器。AD9238与ADI公司的驱动运算放大器配合可以给医疗成像、多通道通信等高端应用提供完整的解决方案。

AD9238分3种型号,采样率最高分别可达20 MS/s,40 MS/s和65 MS/s。他可以提供与单通道A/D转换器同样优异的动态性能,但是比使用2个单通道A/D转换器具有更好的抗串扰性能。

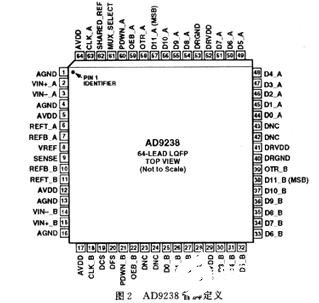

AD9238三种型号的功耗分别为180 mW,330 mW和600 mW,只有同类A/D转换器的1/2。他采用64脚LQFP封装(尺寸只有9 mm×9 mm),非常适合在对尺寸要求严格的场合中使用。

1、AD9238的主要特点:

集成了2个12 b的单通道A/D转换器AD9235(20/40/65 MS/s);采用单一3 V供电(2.7~3.6 V);RSN=70 dBc(最高采样频率时,AD9238-65,此值为典型值);RSFD=85 dBc(最高采样频率时,AD9238-65,此值为典型值);ENOB=11.3 b(有效位数,典型值);差分输入时有500 MHz的3 dB带宽;有片上的参考电压和SHA;1~2Vp-p 的模拟输入范围;输出数据格式为偏移二进制码或者是二进制补码;AD9238-65还带有片上时钟占空比调整电路;通道间串扰为-80 dBc@fIN=10 MHz。

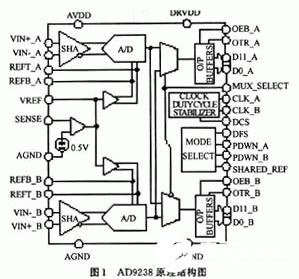

2、芯片内部结构及原理说明

如图1所示,AD9238由2个基于AD9235转换器核的高性能A/D转换器组成。这2个ADC通道除了共用内部的电压参考源VREF,其他基本是独立的。每个ADC通道都包含有1个前端采样保持放大器(SHA)和1个流水线ADC。该流水线ADC分为三级,第一级是1个4 b的闪速(Flash)ADC,第二级是8个1.5 b的闪速ADC,第三级是1个4 b的闪速ADC。每一级都提供有充分的位数重叠来纠正前一级的错误,每级的量化输出再加上数字误差校正可以保证最后得到12 b的有效位数。流水线的结构允许前一级在完成某一采样工作后进行新的采样,而后一级仍在进行先前的采样工作。

流水线的每一级(除了最后一级)都有一个低位数的DAC和一个乘法器来驱动下一级。乘法器用闪速ADC的输出来控制开关电容DAC。DAC的输出减去输入信号再经放大后送入下一级流水线,乘法器这一级也叫做乘法DAC(MDAC)。每一级有1 b用来对前一级的错误进行数字校正。最后一级只包括一个闪速ADC。冲器。输出缓冲器单独供电,这样可以方便地对输出电压进行调节。AD9238有64个管脚,管脚分布如图2所示。

3、AD9238应用系统设计

A/D转换器的应用属于数字模拟混合电路设计,以下对AD9238应用系统设计时需要重点考虑的几个问题进行详细论述。

3.1 模拟输入

AD9238的模拟输入端(管脚2,3,14,15)是一个差分开关电容电路(SHA),他可以接收1-2Vp-p范围的单端或者差分模拟输入信号。

SHA电路根据时钟信号选择处于采样模式或者是保持模式。在SHA电路的每个输入端串接一个小的电阻可以减小从输出级驱动源产生的瞬时峰值电流,并接一个电容可以提供动态负载电流。这个无源网络组成了一个输入低通滤波器。

REFT和REFB分别提供了内部正负差分电压参考。 他们定义了ADC内核的电压范围,有关的关系如下:

内部电压参考(VREF)的范围是0.5~1.0 V,按照上述关系,外部电压输入范围为1.0~2.0 V。当AD9238工作在最大的输入范围时(2Vp-p模式时),可以获得最大的RSN(信噪比)性能,当工作在1Vp-p模式时,RSN会下降3 dB。

如前所述,AD9238可以采用单端或者差分模拟输入。当工作在差分输入模式时,会有比较好的性能。这时建议采用AD公司的差分运放AD8138作为ADC的驱动芯片。当AD9238工作在单端输入模式时,ADC的性能会有所下降(如SFDR和SNR指标),但是比较适合低成本的应用,这时还是可以保证比较好的性能。

3.2时钟信号

高速的ADC对时钟的占空比很敏感,一般来说需要有50%(±5%)的占空比。AD9238给每个通道单独提供时钟(管脚CLK_A和CLK_B),当2个通道的采样时钟同频同相时会有比较好的性能,当2个通道不同步时性能会有所下降。

AD9238-65内部有2个时钟占空比调节器,可以将占空比调整到50%(当使能DCS管脚时)。另外两种型号没有这种功能。

时钟信号的电源驱动应该和输出数字信号驱动分开,以避免混入数字噪声。时钟信号的孔径抖动对ADC的性能影响较大,所以最好采用抖动比较小的晶振作为时钟源。

AD9238三种信号的最高时钟频率分别为20 MS/s,40 MS/s和65 MS/s,最低的时钟频率都为1 MS/s,当时钟频率低于1 MS/s时动态性能会下降。

3.3电源与接地

AD9238供电电压范围为2.7~3.6 V,分为模拟电源(AVDD,共4个管脚)和数字电源(DRVDD,共3个管脚)。每个通道可以独立地工作在休眠模式(通过使能PWDN_A或者PWDN_B)。在这种模式下器件功耗很低。

AD9238的数字输出驱动可以根据DRVDD的值设置成2.5 V或者3.3 V输出。这样可以适应不同系列的器件。

AD9238具有2种接地管脚:AGND(第1,4,13,16管脚)和DRGND(第28,40,53管脚)。模拟地(AGND)用作模拟信号的参考地,整个系统的模拟地应该尽量靠近这些管脚。数字地(DRGND)用做芯片数字部分对地电流的回路。在模拟电源和模拟地之间应该用4组旁路电路隔离开(每组有2个0.001μF和0.1μF的电容),在数字电源和数字地之间用3组旁路电路隔离开(每组有22个0.001μF和0.1μF的电容)。

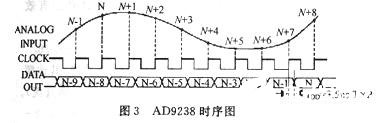

3.4工作时序

AD9238的数据输出会有7个时钟周期的流水线延迟,如图3所示。开始采样后前7个数据是无用的,应该在后端数字信号处理时舍弃掉。

AD9238两个通道的12 b数字信号输出(D0_A-D11_A和D0_B-D11_B)是独立的。一般情况下,他们各自独立的输出转换结果。当把AD9238两个通道的时钟输入CLK_A,CLK_B和管脚MUX_SELECT连接在一起时,系统处于单通道输出工作状态。此时当时钟上升沿到来时,转换数据分别送给各自对应的通道;当时钟下降沿到来时,转换数据分别送给相反的通道。这样在一个时钟周期内,数据结果可以从一个通道输出,另外一个不用的输出通道可以通过管脚OEB_A(或OEB_B)关闭掉。可以看到,这时数据率是采样率的2倍。

3.5 数字输出数据格式

AD8138输出数据为TTL/CMOS兼容电平(可以设置成2.5V或者3.3V),通过设置DFS可以使AD8138输出数据格式为偏移二进制码(DFS接AGND)或者是二进制补码(DFS接AVDD)。

另外,管脚OTR_A和OTR_B为溢出标志位,当某个通道的输入模拟信号幅度超出范围,对应通道的溢出标志位会输出高电平。

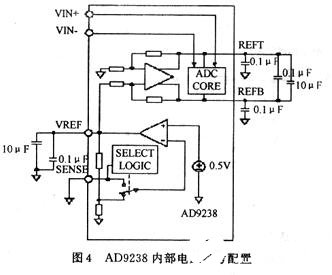

3.6 电压参考

AD8238内部有一个稳定精确的0.5 V电压参考。调整AD9238的参考电压可以改变输入信号范围,调整的方法有2种:内部参考和外部参考。输入范围根据参考电压的改变做线性变化。当把SENSE(第9脚)接地时,VREF 被设置成1 V,此时器件采用内部参考,输入信号范围为2Vp-p。有关管脚的接法如图4所示。

当把SENSE(第9脚)直接与VREF管脚连接时,输入信号范围为1Vp-p当在SENSE管脚、VREF管脚和模拟地三者之间串接2个电阻R1和R2时,输入信号范围为可改变的,即VREF=0.5×(1+R2/R1)。上述两种情况都属于内部电压参考。

当把SENSE管脚接到AVDD时,内部参考无效,采用外部电压参考。这种情况使用不多,不再做详细介绍。

在设置电压参考时,主要是改变SENSE管脚的接法,REFT和REFB管脚的接法如图4所示。值得注意的是,AD8238对每个通道都提供了电压参考,如果采用共享电压参考模式可以取得较好的性能。此时需要把SHARED_REF管脚(第62脚)接高电平,2个通道的REFT和REFB管脚互相连接(即REFT_A接REFT_B,REFB_A接REFB_B),他们各自的去耦和隔离电容接法仍同图4所示。

4、AD9238设计实例

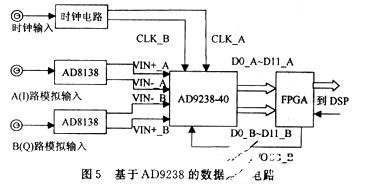

AD9238在通信接收机的射频采样中有很好的应用,现介绍一个在通信I/Q两路数据采集中的具体设计实例。

如图5所示,该数据采集电路由时钟电路、运放驱动电路、A/D转换电路、FPGA电路组成。FPGA主要完成和DSP芯片之间数据的缓冲、转换及传递,利用握手信号实现异步通信。该电路工作在2Vp-p差分工作模式,采用内部电压参考,最高采样频率可达40 MS/s。下面主要对运放驱动电路和A/D转换电路做详细的介绍。

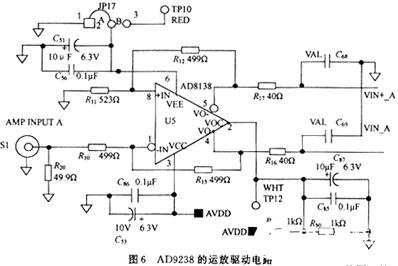

4.1 运放驱动电路

AD9238两个通道分别采用一个AD8138做为运放驱动芯片。I/Q两路中频模拟信号分别经过2个AD8138变为差分信号送给A/D转换器(第2,3,14,15管脚)。图6给出了其中一路的具体电路图,另一路与此基本相同。

4.2 A/D转换电路

该部分电路是整个数据采集电路的核心,下面仅就原理图设计的有关重要管脚进行说明,PCB设计不做详细讨论。

4.2.1 输入信号

包括模拟输入(管脚2,3,14,15)和时钟输入(管脚18,63),其中时钟输入由外部供给可调的时钟,经过反 相器后送给A/D转换器。

另外还有2个通道的输出使能(管脚22,59),由FPGA提供,低电平有效,可以根据通信系统需要控制A/D转换器实时的开始或者停止采样。

4.2.2 电压参考

包括的主要管脚是第6,7,8,9,10,11,62个管脚,在3.6中已经对这些管脚的接法做了详细的讨论。该数据采集电路板采用2 VP-P差分工作模式,使用内部电压参考,两通道工作在共享电压参考模式。

4.2.3 电源和地

AD9238有4组模拟电源和模拟地管脚(第5,12,17,64为AVDD,第1,4,13,16为AGND)、3组数字电源和数字地管脚(第29,49,52为DRVDD,第28,40,53为DRGND),他们的具体接法见3.3说明。值得注意的是,在进行PCB设计时,电路的模拟部分(模拟电源、模拟地等)和数字部分(数字电源、数字地等)应该分开布局,然后把模拟地和数字地单点连接。

4.2.4 输出信号

转换后得到12位I/Q两路的数字信号(D0_A-D11_A和D0_B-D11_B)分为2个通道输出给FPGA。溢出标志(OTR_A和OTR_B)为高电平有效,可外接一发光二级管做为电路溢出指示灯。

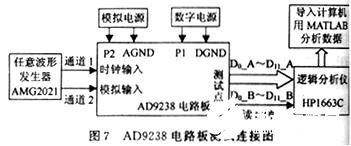

4.3 电路测试方法

在电路板设计制作完成后要对其进行测试,图7为该数据采集板的测试连接图。

采用任意波形发生器产生时钟信号和模拟信号(2个通道共用)提供给试验板,这样可以方便地对不同频率和幅度的信号进行调试;稳压电源分别给电路板提供模拟电源和数字电源;逻辑分析仪在读时钟驱动下读取采集到的两路12 b数字信号,导出后可在电脑上进行分析计算。

4.4 测试结果

衡量A/D转换器最重要的指标是有效位数和采样频率。

测试有效位数的方法是:由逻辑分析仪采集到每个通道的8192点12 b二进制补码数据,导入计算机中;运用Matlab软件分析其频谱,计算出信噪比和信纳比。然后根据信纳比(SINAD)计算出有效位数,有效位数:

SNOB=(SINAD-1.74)dB/6.02。

其中:SINAD=信号功率/其他频谱成分功率和(包括谐波,不包括直流)。

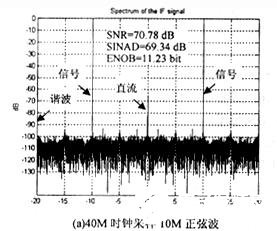

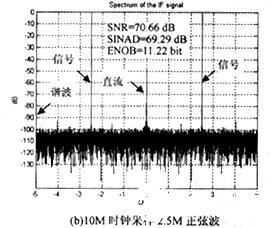

根据上述方法,对基于AD9238-40 的数据采集电路板进行了测试,在采样频率为40 MS/s和10 MS/s时仅就单个通道进行了测试,得出的结果如图8所示。

从图8的2个频谱图可以看到,在上述两种采样频率下,AD9238-40的信噪比可以达到70 dB以上,有效位数可以达到11 b以上,达到了设计要求。

图8 两种采样频率下的2个频谱图

限于篇幅,仅给出了单个通道的测试结果,有关双通道之间幅相一致性测试、串扰测试等对系统整体影响不大,所以不做详细讨论。

5、结语

本文对双通道高速A/D转换器AD9238的原理和应用做了介绍。可以看到,在双通道或多通道数据采集电路应用中,AD9238是非常有用的。相对于采用单通道A/D转换器的电路来说,AD9238具有功耗低、尺寸小、双通道幅相一致性好等独特的优点,而且AD9238还具有同样优异的SNR和SFDR性能。

责任编辑:gt

-

AD9238:高性能12位ADC的深度解析与应用指南2026-04-02 295

-

模数转换器AD9238采样失效,输出延时超过7个时钟周期怎么处理?2023-12-11 534

-

IP_数据表(A-10):单/双通道 12b D/A 转换器2023-03-16 523

-

12b双通道高速A/D转换器AD9238的知识点,总结的太棒了2021-04-22 3761

-

双通道模数转换器LTC2181相关资料下载2021-03-30 1146

-

低功率双通道模数转换器LTC2185相关资料分享2021-03-25 1232

-

双通道12位模数转换器LTC2305相关资料分享2021-03-24 1181

-

AD9680: 14位、1000 MSPS JESD204B双通道模数转换器2021-03-22 1126

-

AD9628:12位、125/105 MSPS、1.8 V双通道模数转换器2021-03-19 1469

-

AD9238双路A D转换器的五个部分2020-03-05 3335

-

AD9238BCP-20EBZ,用于AD9238评估板,双通道,10位,20 MSPS模数转换器2019-11-11 5428

-

AD9238BCP-40EBZ,是一款双通道,3 V,12位,20 MSPS模数转换器2019-11-08 4164

-

AD9238BCPZ-65模数转换器2018-11-02 1127

全部0条评论

快来发表一下你的评论吧 !