低功耗SRAM芯片IS62WV102416DALL的特点和功能

今日头条

描述

ISSI IS62WV102416DALL,IS62WV102416DBLL是超低功耗CMOS16Mbit静态RAM,组织为1M字乘16位。它是使用ISSI的高性能CMOS技术制造的。这种高度可靠的工艺加上创新的电路设计技术,可生产出高性能和低功耗的设备。IS62WV102416DBLL和IS65WV102416DBLL封装在48引脚TSOP(I型)中。ISSI代理宇芯电子支持提供技术支持及产品解决方案。

主要特点

•高速访问时间:45ns,55ns。

•CMOS低功耗操作

–25µA(典型值)CMOS待机

•CMOS以实现最佳速度和功率以及TTL兼容接口级别

•单电源

–1.65V〜1.98VVDD

(IS62/65WV102416DALL)

–2.2V〜3.6VVDD

(IS62/65WV102416DBLL)

•完全静态操作:无需时钟或刷新

•工业和汽车温度支持

功能说明

sram是随机存取存储器之一。每个字节或字都有一个地址,可以随机访问。SRAM支持三种不同的模式。每个功能在下面的“真值表”中进行了描述。

待机模式

取消选择时,设备进入待机模式。输入和输出引脚(I/O0-15)处于高阻抗状态。根据输入电平,此模式下的电流消耗为ISB1或ISB2。此模式下的CMOS输入将最大程度地节省功率。

写模式

选择芯片时且写使能输入LOW时的写操作问题。输入和输出引脚(I/O0-15)处于数据输入模式。即使为LOW,在此期间输出缓冲区也会关闭。并启用字节写入功能。通过启用LOW,来自I/O引脚(I/O0至I/O7)的数据被写入该位置。在地址引脚上指定。处于低电平时,来自I/O引脚(I/O8至I/O15)的数据被写入该位置。

读取模式

选择芯片时,写使能(WE)输入为高,则发生读操作问题。为低时,输出缓冲器打开以进行数据输出。不允许在读取模式下对I/O引脚进行任何输入。并启用字节读取功能。通过启用LOW,来自存储器的数据出现在I/O0-7上。处于低电平时,来自内存的数据将出现在I/O8-15上。

在读取模式下,可以通过拉高来关闭输出缓冲器。在此模式下,内部设备作为READ操作,但I/O处于高阻抗状态。由于设备处于读取模式,因此使用有功电流。

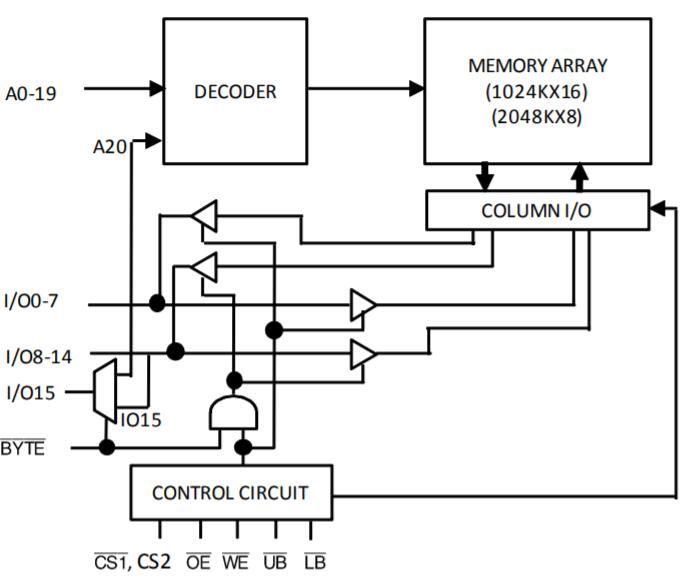

框图

fqj

-

超低功耗CMOS静态RAM IS62WV51216ALL/BLL数据手册2022-09-29 771

-

STM32外扩SRAM芯片IS62wv51216兼容替换相关资料推荐2022-02-11 2002

-

用于替换IS62WV51216EBLL-45TLI的国产SRAM芯片2022-01-26 2851

-

ISSI低功耗SRAM芯片IS62WV12816DBLL2021-12-21 1962

-

STM32外扩SRAM芯片IS62wv51216兼容替换2021-12-08 1106

-

低功耗SRAM存储器IS62WV1288DALL的特征2021-08-24 1194

-

STM32外扩的SRAM芯片IS62wv51216兼容替换2021-01-04 2646

-

ISSI IS62WV20488EALL低电压2Mx8并口SRAM2020-06-01 1441

-

ISSI代理超低功耗SRAM IS62WV102416DBLL2020-05-28 1646

-

SRAM芯片is62wv51216简介2020-03-25 17575

-

浅谈SRAM芯片is62wv512162020-03-18 4440

-

微雪电子IS62WV51216BLL SRAM存储模块简介2019-12-30 5893

-

IS62WV51216ALL和IS62WV51216BLL超低功耗CMOS静态RAM详细资料概述2018-07-24 3406

-

128K×8低电压超低功耗CMOS静态存储器IS62WV1288DALL/DBLL2017-09-20 1134

全部0条评论

快来发表一下你的评论吧 !