Altera ACEX 1K系列CPLD器件的三种配置方法的比较

可编程逻辑

描述

1、 引言

ACEX 1K系列器件是Altera公司推出的新型CPLD产品。该器件基于SRAM,结合查找表(LUT)和嵌入式阵列块(EAB)提供了高密度结构,可提供10 000到100 000可用门,每个嵌入式阵列块增加到16位宽可实现双端口,RAM位增加到49125个。其多电压引脚可以驱动2.5V、3.3V、5.0V器件,也可以被这些电压所驱动;双向I/O引脚执行速度可达250MHz。该器件还应用Altera专利技术进行了重要的生产改进,进一步降低了器件的成本,提高了产品的性能价格比。因此,ACEX 1K器件可用来实现许多逻辑复杂、信息量大的系统。但是在器件操作过程中,ACEX 1K系列器件的配置数据存储在SRAM单元中,由于SRAM的易失性,配置数据在每次上电时必须被重新载入SRAM。

2 、配置ACEX 1K系列器件三种方法的比较

对于ACEX 1K系列器件,目前实现加载的方法有以下3种:①采用PROM并行加载;②采用单片机控制实现加载;③通过JTAG口直接一次性实现编程数据加载。第一种方式需要占用较多的CPLD管脚资源,虽然这些资源在加载完成后可用作一般的I/O口,但在加载时不允许这些管脚有其他任何外来信号源;另外数据存储在PROM与CPLD之间的大量固定连线,如8位数据线以及大量访问PROM的地址线等,使得PCB板设计不便。但是这种方式有一个好处,即PROM的容量较大、容易购置、价格低、技术支持(编程器)较好。第二种方式采用单片机控制,由PROM中读取并行数据,然后串行送出。由于涉及到单片机编程,对于开发者来说较为不便;另外,如果单片机仅用来实现该任务,较为浪费硬件资源。CPLD的一个最大优点是采用计算机专用开发工具,通过JTAG口直接一次性实现编程数据加载,但是由于ACEX 1K器件SRAM的易失性使数据无法永久保存,为调试带来很大的不便,特别是从事野外作业者。

目前,Altera公司推出了相应的配置器件。在CPLD器件配置过程中,配置数据存储在配置器件的EPROM中,通过配置器件内部振荡器产生的时钟控制数据输出。本文以20脚EPC2器件(以下简称EPC2)为例阐述配置器件与ACEX 1K系列器件的连接。

3、 EPC2器件简介

EPC2具有Flash配置存储器,可用来配置5.0V、3.3V、2.5V器件。通过内置的IEEE Std. 1149. 1 JTAG接口EPC2可以在5.0V和3.3V电压下进行在系统编程(ISP)。 系统编程后,调入JTAG配置指令初始化ACEX 1K器件。EPC2的ISP能力使ACEX 1K器件的初始和更新更容易。当用EPC2配置ACEX 1K器件时,在配置器件的内部发生带电复位延迟,最大值为200ms。Alterat公司的QuartusⅡ和MAX+PLUSⅡ软件均支持配置器件的编程,设计中软件自动为每一个配置器件产生POF。多器件设计中,对于多个ACEX 1K器件,软件可以将编程文件与一个或多个配置器件联合。软件允许用户选择适当的配置器件更充分地储存每一个ACEX 1K器件的配置数据。EPC2器件用于与ACEX 1K器件连接的引脚功能见表1。

4、 器件连接及工作原理

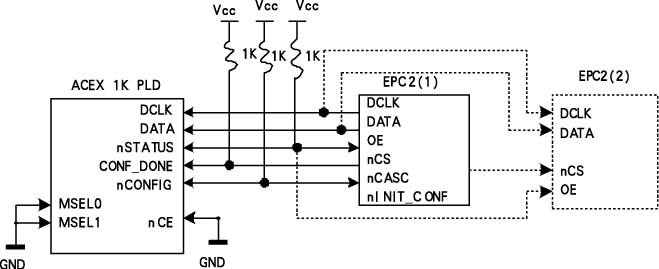

当用一片EPC2配置ACEX 1K器件时,EPC2的控制信号nCS、OE、DCLK直接和ACEX 1K系列器件的控制信号连接。图1给出了ACEX 1K器件和一片EPC2的连接关系。

EPC2的nCS和OE引脚控制DATA输出引脚的三态缓冲器,使能地址计数器和EPC2的振荡器。nCS引脚控制配置器件的输出。当OE引脚接低电平时,不论nCS为何状态,地址计数器复位,DATA引脚输出为高阻状态。当OE引脚接高电平时,如果nCS保持高电平,则计数器停止计数,DATA引脚保持高阻状态;如果nCS接低电平,则计数器和DATA引脚正常工作。EPC2允许用户将nINIT_CONF引脚与PLD器件的nCONFIG引脚相连来初始化PLD器件的配置。EPC2的DATA引脚与ACEX 1K系列器件的DATA0或DATA引脚相连。存储在EPC2器件中的数据在其内部时钟的控制下顺序输出到DATA脚,然后在控制信号的控制下输出到CPLD器件的DATA0或DATA引脚。当配置数据的大小超过一片EPC2的容量时,可以采用多片级联的方法。这时候器件的nCASC和nCS引脚做器件间的握手信号。器件连接如图1虚线所示。

用级联EPC2 配置ACEX 1K器件时,EPC2的操作与其在级联链中的位置有关。当级联链中的第一个即主EPC2加电或复位,且nCS脚为低电平时,主EPC2控制配置进行。配置过程中主EPC2向其后的从属EPC2和CPLD器件提供所有的时钟脉冲,并向PLD器件提供第一个数据流。当主EPC2中配置数据发送完毕,器件的nCASC脚变为低电平,使第一个从属EPC2的nCS脚变为低电平,从而使从属EPC2向外发送配置数据。每一片EPC2中数据全部输出且nCASC引脚为低电平时,器件的DATA引脚置为高阻状态以避免和其他配置器件发生竞争。一旦所有的配置数据传送完毕,且基于查找表的CPLD器件的CONF_DONE脚驱动主EPC2的nCS脚为高电平,主EPC2器件将额外增加16个时钟周期来初始化CPLD器件。随后主EPC2器件进入空闲状态。当需要另外加入EPC2器件时,可以将欲加入的EPC2的nCASC引脚和级联链中的从属EPC2的nCS相连,DCLK、DATA和OE引脚并联。

5、 结论

从上述的阐述中,我们可以看到:采用Altera公司的专用配置器件加载数据时,配置器件与CPLD之间的接口线非常少,且直接连接不需要外加智能控制器;通过器件内置JTAG口能够将数据一次性写入EPROM中加以保存,而且当CONFIG数据量较大时,可以采用多片级联;器件可多次写入,当需要下载新数据时不需事先擦除器件中原有数据,只需将新数据直接写入即可。由此可见采用配置器件加载数据方便、可靠、易学易用。

责任编辑:gt

-

今日说“法”:FPGA的三种配置方式2023-04-24 845

-

ACEX 1K系列器件实现加载的方法有哪几种?2021-04-15 1035

-

FPGA的三种配置方式详解2020-07-09 9066

-

请问ACEX1K芯片的IOH, IOL分别是多少?2019-08-07 4625

-

FPGA与CPLD怎么区分2019-07-01 2602

-

CPLD/FPGA有哪些设计工具?2019-03-04 3375

-

FPGA教程之CPLD和FPGA的配置与下载的详细资料说明2019-02-28 1819

-

FPGA教程之ALTERA的CPLD与FPGA器件的详细资料说明2019-02-27 1639

-

铁损耗曲线的三种拟合方法比较2017-01-02 706

-

三种电路仿真软件比较及器件模型加入方法2010-05-10 1519

-

altera fpga/cpld设计2009-07-10 871

-

ACEX 1K系列CPLD配置方法探讨2009-06-20 824

-

用单片机配置CPLD器件2009-03-28 1483

全部0条评论

快来发表一下你的评论吧 !