资料下载

×

J750 512针测试系统维修参考手册

消耗积分:2 |

格式:pdf |

大小:4.13 MB |

2020-07-23

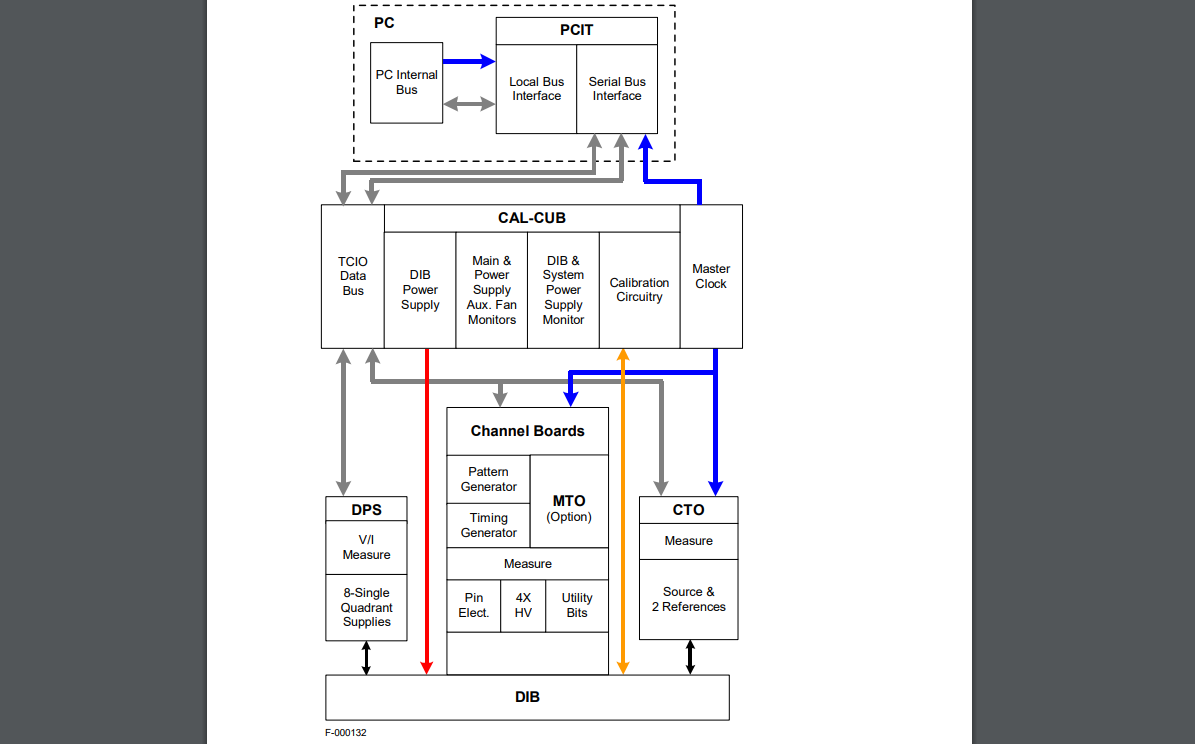

本手册的系统概述章节提供了J750512引脚测试系统的一般说明。本章包括系统功能列表、系统主要组件的说明、J750组件的位置和基本说明,J750组件是J750的一部分。有关电路板和组件的详细信息,请参阅本章其他章节手册。那个以下信息包含在本章移动系统框图中

J750-512引脚测试系统提供测试各种复杂的超大规模集成(VLSN)设备所需的功能和灵活性,从测试仪产生一个测试头系统,可以坐在prbr:y awx 3 7.微控制器到ASIC之上,并建立在一个平台上,将随着客户的增长而增长测试仪将整个数字子系统集成到一个64针通道板上,这意味着一个完整的5 12针测试仪可以由8个通道板和多个支撑板组成。这种集成化设计大大降低了复杂度J750-512引脚测试系统是一个功能齐全的100MHZ超大规模集成电路测试仪。集成数字通道架构提供了完整的每引脚100MHZ测试,具有革命性的经济性和占地面积。该测试仪的数字特性包括100MHz全格式化(非多路复用)驱动和接收MEG图案深度每引脚高电压/高电流(±24v,±200ma)PMU6每引脚边缘高达50MHZ,每个引脚4个边缘高达100MHz Z256全局时间集,32个每引脚边缘设置周期,基于飞行时间,周期和格式变换器每针参数测量单元(PPMU)仪器配置,以进行真正的并行测试硬件站点启用每通道异步模式发生器

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章