使用XC9500 CPLD实现FPGA电路接口的方案设计

可编程逻辑

描述

概述

随着FPGA芯片密度的增加,串行PROM已不能适应高密度的FPGA的配置。大容量的并行PROM所要求的寻址方式又不能直接与FPGA接口,这时可以采用XC9500 CPLD和PROM对高密度FPGA进行配置。FPGA设备在线配置或电源上电时,配置逻辑会被自动清除。FPGA的PROGRAM信号必须在300ns内置低,使配置逻辑复位。INIT输出在内部配置存储器清零期间保持低电平。一旦INIT管脚变高,就表明设备已准备接受配置。

FPGA的配置有主设备串行配置和从设备串行配置两种方式。XC4000和Spartan系列设备在INIT变高后要求在设备准备接收配置数据之前有一个超时期,但Spartan-Ⅱ不在此列。在主设备串行模式下,FPGA在超时达到要求之前关闭配置时钟(CCLK)。在从设备串行模式下,必须在超时期完成后才能开启CCLK。而Spartan-Ⅱ和Virtex系列在INIT信号变高之后不要求超时期,一旦INIT信号变高,设备立即准备接收配置数据。

接口设计

在串行配置模式下用并行PROM对FPGA进行配置时,需要专门的接口进行并行数据到串行数据的转换,并管理FPGA的配置信号。接口的设计方法很多,图1是使用XC9500 CPLD配置FPGA的电路结构。

VSPROM的设计

设计虚拟串行PROM(VSPROM)的目的是为并行PROM和FPGA之间的连接提供接口,接口的任务是将从PROM中读来的数据转换成串行输出,然后再将地址递增。VSPROM的结构如图2所示。在处理数据的同时,VSPROM还管理INIT和DONE信号。在配置期间,如果INIT被FPGA拉低,表明出现配置错误,VSPROM必须复位并等待用户将FPGA复位,然后重新配置。一旦FPGA的DONE变高,表明配置成功,VSPROM就撤消ROM_CS来取消PROM的使能,将自己和PROM与FPGA隔离,并将DOUT设为高阻态。

在VSPROM的设计中,使用XC9536PC44-10、XCV600BG432-6和一个8位的PROM(AT27C080)验证。

主设备串行配置时,Xilinx FPGA提供配置时钟(CCLK)。CCLK与VSPROM的时钟CLK_IN直接相连。Virtex和Spartan-Ⅱ支持的最大配置速率是60MHz,XC4000/Spartan系列支持的最大配置速率是8MHz。然而,实际的最大配置速率还应该考虑PROM的存取时间(TACC)和主设备串行输入的时间(TDSCK)。

主设备串行模式下PROM的频率=1/(TACC+TDSCK)。

TACC对于Virtex为5.0ns,对于XC4000/Spartan系列是20.0ns,PROM的TACC对于AT27C080是100ns。因此,对于Virtex设备最大频率为9.5MHz,对于XC4000/Spartan设备最大频率为8.3MHz。这就是说,Virtex设备的配置频率受PROM的限制,而XC4000/Spartan设备的配置频率受自己内部CCLK的限制。为了加快Virtex设备的配置速度,可以选择更快的PROM。在主设备串行模式下,FPGA在准备好接收配置数据之前会关闭CCLK,因此VSPROM的设计不用考虑其他问题。

从设备串行配置有专门的振荡电路提供配置时钟,速度比较快。振荡电路的时钟输出必须接FPGA的配置时钟(CCLK)和VSPROM的时钟(CLK_IN)。最大配置频率对于Virtex是66MHz,对于XC4000/Spartan系列是10MHz。同样,配置频率受到PROM的存取时间(TACC)和从设备串行输入时间(TDCC)的限制,计算方法同上。

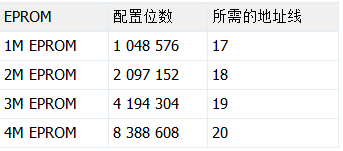

表1 不同的EPROM所需的地址线

从设备串行模式下对XC4000或者Spartan系列FPGA进行配置时,必须考虑设备开始的顺序(这里讨论的顺序不适合Spartan-Ⅱ系列)。正如前面提及的,一旦INIT置高,设备能够接收配置数据之前需要有一个超时期,VSPROM接口必须能够在超时期达到之前封锁振荡电路的时钟输出。如果是Virtex或者Spartan-Ⅱ设备作为从设备,INIT置高后FPGA可以立即准备好接收配置数据,就不用考虑超时的问题。

在以上两种配置方式下,并行PROM的大小和数目由配置FPGA所要求的配置位的数目决定。PROM的大小由所需要的地址线数目决定。缺省情况下,VSPROM设计使用19根地址线,对应4MB的PROM。当需要更多的容量存储配置数据时,可以修改VSPROM源程序(VHDL或GENERIC)使其适应新的需求,详细情况参见表1。如果配置要求多于19根地址线,可以使用XC9572设计VSPROM。

FPGA配置期间发生错误时,INIT信号变成低电平,配置程序中止。所以VSPROM需要管理INIT,当INIT变低时,VSPROM需要复位并等待FPGA的复位后才能进行重新配置。简单的方法是可以在INIT变低时用VSPROM控制FPGA的PROGRAM变低,迫使FPGA清除自己的配置存储器,然后重试。或者可以将INIT接微控制器,在配置期间INIT变低时控制整个系统复位。

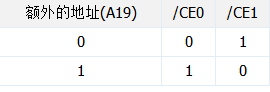

表2 两个PROM的地址译码

接口的扩展

FPGA要求的配置空间大于所选的PROM时,可以使用多个PROM,连接方法如图3所示。这时地址线是20位,高位地址线 ADDRESS(19)用来选择PROM,见表2。

多个FPGA可以直接级连,如图4所示。这种情况下对VSPROM没有特殊的要求。CCLK,INIT,DONE和PROG信号必须并联,前一个设备的DOUT信号连接下一个的DIN。

调试应用

为了保证FPGA的CCLK和DIN信号不受任何干扰,在设计电路板时通常在每个Vcc和GND之间加0.1μF和0.01μF的电容。同时,要保证Vcc的响应速度足够快。如果电源响应速度不够快、响应单调性不好,会影响系统的上电过程从而影响正确的配置。

所有的XC4000和Spartan设备都对5V和3.3V环境兼容。Virtex和Spartan-Ⅱ设备也可以直接应用于5V和3.3V的环境,在LVTTL与3.3V的Vcco相连时必须使用缺省的I/O标准。详细情况参见Xilinx设备的电压兼容性数据资料。Virtex-E设备不能直接应用在5V环境,因此在配置时必须加以考虑。

责任编辑:gt

-

请问如何实现CPLD遥控编程?2021-04-27 1610

-

XC9500系列CPLD遥控编程该怎么设计?2019-09-30 1510

-

FPGA与CPLD怎么区分2019-07-01 2600

-

适用于XC9500的工具2019-04-11 1618

-

CPLD XC9500是否有任何序列?2019-01-15 1618

-

Digilent_XC9500_DigiLab_XC952016-02-22 1034

-

xapp069 - 使用XC9500 JTAG边界扫描接口2012-02-17 1258

-

XC95002009-05-15 1149

-

介绍如何使用XC9500的时序模块2009-05-13 769

-

用CPLD实现单片机读写模块2009-04-16 345

全部0条评论

快来发表一下你的评论吧 !