使用FPGA设计数字电路时的综合工具介绍

可编程逻辑

描述

在使用FPGA做数字电路设计的流程中,综合是其中非常重要的一个步骤。同样的设计源代码,无论是VHDL或Verilog HDL,采用不同的综合工具综合会产生不同的结果。

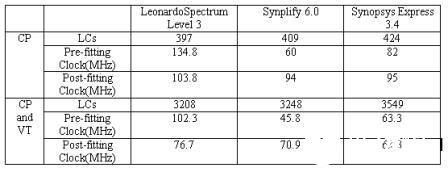

通过使用LeonardoSpectrum Level 3,Synplify 6.0 以及 Synopsys Express 3.4三种综合工具对大小两类设计进行综合,并将综合得的网表送Quartus布局布线,分析两个步骤的结果后得到如下结论:

1.针对较小的设计(1000 LCs以下),三者综合后的结果是最高频率差别较大,但经过Quartus布局布线后的结果差别并不太大;

2.针对较大的设计(1000 LCs 以上),三者综合后的结果是最高频率差别较大,经过Quartus布局布线后的结果差别较大。

下表为结果数据:

根据上述的分析,无论对较大的或是较小的设计,采用LeonardoSpectrum Level 3综合的结果最好,相应进行布局布线的结果也最好。

另,使用LeonardoSpectrum Level 3时,某些选项的设置需要注意:

1.在选择综合策略时,选择Hierachy会提高综合后的速度;

2.在指定好器件后,在窗口Technology?Technology Setting?Wire中选择apex20e_lab_default会得到最好的综合结果;

3.在窗口Optimize?Advanced Settings中,不可选择 “Do not use wire delay during delay calculations”和 “Break combinational loops statically during timing analysis”两项。

责任编辑:gt

-

高速数字电路的仿真2009-03-20 1706

-

数字电路—24、计数器2025-03-26 612

-

什么是数字电路2009-04-06 11849

-

FPGACPLD数字电路设计经验分享2012-08-07 2239

-

FPGA CPLFPGA CPLD 数字电路设计经验分享2012-08-11 3906

-

数字电路的应用介绍2018-08-28 3871

-

《数字电路》课程口袋型FPGA实验板介绍2021-01-28 3191

-

PSpice软件在数字电路分析中的应用2011-08-23 1309

-

数字电路设计·仿真·测试2011-09-07 3003

-

数字电路中的FPGA和verilog教程2016-01-18 727

-

在没有综合工具情况下,如何设计数字电路?2020-06-17 3960

-

基于FPGA的数字电路设计2020-08-16 8884

-

FPGA CPLD数字电路设计经验分享.2021-09-18 1431

-

数字电路中的计数器详解2023-10-17 6785

-

FPGA/CPLD数字电路设计经验分享2023-11-21 606

全部0条评论

快来发表一下你的评论吧 !