采用FPGA和通用DSP相结合实现视频图像采集系统的设计

可编程逻辑

描述

引 言

1964年美国JPL实验室处理了太空船“徘徊者七号”发回的月球照片,标志着数字图像处理技术开始得到实际应用。随着基于实时图像处理的视觉测量理论及应用技术的迅速发展,可独立运行的视频信号数字处理平台已成为视觉测量领域的一个发展趋势。本文主要研究高速实时图像处理系统中的图像采集、处理技术,采用FPGA和通用DSP相结合的方法,充分发挥FPGA加通用DSP结构的灵活性及实时处理能力。

1、 系统设计

图1为系统硬件结构框图。

1.1 硬件设计方案

系统采用两片TI公司的TMS320C6416为核心处理器,最大峰值速率为9600MIPS, DSPA的64bit EMIFA连接FPGA与片外大容量SDRAM,并可与FIFO无缝连接;16bit的EMIFB连接片外8M FLASH存储器,用于加载DSP的启动信息与FPGA的初始化配置。增强型直接存储访问控制器(EDMA)与串行多通道缓冲串口(McBSP)可用于构成FPGA与DSP之间的控制通道以及两片DSP之间的控制信号传输通道。

FPGA连接两片C6416的64bit/133MHz的EMIFA总线,或通过McBSP口相连。在FPGA的存储扩展结构上,可连接两组片外存储器2MB的快速SBSRAM和32M的DDR SDRAM,这种双存储机制能够在增强运算的协处理能力及灵活性方面得到一定程度的优化。例如SBSRAM提供的线性存储模式,可用于在进行类似于快速FFT运算时开辟一个面向分块的信号处理模式。

由于C6416具有32bit/33MHz的PCI总线接口,支持PCI2.2规范,最大传输速率达到132MB/s,系统采用PCI桥QL5604连接主机与Local Bus,总线搭载两片C6416和FPGA,并可选择搭配全局存储器(Global SDRAM)。两片C6416的数据传输可通过双口RAM 或经EMIF与FPGA内建的FIFO进行双向传输,两片C6416在运算处理方面可以用流水线的方式并行计算,也可由基于总线的突发模式(Burst-Mode)进行数据处理。

1.2 视频图像采集

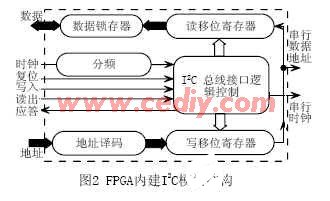

本系统采用SAA7111A作为前端视频解码器,由于采用了I2C总线接口标准,在这里我们将I2C总线的控制电路集成到FPGA内部[1],如图2。地址译码器产生相应的读/ 写操作地址,写移位寄存器将地址信息或数据信息经过并/ 串转换后发送到SDA上;读移位寄存器将SDA上接收的数据存入双向数据锁存器。

1.3 视频图像处理

SAA7111A对输入的PAL格式的模拟图像进行A/D变换,由FPGA完成在隔行采样方式下对FIFO的逻辑时序控制,包括SAA7111A输出的行、场同步控制信号。

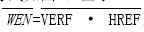

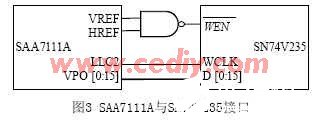

在图像的帧存储过程中,利用同步信号(RTS0、VREF、HREF)实现对采集起止点的控制,SAA7111A与SN74V235 FIFO的接口方式如图3。由于SAA7111A没有独立的写使能信号,因此,采用VERF和HREF的逻辑与非关系( )作为SN74V235的

)作为SN74V235的 。当一帧图像存入帧锁存器后,由FPGA发出控制信号,逐行写入到FIFO中,达到半满(HALF_FULL)状态后,发出READY信号,由DSPA以DMA方式通过EMIFA口读出一行数据,同时考虑到FIFO与SDRAM共用EMIFA总线,因此该步骤只需一次操作便可完成。

。当一帧图像存入帧锁存器后,由FPGA发出控制信号,逐行写入到FIFO中,达到半满(HALF_FULL)状态后,发出READY信号,由DSPA以DMA方式通过EMIFA口读出一行数据,同时考虑到FIFO与SDRAM共用EMIFA总线,因此该步骤只需一次操作便可完成。

1.4 FPGA与DSP之间的连接

DSP通过EMIF接口总线连接到FPGA,EMIFA口的数据线、地址线、片选信号等与FPGA的I/O连接,将FPGA内部存储器映射到DSP地址空间,实现高速数据交换。在FPGA内部构建基于FIFO方式的EMIF接口模式,片使能信号 和异步输出使能信号

和异步输出使能信号 用于产生FIFO的读、写使能信号。同时,Xilinx Virtex系列FPGA内部集成Block RAM,可以配置成两个端口完全独立的真正的双口RAM。双端口Block RAM的一侧被用来实现与DSP的通信,另一侧用于实现与FPGA内部逻辑电路与FPGA嵌入式处理器的通信[3]。

用于产生FIFO的读、写使能信号。同时,Xilinx Virtex系列FPGA内部集成Block RAM,可以配置成两个端口完全独立的真正的双口RAM。双端口Block RAM的一侧被用来实现与DSP的通信,另一侧用于实现与FPGA内部逻辑电路与FPGA嵌入式处理器的通信[3]。

1.5 DSP与主机、双DSP间的通信

主机可通过桥接的PCI总线直接访问DSP资源,DSP对主机的访问则采用DMA方式以主模式访问上位机。同时DSP与SDRAM之间也以DMA方式进行200MB/s的数据传输。在大数据量情况下考虑实时性因素,两片C6416之间通过全双工串行多通道缓冲串口McBSP进行控制信号的传送,通过两片C6416的EMIFA口连接至FPGA的EMIF总线接口,可达到800MB/s的数据传输速率。因此,该设计在双DSP之间以及与主机的通信方面是灵活的。DSPA的EMIF存储空间地址分配如表1。

2、 软件设计及实验测试

使用TI公司的CCS集成的C/C++开发环境,仿真测试通过后经PCI总线写入相应存储器。PCI驱动程序开发在Windows 2000视窗环境下,采用NuMega Lab公司提供的Driver Studio, TI公司提供的API函数包,实现诸如中断控制、I/O设置等功能。

2.1 FFT算法测试

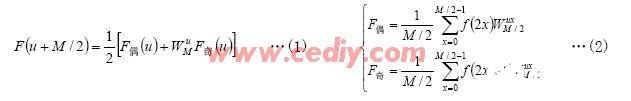

采用M为2的整数次幂FFT算法算法。依据(1)、(2)两式,一个M点的离散FFT可以只计算M/2点的离散FFT,对于M=2r个点的离散FFT运算,需要进行r轮递推排序,每轮有(M/2)•r =(M/2)lbM次乘法和M•lbM次加法,整个运算次数可减少到

基于C6416的单、双DSP在处理二维FFT和一维FFT、IFFT的运算时间比较见表2。试验结果表明,该系统完成FFT算法测试的运算速度较快,能够满足实际应用的要求。

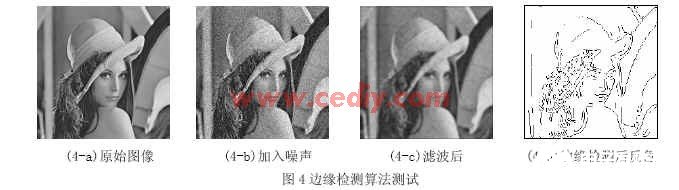

2.2 改进LOG边缘检测算法测试

以LENA图片(图4-a)加入噪声后的图像(图4-b)为测试目标,首先将图像灰度等级映射为8级,分别计算0o、45o、90o和135o时的灰度共生矩阵,并以其惯性矩阵特征值的平均值作为目标图像滤波层的惯性矩阵特征值,进行三次循环操作,即对前一次得到的高斯滤波图像进行相同的运算,从而依次得到三个惯性矩阵平均特征值:σ1、σ2、σ3,满足不等式(σ2-σ3)<(σ1-σ2),为了不产生过多的计算量,将经过滤波的图像(图4-c),以σ3=1.5337作为LOG算子的空间系数,得到反色后的边缘检测图像(图4-d)。

实验结果表明,在该系统平台上进行改进LOG算子的边缘检测方法能够取得较好的效果,基本上可无延迟的输出边缘图像,满足处理任务的实时性要求。

3 、结束语

本文作者创新点:本设计所提出的基于PCI总线的DSP×2+FPGA的实时视频图像处理平台能够满足大多数实时图像处理任务,以FPGA作为协处理器的方式一方面缓解了DSP的运算压力,同时也增加了该系统的灵活性,并通过对系统结构的优化,使得该系统能够作为一款结构紧凑,实时性强的高速图像处理平台。

责任编辑:gt

-

如何采用Spartan-3 FPGA实现通用视频采集系统的设计?2021-06-08 1915

-

使用FPGA控制实现图像系统视频图像采集的设计资料说明2021-01-26 1138

-

如何使用DSP和FPGA技术实现细胞图像采集系统的设计2021-01-25 1357

-

基于FPGA的高速数据采集系统该怎么设计?2019-09-05 2381

-

一种基于FPGA+DSP的视频处理系统设计2019-07-01 2389

-

基于FPGA+DSP架构的视频处理系统设计2019-06-28 2292

-

基于FPGA与DSP的视频处理系统设计2019-06-19 2217

-

一种基于DSP+FPGA视频图像采集处理系统的设计与实现2017-12-25 5844

-

基于DSP和FPGA技术的细胞图像采集系统设计2016-08-26 676

-

基于DSP和FPGA的CCD图像采集系统设计与实现2011-02-25 1315

-

基于DSP和FPGA的通用图像处理平台设计2010-02-01 1768

-

基于DSP+FPGA的实时视频采集系统设计2009-12-16 815

-

FPGA控制实现图像系统视频图像采集2009-07-28 998

全部0条评论

快来发表一下你的评论吧 !