基于ACEXIK系列FPGA器件EPIK10实现8路脉冲量计数系统的设计

可编程逻辑

描述

1、引言

八路脉冲量输入模板(Pl)的功能是对8路0-50kHz阀值电压在0-5V、0-12V、0-24V电平的脉冲量信号进行测量,可以进行相应的频率型和累积型信号的计算。频率型和累积型分别适用于不同的场合。当对累积精度要求较高时使用累积型组态,而当对瞬时流量精度要求较高时使用频率型组态。

2、模板的主要技术指标

1. PI模板可允许八路脉冲量信号输入,并且通道之间是点点隔离的;

2. 信号频率的输入范围:频率型信号为0-50kHz,累积型信号为0-2kHz,输入电流大于7mA;

3. 对输入的脉冲量信号采用专用设备FPGA进行计数,做批处理;

4. 通过工程师站配置所需信息:每一路可选择输入信号范围和类型及对应的工程量量程、上下限报警点等,并记忆于模板上的非易失性存储器中;

5. 根据所配置的信息,智能节点实现自动测量;

6. 最小辨识的输入脉冲信号宽度为5µs,分辨率1Hz;

7. 具有整形处理、掉电保护、通信故障自检与报警及CPU故障自检与报警功能;

8. 专用计数设备FPGA与脉冲量信号之间采用了光电隔离措施,抗干扰能力强;

9. 可安装于测量现场,通过CANBUS总线将每一路的测量信息传送到主控模板,方便地组成智能分布式控制系统。

3、模板的硬件组成及总体设计

PI模板选用MCgslZD64为微处理器,配以Altera公司生产的ACEXIK系列现场可编程门阵列即GA器件EPIK10、AGILENT公司的高速光耦合器6N136、施密特触发器74HC14、总线驱动器PCA82C250等组成。PI模板设置了8路输入通道,用来采集0-50kHz阀值电压在0-5V、0-12V、0-24V电平的脉冲量信号,信号通过高速光耦合器6N136,再经施密特触发器74HC14对信号整形,整形后的信号进入FPGA器件EPIK10,在该器件内部完成对8路脉冲量信号的计数,同时微处理器MC9512D64实现对FPGA器件的控制,从而完成对8路脉冲量的计数及结果的存取,并通过CAN总线通信将结果传送到主控模板。

该设计选用了Altera公司生产的ACEXIK系列FPGA器件EPIK10实现对8路脉冲量的计数,对于该器件的设计及功能的实现是PI模板设计的重点和难点,下面就从可编程逻辑器件开始做详细的介绍。Pl模板总体设计如图1所示。

图1 PI模板总体设计图

4、FPGA实现8路脉冲量计数的设计

4.1 CPLD与FPGA的区别

在主控模板的设计中,采用了CPLD实现了总线的转换,在脉冲量模板中又使用了FPGA来实现对脉冲量的计数。概括起来FPGA和CPLD都是由逻辑单元、I/O单元和互连三部分组成的,I/O单元的功能基本一致,单元、互连以及编程工艺则各不相同,而它们的区别又决定了它们应用范围的差别。

在选择可编程逻辑器件时,所选器件的逻辑资源量能否满足系统的要求是首要考虑的因素,但在实现调试前很难准确确定芯片耗费的资源。PLD器件的应用大都是在使用开发软件前大概估算一下所需资源量,选择有一定冗余的器件以便充分满足系统的设计要求,同时也要考虑系统设计完成后,有可能增加新的功能,以及后期硬件升级的可能性。本系统设计时选用的是可编程逻辑器件的主流厂家Altera公司新近提供的一款中等密度器件ACEXIK系列的FPGA器件EPIK10。

ACEXIK系列采用SOPC设计,是基于Altera公司的查找表结构的一种现场可编程门阵列(FPGA),性能高,功率低。ACEXIK系列基于静态存储器SRAM结构,管脚之间的延迟低于3.5ns,集成了10000-100000个可用门。

4.2 配置器件

基于静态存储器SRAM结构的可编程器件在芯片掉电时其存储的数据将丢失,所以这类FPGA必须与一块EPROM或EZPROM连用—将各点的编程数据存储在E2PROM(或EPROM中)。芯片每次上电工作时,首先将各编程点的触发器按E2PROM中存储的数据置位,则FPGA芯片就能执行所设计的功能。因为在这种方式中,各实际的连接器件并未像CPLD那样被烧死,换用其他编程数据即可按其他的设计结果工作,所以常将这种方式称为配置(Configure)。

Altera的配置器件可以存储基于SRAM工艺的ACEX、FLEX、APEX系列器件的配置数据,提供的配置器件支持ISP,简化了设计流程,并且可以现场升级;支持多重端口电压标准,支持3.3V和5V电压,适合于混合电压设计使用,并且密度范围宽。该设计中选用的EP1K10器件的配置器件可以是EPC1、EPC2和EPC1441,它们都支持3.3V和5V电压,不同的是存储空间大小不同,设计中选用了EPC1441,它可存储440800个字节。

所有的APEX、FLEX和ACEX系列器件可以控制整个配置过程,在不需要控制器的条件下可以自动的从配置器件当中读取数据,完成配置过程。如图2所示,是用EPC1441配置EP1K10器件的电路图。

EPC1441将配置数据存储在EPROM中,用内部振荡器存储串行时钟数据的输出。OE、nCS和DCLK引脚为地址计数器和输出三态缓冲器提供控制信号。配置器件发送一串连续的配置数据到它的DAIA引脚,这样数据就被发送到EP1K10的DATA0或DATA输入引脚上,完成了配置过程。

4.3 开发软件Max+PlusII的功能及使用

对于CPLD/FPGA的设计来说,成功与否在很大程度上取决于EDA开发软件。在提供高性能芯片的同时,Altera公司也提供了强大且易于使用的软件开发工具Max+PlusII。设计者不需精通器件内部的复杂结构,可以用自己熟悉的设计工具,如原理图输入或硬件描述语言建立设计,Max+PlusII把这些设计自动转换成最终所需的格式,设计速度非常快。Max+PlusII的设计流程包括几个部分,如图3:

图2 EPC1441配置EP1K10器件电路图 图3 软件开发流程

Max+PlusII为实现不同的逻辑功能提供了大量的图形元件和宏功能符号供设计人员在图表编译器文件中直接使用。这些功能为FPGA的设计提供了高度的灵活性,缩短了开发周期,在该设计中使用了大量的74系列逻辑实现锁存、计数、译码等功能。

5、具体设计方案及实现

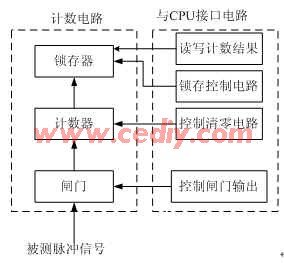

模板选用Altera的FPGA器件EP1K10实现8路脉冲量计数的功能,如图4所示。

图4 FPGA内部设计框图

对该器件的设计包括接口电路设计和计数电路设计两个部分,其中计数电路部分又包括闸门、计数器和锁存器三个部分的设计。

图5是对计数电路部分的具体设计原理图,图中只画出了对第一路脉冲量信号计数的电路,对其他七路信号的计数与此相同。如图所示,选用74HC125相当于一闸门,脉冲信号接到输入引脚,输出控制引脚接至CPU来控制何时将脉冲信号输出至计数器开始计数。一个74HC125可控制四路脉冲信号,那么只需两个74HC125即可完成对八路脉冲信号的计数使能。

图5 EP1K10实现脉冲计数的内部原理图

对计数器的设计是用4片4位二进制加法计数器74161采用同步级联方式构成的16位二进制同步加法计数器。四个芯片公用外部时钟和清零信号。由于低位片的ENT=ENP=1,所以总是工作在计数状态。而高位片的ENT、ENP接低位片的进位输出端RCO,所以只有当低位片计数到最大值1111时,RCO=1使高位片的ENT=ENP=1,满足计数条件,在下一个时钟脉冲到来时,低位片回零,高位片加1,实现了进位。由于四个芯片共用外部时钟,在需要翻转时,四片同时翻转,所以称为同步级联。

Max-PlusII中提供了大量的库文件,其中包括了上面设计图中的74系列逻辑元件及各种门,只需调用即可。在新建的项目下输入设计好的图形后,下一步是对其进行编译。打开“ComPiler”,选择“start”开始编译。编译成功后生成时序模拟文件和器件编程文件。若有错误,编译器停止编译,并在下面信息框中给出错误信息。编译器通过“TimingSNFExtractor”后就可以进行时序模拟,判断输入输出间的延迟。

为使设计符合用户的要求,由编译器自动选择的目标器件和管脚锁定将由用户重新选择。此时需要对项目进行重新编译。最后将设计的项目配置到所选择的器件中。

本文作者创新点:

可编程逻辑器件的应用成为现代电子电路设计中的高效方式。本文基于FPGA实现了对8路脉冲量信号的计数功能,满足了模板的性能要求,同时,具有较强的实时性,可以满足工业现场高速通信的需要,也可为复杂控制系统实现实时控制提供强有力的工具。

责任编辑:gt

-

基于FPGA cylone II芯片实现智能脉冲电源的设计2021-02-23 3935

-

FPGA系列器件汇总2012-08-12 2377

-

新型TurboDisc EPIK700 GaN MOCVD系统2021-02-07 4547

-

脉冲量输入信号调理电路2009-02-09 2182

-

FPGA的多路可控脉冲延迟系统设计2009-03-29 3065

-

单片机脉冲计数器程序详解2017-11-23 12809

-

以FPGA为基础的脉冲量采集模块设计详解2018-07-18 8373

-

如何使用FPGA和DSP进行高速数据采集系统设计2018-11-07 1404

-

基于Flash FPGA器件实现脉冲延迟控制系统的设计2020-08-11 1896

-

编码器脉冲计数/4倍频计数/生产线/物流包裹数量计数Modbus和MQTT,WiFi模块2022-11-23 2022

-

球栅尺脉冲信号计数采集模块磁栅尺频率测量2022-11-28 1115

-

2路DI脉冲计数扩展模块2022-12-12 1697

-

1路编码器脉冲计数器或2路DI高速计数器,Modbus RTU模块 YL1502022-11-03 1365

-

脉冲计数器的分类和作用2024-05-15 3276

-

plc脉冲量的应用场景有哪些2024-09-16 1936

全部0条评论

快来发表一下你的评论吧 !