采用现场可编程逻辑阵列技术实现防视频信息泄漏系统的设计

可编程逻辑

描述

1.引言:

随着信息技术的发展和微型计算机的普及应用,计算机已成为目前应用最为广泛的信息处理和信息传输的电子设备。由于计算机的特殊构造方式与工作方式,它不可避免地会向空间辐射电磁波 ,其信息电磁泄漏问题已经对信息安全和保密构成了严重威胁 。研究表明,视频电缆的辐射在整个视频通路的辐射中占主导地位 。因此,如果我们在视频信号传输到显示器之前就对其进行处理,就可以有效地减少视频信号被截获的可能性,而一般视频信息在视频电缆中是串行传输方式,如果采用并行数据传输,并行数据即使在泄露后也是极难还原的 。本文所设计的视频信息采集系统就是把视频信号在发送到视频电缆前先进行处理再传输到电缆上,采用现场可编程逻辑阵列(FPGA)为核心处理单元,系统程序在QUARTUSII环境中通过综合仿真,结果表明整个系统既满足视频系统对实时性的要求,又减少了信息泄漏的可能性,验证了方案的可行性。

2.系统描述:

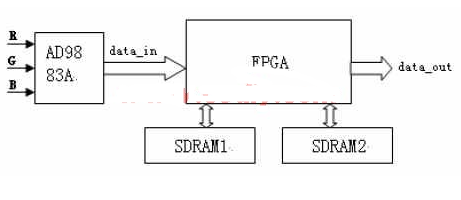

系统简化结构如图1所示,采用AD公司高性能视频专用模数转换器件(ADC) AD9883,采集三路R,G,B模拟视频信号,以高性能、高集成度、低功耗系列FPGA作为核心部件,利用FPGA的在系统可编程以及控制逻辑实现方式灵活等特点,产生系统需要的时序,完成数字视频信号的读取和两片SDRAM的交替读写,并将以像素为单位的视频信息转换为位平面格式。FPGA处理完后就将结果通过并行电缆传输至显示端适配卡,而显示端适配卡则负责将位平面信息还原为像素格式。该系统能够实现实时视频数据流的无缝缓冲,同时实现对视频信号的并行传输,降低在数据传输过程中的电磁泄露。系统主要包括A/D转换部分、帧存取部分和数据变换部分,下面分别对这三个部分进行介绍。

3.A/D转换部分

A/D转换部分选用的是AD9883,其主要特点是:1)高达300M的带宽和140MHZ的转换速率;

图1 采集系统结构图

2)三路独立的0-1.0V的输入信号范围,非常适合采样视频信号;3)提供I2C总线接口,以适应多种应用 [4]。

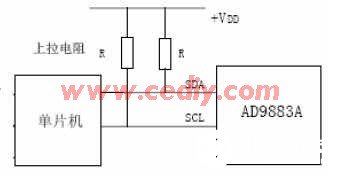

AD9883芯片在使用前需要根据实际的功能指标对内部寄存器进行初始化,初始化过程依靠AD9883的SDA和SCL两引脚进行,时序符合I2C总线时序标准。采用支持I2C总线协议的P89LPC932A1PLCC28单片机实现对AD9883的初始化,硬件连接如图2,

图2 AD9883A初始化电路图

4.帧存取部分:

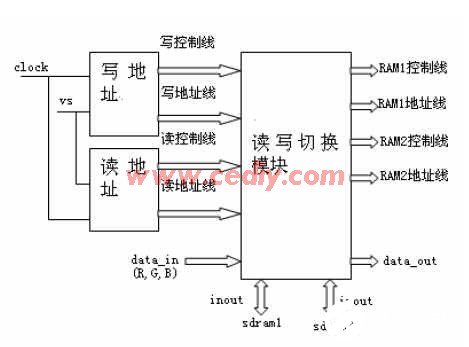

输入和输出缓冲电路一般有三种结构方式:双口RAM结构,FIFO结构,乒乓缓存结构 [5]。数字视频处理系统的突出特点是视频数据的流量非常大,因此,系统必须建立快速、有序的视频数据输入、输出机制,尽可能采用高速的FPGA,并在此基础上,采用适应于高速FPGA的乒乓缓存结构。由于SDRAM同时具有SRAM存取速度快和DRAM集成度的优点,所以在这里选用SDRAM作为帧存储单元,两片SDRAM读写地址和切换信号的产生均由高速FPGA完成,其整体结构如图3所示。

4.1SDRAM工作原理

SDRAM与SRAM不同,它只能将数据保持很短的时间。为了保持数据,SDRAM必须隔一段时间刷新一次,如果存储单元没有被刷新,数据就会丢失。SDRAM通常包括2个或4个bank,由地址线复用选通行和列地址访问SDRAM内部存储单元,这种方式有效的减少了地址线,扩大了地址访问空间。当设计FPGA实现对SDRAM的读写控制时,首先必须对SDRAN进行初始化配置,即写模式寄存器,以确定CAS潜伏期,突发传输模式等工作模式;然后,经过激活命令激活对应地址的bank,同时输入行地址。最后,通过读命令或者写命令输入列地址,将相应数据读出或者写入到对应的地址。操作完成后用相关命令中止读或写操作 [6] [7] 。

图3 帧存取单元电路图

4.2写地址发生电路:

写的过程是将三路24bit R,G,B数字信号写入SDRAM中,所选用SDRAM是32位,剩余高8位补0。写地址发生电路产生数据写入RAM时需要的行,列选通信号ras_w,cas_w,写允许信号we_w,写地址信号add_w以及块选择信号bank_w。写地址发生电路核心是两个11位计数器,当列数计到最大列数值时,通过预充电命令关闭所在行,并把行数加1,在下一个时钟周期先激活下一行,再进行写入,写地址发生仿真波形如图4所示。

图4 写地址发生仿真

4.3读地址发生电路

读的过程是将存储在SDRAM中的数据读到视频传输电缆上,读地址同样产生读RAM所需要的控制及地址信号。与写地址控制电路不同的是,读取过程有读潜伏期CL,即从CAS与读取命令发出到第一笔数据输出的这段时间,所以在一行读完的时候,先执行两个空操作命令再预充电关闭所在行。同时在读方式上采用突发连续读取模式,突发长度BL设定为8,只要在起始列地址发送列地址和读命令即可,以后的寻址与数据的读取自动进行,这样可以大大降低对控制资源的占用,读地址发生仿真波形 如图5所示。

图5 读地址发生仿真

4.4读写切换电路

读写切换电路实现两片SDRAM的交替读写,在一帧时间内一个SDRAM向显示器输出图象信号,另一个接收来自显卡端的R,G,B信号,在下一帧两个SDRAM进行读写切换,这样循环下去。读写切换信号switch由场同步信号VS经过二分频产生,周期为2倍场同步信号周期,在其为低电平时,向SDRAM1写入数据,高电平时从中读出数据。除了完成读写地址信号切换,还要实现数据输出切换,这里把SDRAM数据线与FPGA的接口定义为inout端口类型,由switch信号决定端口处于输出还是输入模式。

5.数据变换部分

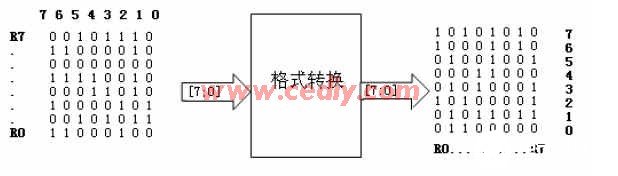

前面说过,把串行视频信号转换为并行信号可以大大降低信号在视频传输电缆上的信息泄露,但如果简单的将模拟视频信号转换为数字信号后直接进行传输,虽然数据是并行传输的,但同时传输的只是一个像素的不同位灰度信息,因此,从像素角度来考虑,仍然是串行传输的。所以在视频信号送至传输电缆之前就进行位面分层格式转换,使得并行电缆上能同时传输多个像素,实现真正意义上的并行,即基于像素的并行传输。

以红色信号为例,FPGA从SDRAM中读出8个像素的R(红色,8位)灰度数据,经过转换后成为位面分层格式,再经过8次并行连续输出,宽度为8位,这样将8个像素的R灰度数据R7-R0同时连续输出,R灰度数据位面分层示意图如图6所示。经过接收端电路的处理,将会还原到原始的灰度数据。这样,就将传统的串行模拟传输,变为并行数字传输,增加了信息被截获后复现的难度,保证了信息的安全传输。

图6 位面分层输出示意图

6.结论

以高速FPGA作为核心处理器件,完成了防视频信息泄漏系统数据发送端的设计,选用SDRAM作为缓冲存储器,在数据发送端先对视频信号进行位面分层格式转换,实现真正意义上的象素并行传输,减少了信息泄漏的危险,经过软件仿真和硬件实现,论证了此方案的可行性。

本文作者创新点:

1.器件选择:选用视频专用ADC,高速可编程逻辑器件FPGA,选用SDRAM作为缓冲存储单元,速度快,保证了视频信息传输的实时性要求;

2.结构设计:由于SDRAM的行列地址复用等特点,采用FPGA作为核心处理器,在一片FPGA内设计了SDRAM的读/写,切换控制器;

3.防信息泄漏算法:很多参考文献中指出,并行传输的信号很难被还原;因此在视频信息发送到传输电缆之前就把串行传输的信号转换为并行,这里的并行不是简单的将模拟视频信号转换为数字信号后直接进行传输,虽然数据是并行传输的,但同时传输的只是一个像素的不同位灰度信息,因此,从像素角度来考虑,仍然是串行传输的。所以在视频信号送至传输电缆之前就进行位面分层格式转换,使得并行电缆上能同时传输多个像素,实现真正意义上的并行。

责任编辑:gt

-

可编程逻辑阵列PLA内部逻辑结构示意2024-02-02 5260

-

现场可编程门阵列有哪些应用?2019-08-06 4096

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 1172

-

XC5VLX85-1FF676C现场可编程门阵列2021-04-26 1061

-

如何利用现场可编程逻辑门阵列FPGA实现实现DDS技术?2021-04-30 1337

-

FPGA-现场可编程门阵列2021-07-30 1248

-

可编程逻辑阵列fpga和cpld相关资料2023-09-20 640

-

开关电容器现场可编程模拟阵列的频域SPICE仿真2006-05-26 2390

-

现场可编程门阵列的供电原理及应用2010-03-17 1892

-

可编程逻辑阵列(PLA)简介2012-10-12 23454

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 1047

-

可编程逻辑阵列fpga和cpld说明2021-03-30 1215

-

现场可编程门阵列简介2021-04-07 1551

-

现场可编程门阵列是什么2024-03-16 4186

-

什么是现场可编程逻辑阵列?它有哪些特点和应用?2024-05-23 2652

全部0条评论

快来发表一下你的评论吧 !