在现场可编程逻辑门阵列上实现全数字跳频同步系统的设计

可编程逻辑

描述

1. 引言介绍

跳频通信具有保密性强,抗干扰能力强,频谱利用率高等优点,获得了广泛的应用。跳频同步是其中的关键技术之一。在短时间内实现同步并保障其稳定性已成为一个研究热点。

随着软件无线电技术的发展, 传统的模拟硬件接收设备逐渐向数字IC产品过渡。FPGA(现场可编程逻辑门阵列)以其丰富的逻辑资源和可重新配置的优势, 成为人们前期研究与开发的重要手段。在FPGA上对跳频同步技术进行研究, 具有重要的应用价值。

本文详细介绍了一种全数字的跳频快速同步方法及其在FPGA上的实现方案。

2. 跳频同步方案

跳频通信中,收发双方依照约定的跳频码序列跳变载波频率。跳频同步是跳频接收机调整本地跳频序列与发端跳频序列达到同步的过程,可以分为捕获和跟踪两个阶段。捕获的任务是搜索接收到的跳频信号的跳频码序列的相位,同时调整接收机本地跳频码序列的相位,直到两者的相位差小于1/2跳时间。跟踪的任务是校准跳频码序列之间剩余的相位差。

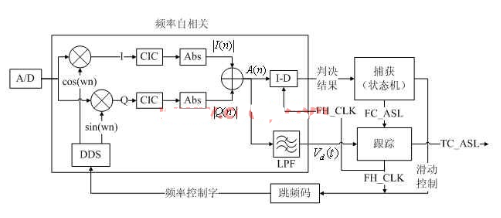

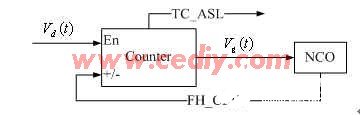

本文跳频同步方案的原理图如图1所示。包括三个部分:频率自相关,同步捕获和同步跟踪。同步捕获用状态机实现了改进的自同步捕获法——快速出局式滑动捕获法;同步跟踪采用数字NCO进行跳频时钟锁相。以上方法保障了系统在短时间内达到稳定的跳频同步。

图1 跳频同步原理图

I-D(积分门限判决器):积分器

同步捕获——快速出局

本文采用快速出局捕获法,它是一种改进的滑动相关法。滑动相关法的优点是硬件简单,抗干扰能力强,缺点是捕获时间长,为  ,其中 L是跳频周期。快速出局法对捕获算法进行了改进,大大缩短了捕获时间,达到

,其中 L是跳频周期。快速出局法对捕获算法进行了改进,大大缩短了捕获时间,达到 。快速出局法保持了滑动相关法的优点。

。快速出局法保持了滑动相关法的优点。

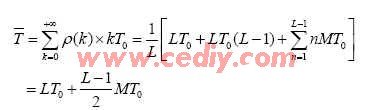

捕获状态机

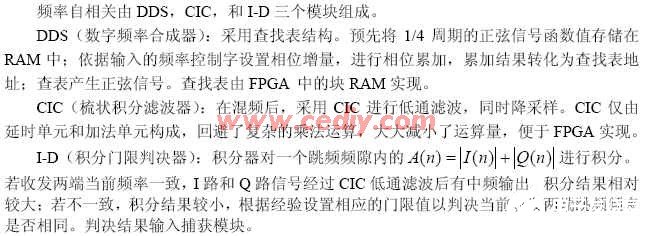

本文用状态机实现快速出局式捕获电路。捕获过程划分为三个状态:①快速出局状态,②单周期确认状态,③多周期确认状态。

快速出局状态:计数模块对 M个频隙内的判决结果累加计数,计数结果与预设门限比较,做出出局判决。若收发双方跳频序列未同步则将本地跳频序列的当前状态快速出局,跳频序列相位滑动,重新开始本地载波与接收信号的相关、累计和出局判决;否则,快速捕获成功,进入单周期确认状态。

单周期确认状态:计数模块对一个跳频周期内的判决结果累加,对累加结果进行门限判决。若捕获成功,进入多周期确认状态;否则返回快速出局状态,重新开始捕获过程。

多周期确认状态:在若干个跳频周期内对捕获进行确认,确认成功,捕获过程完成,进入跟踪过程;否则返回快速出局状态。

状态转移图如图2所示。图中FOS_flag为快速出局捕获标记,SOS_flag为单周期捕获标记,FC_ASL为捕获成功标记。进入跟踪过程后,时刻检查SOS_flag,一旦失去同步,立刻跳回状态①,重新进行捕获。

图2 捕获过程状态转移图

捕获时间分析

无干扰时,快速出局式滑动捕获法在第 个频隙捕获成功的概率为:

(1)

其中 为出局参数, 为跳频码周期

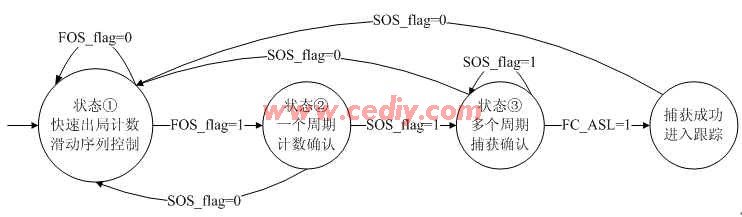

此时其捕获时间的期望为[5]:

(2)

由公式2可知,快速出局法的捕获时间为  ,远小于滑动相关法的捕获时间

,远小于滑动相关法的捕获时间 。

。

同步跟踪——数字NCO

捕获完成后,收发双方的跳频码序列间剩余的小于1/2跳时间的相位差由跟踪过程校准。

图3 负反馈跟踪环

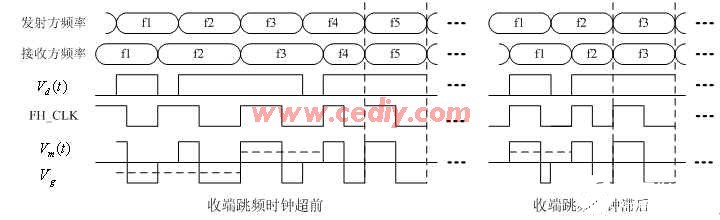

跟踪过程如图4所示。由图中可看出,经过数个周期,即可完成跟踪。

图4 跟踪过程

3. 仿真结果

用Verilog HDL实现上述跳频同步方案,综合,映射,布局布线后,调用Modelsim进行后仿真。仿真条件如表1所示。

FPGA片上时钟/AD采样时钟 40 MHz

表1 仿真条件

仿真结果如图5所示。捕获状态机起始状态为状态①,经过两次跳频码滑动后,本地跳频序列捕获到了发端序列,进入状态②;一个周期捕获确认后进入状态③;经过再次确认,fc_asl信号值由0到1,捕获完成,进入跟踪。经过5个频隙,收发端跳频时钟之间的相位差降到预设门限以下,tc_asl信号值由0到1,跟踪完成,同步结束。同步时间约0.25s,远小于短波跳频电台要求的5s接入时间。在信噪比-12dB时,本方案能够迅速达到精确同步。

图5 仿真结果

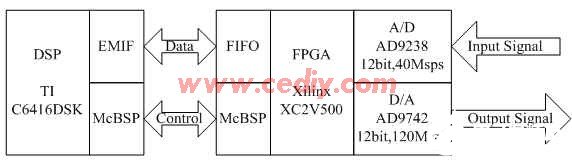

4. 硬件平台

FPGA器件具有速度快,编程灵活,可重新配置,通用性好,规模大等优点,适合进行高速数据处理。考虑到成本以及需求,本文选用容量50万门电路的Xilinx VirtexII系列FPGA XC2V500做为中频数据处理系统的核心运算单元。其内部时钟频率可达420MHz,整合了大量的分布式RAM,集成了32个18×18bit乘法器,并有多个数字时钟控制模块(DCM)以及全局时钟布线资源。硬件平台如图6所示。除了FPGA模块外,还包括AD/DA转换器,DSP以及其它的外围器件。AD转换器是采用AD9238芯片,采样精度12bit,采样速率最高可达100MHz;DA转换器是采用AD9742芯片,采样精度12bit,采样速率最高可达120MHz。

图6 硬件平台框图

前文所述跳频同步方案利用Verilog编程,Synplify综合,Xilinx ISE布局布线后,通过Modelsim后仿真验证电路的正确性,并最终在FPGA芯片上实现。芯片资源占用如表2。

表2 XC2V500资源占用情况

5. 小结

本文设计了一种高效的跳频同步方法,并介绍了该方法在FPGA平台上的实现方案。本文作者创新点是设计并实现了基于状态机的快速出局滑动捕获电路的和基于计数器的NCO跟踪电路。此方案同步性能优越,保障较强的抗干扰能力的同时大大缩短跳频同步的时间,在信噪比为-12dB的情况下仍能在短时间内达到精确同步,并且电路结构简单,硬件消耗少。这种方法在跳频通信中有广泛的应用前景,对工程实现有重大的意义,并且具有很好的通用性,实际应用中,可通过修正参数适应不同频段和跳速的需求。

责任编辑:gt

-

现场可编程门阵列简介2024-03-27 1529

-

现场可编程门阵列是什么2024-03-16 4176

-

FPGA现场可编程门阵列的综合指南2023-12-07 1692

-

什么是FPGA?FPGA现场可编程门阵列的综合指南2023-09-14 2194

-

FPGA-现场可编程门阵列2021-07-30 1248

-

如何利用现场可编程逻辑门阵列FPGA实现实现DDS技术?2021-04-30 1337

-

XA6SLX25-3CSG324Q现场可编程门阵列2021-04-26 1525

-

XC7K325T-2FFG900I现场可编程门阵列2021-04-13 1172

-

现场可编程门阵列有哪些应用?2019-08-06 4096

-

现场可编程逻辑门阵列器件 FPGA原理及应用设计2017-09-19 1045

-

现场可编程门阵列2015-03-13 2344

-

现场可编程门阵列的供电原理及应用2010-03-17 1892

-

现场可编程门阵列的结构与设计2009-07-07 1949

全部0条评论

快来发表一下你的评论吧 !