利用ADC、全差分放大器和时钟调整电路设计模拟系统

模拟技术

描述

传统上,模拟IC设计工程师都是通过提升电源电压和工作电流来提高设备的运行速度和动态范围,但在能源效率意识愈强的今天这一方法已很难达到最佳的效果。现今,设计者不仅追求更高的工作频率、可用带宽、噪声性能和动态范围,还要同时保证设备的功耗不变甚至更低。

美国国家半导体公司的PowerWise产品采用创新的架构和领先的制作工艺,不但性能强劲而且功耗极低。本文将通过采用图1中的参考设计平台来展示如何利用高能源效率的模/数转换器(ADC)、全差分放大器和时钟调整电路来开发一个完整的模拟系统。首先,我们先从PowerWise 品牌背后的技术内涵谈起。

图1. 完整的参考设计电路板,当中包含有ADC、全差分放大器和时钟调整器电路。

为特定组件度身订造的工艺技术

用来开发模/数转换器(ADC)的工艺技术并不一定适合用来开发高频的低噪声放大器。事实上,半导体公司一般都会使用几种不同的工艺技术,例如CMOS、BiCMOS和SiGe等。而使用哪一种工艺则取决于组件的要求。如果没有优秀的工艺技术相配合,再完美的电路设计也是有缺憾的。

不同于其他大多数的半导体供应商,美国国家半导体采用纯CMOS技术去设计大部分最新的ADC。今天,CMOS技术可谓无处不在,原因是CMOS的逻辑门没有任何的静态功耗,但拥有较高的驱动电流和速度。考虑到ADC内包含有大量的数字电路,因此用纯CMOS技术去实现电路设计便可实现比BiCMOS更低的功耗。数字CMOS门电路在直流模式下不会消耗电流,但双极的门电路即使在直流模式下都需消耗电流,因为电路需要偏置电流来维持性能参数。结果,芯片中的数字部份会消耗较多的电流,从而提高整体的功耗。

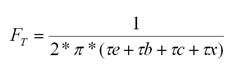

美国国家半导体特别开发出VIP 10工艺来配合放大器电路的设计。VIP 10是一种高速、介质隔离的互补双极电路工艺,它在一片键合晶圆(bonded wafer)上采用深槽技术实现完全的介质隔离以及优化的高速放大器性能。键合晶圆采用的深槽技术可尽量降低寄生电容,优化功率/带宽性能、降低失真并使裸片的体积更小。采用高性能NPN和PNP晶体管的互补双极晶体管设计可以为现今的高速放大器带来最优的性能组合,包括高带宽、低功耗、低电源电压、大输出摆幅、高输出电流和低失真。对于双极晶体管来说,最常用的AC品质因素是过渡频率(FT),在这频率下共发射极电流增益下降到单位级。在VCE=5V下,VIP 10 NPN和PNP的FT分别为9GHz和8GHz,大约比同类竞争的工艺高出50%。晶体管的高FT意味着在既定工作点下其发射极-基极扩散电容值会很低。配合VIP 10晶体管,美国国家半导体可以设计出带宽超过1GHz 或带宽在100MHz 范围以内的放大器,而且其功耗可以非常低。因为扩散和寄生电容同时被大幅削减后,内部级在很低的工作电流下也会出现低相位位移。对于某些双极工艺来说,FT可以在较低电压下大幅地下降,但若采用VIP 10工艺,那即使Vce=1V,FT都可维持在高水平:NPN可达7GHz而PNP可达5GHz。下面的公式1表示出一个双极晶体管的过渡频率是如何计算出来。

其中:

k是玻尔滋曼常数、T是绝对温度、Cte 是发射极电容、q是电子的单位电荷、IC 是集电极电流、WB是基带带宽、μB是电子移动性、rcs是集电极电阻、Ccb 是集电极电容、Xs 是集电极空间电荷区的宽度,而vx则是集电极空间电荷区的饱和速度。

创新的技术

上文中我们已探讨过IC设计者通晓了最优的电路设计方法、专利架构和尖端的工艺技术就基本掌控了到业内最先进的技术,从而能够在竞争激烈的市场中开发出与众不同的产品。要进一步巩固竞争优势,设计者还必须紧随业内发展的潮流,诸如美国国家半导体的PowerWise等创新技术。PowerWise技术可以使数字处理器(例如DSP或FPGA)中的DSP或FPGA功耗降低70%。

PowerWise采用自适应电压调整(AVS)和阈值调整技术可以在维持系统最低开销的情况下自动将数字逻辑电路中的工作电路和漏电功耗减到最低。PowerWise技术在业内是独一无二的,它是唯一一种可供所有电路开发商使用的先进系统级能源管理方案,不但内容完备而且还可提供详细的知识产权信息。通过使用简单的标准硬件接口,加上业内知名合作伙伴ARM、TSMC、UMC、Synopsys等支持,这项技术可应用到任何CMOS工艺,而且设计工具和流程都已标准化,可配合任何的操作系统或应用,实现最优的能源效率。

建立一个完整的模拟系统

设计参考可以为设计工程师提供了设计模版,其重要性不言而喻。特别是要求在不增加功耗的前提下提升系统性能时,设计参考就显得更为重要了。大多数棘手的设计问题,例如选择正确的组件、组件布置、系统布局和布线等,都可在这些设计参考中找到答案。基于服务客户创建的高性能模拟系统的知识积累,美国国家半导体建立起了一个汇聚杰作的设计参考库。以最新加入参考库的ADC14DS105KARB参考设计为例,它采用了最新的PowerWise 家族LMH6552 1.5GHz差分驱动器作为信号链的一部份。该组件与高速的ADC14DS105数据转换器和定时方案结合在一起,为测量仪表的设计者提供一个良好的参考工具。

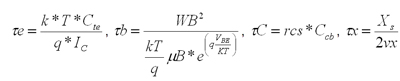

ADC14DS105KARB接收器参考设计板

ADC14DS105KARB是一个近零中频接收器参考设计板,它所使用的组件如下:两个LMH6552 1.5GHz 带宽差分电流反馈放大器;ADC14DS105 带有LVDS输出的14位、1GHz、双路、105MSPS模/数转换器;LMK02000低抖动精密时钟调整器,它带有一个可在100Hz到20MHz带宽范围内提供128fs抖动的集成锁相环路(PLL);数个高能源效率的电源管理电路。

ADC14DS105KARB (其框图见图2)是一块中频接收器子系统参考设计板,它采用一对LMH6552差分驱动器和一个双路ADC,可以立即测试适用于直流电至40MHz信号频率的正交直接转换或近零中频接收器。这个接收器架构现已被广泛应用到WiMAX 和WCDMA接收器系统。

图2. 参考设计板的框图。

由于ADC的输入带宽高达1GHz,而差分放大器增益级的带宽高达1.5GHz,因此若输入信号不超过40MHz,大信号的信噪比可达 73.3满刻度分贝值(dBFS),而无杂散信号动态范围(SFDR)则超过85dBFS。这款电路板除了采用LMH6552之外,还安装了美国国家半导体的14位、 105MSPS、低失真、低噪声、并可输出串行LVDS数据的双通道模拟/数字转换器ADC14DS105、低抖动时钟调整器LMK02000以及多颗高能效的电源管理IC。

LMH6552是一个高性能全差分放大器,它能提供驱动14位高速数据采集系统所需的超强信号保真度和宽阔的大信号带宽。通过采用获得专利的差分电流模式输入级架构,LMH6552能够在不牺牲响应平坦度、带宽、谐波失真或输出噪声性能下,在增益大于一个单位级下工作。

配合外置的增益设置电阻器和集成式的共模反馈, LMH6552可被配置成一个差分输入到差分输出,或信号单端输入到差分输出的增益级。LMH6552的输入端可作交流耦合或直流耦合,因此可以应用到诸如通信系统及高速示波器的前端电路等非常广泛的领域。

LMH6552的电流反馈拓扑使器件即使在高增益下,只需选择合适的反馈电阻(RF1, RF2),便可提供有超强增益平坦度和噪声性能的增益和带宽独立性。在大多数的应用中,RF1都被设置成等于RF2,因此增益是由RF/RG的比例来决定。

LMH6512的数据表根据各种各样的增益给出最优的反馈电阻器数值。无论是过大或过小的RF都会对稳定性构成影响。在许可的情况下,反馈电阻器还可以调整频率响应。

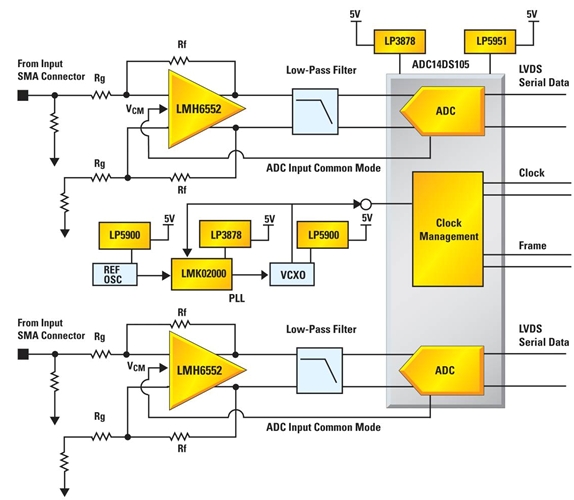

电流反馈放大器的另一优点是需要内部增益级相对较低。通常一个电流反馈放大器主要包含有一个输入缓冲器、一个增益级和一个输出缓冲器。拥有较少的增益级意味着经过开环电路的延迟会较少,从而在相同的功耗下能获得较大的带宽。

图3. 基本的电流反馈(CFB)拓扑。

图3中的基本电流反馈(CFB)拓扑是一个单级放大器。电路中的唯一高阻抗节点是在输出缓冲器的输入。VFB放大器通常需要两个或以上的增益级才能获得足够的开环增益,这些附加的增益级不单会增加延迟,而且还会降低带宽的稳定性。

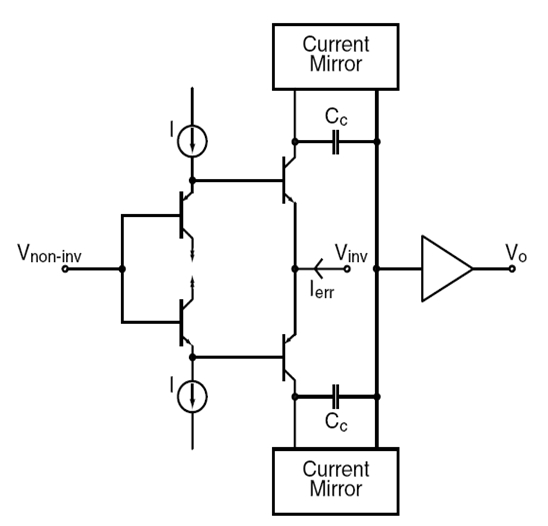

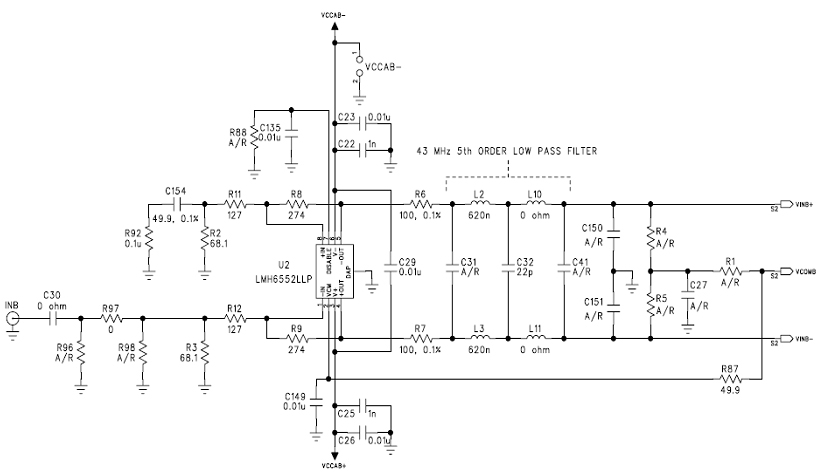

图4. LMH6552电路和5阶低通滤波器。

图4说明了放大器的参考电路板配置。当中的输入是50Ω和直流耦合。LMH6552被配置成单端到差分模式转换,而ADC14DS105的VCOM输出会用作放大器的共模输入。每一个放大器都被配置成有6分贝的增益,因此最大的输入信号电平为1Vp-p,并在放大器的输出处产生出2Vp-p。这里建议放大器最好由一个双电源轨来供电(+/- 5VDC)。在VCCAA- 和VCCAB-处设置跳线,电路板就可在单电源模式下工作,详细信息可参考LMH6552数据表中有关LMH6552单电源工作的部分。要获得最佳的失真性能(最佳SFDR),建议采用一个低噪声信号发生器来驱动评估板的信号输入,而信号发生器的输出应该经过带通滤波以抑制由信号发生器引入的谐波失真,以及容许进行精确的噪声和失真性能测量。然而,跟随在LMH6552之后的43MHz的5阶低通滤波器可过滤信号发生器的宽带噪声,从而进一步改善ADC的噪声性能。滤波器输出会被模/数转换器采样。

ADC14DS105是世上第一款带有串行化LVDS输出的14位高速、1GHz FPBW的双路模/数转换器,它采用串行化LVDS输出大幅地减少了需要跨过电路板或在电路板之间的导线数量,因此大大地简化电路板的布局。

用来替模拟输入采样的ADC时钟信号是由一个经LMK02000精密时钟调整器控制的VCOX所产生。该LMK02000为用户提供一个设有时钟分配区的超低噪声锁相环路(PLL),它可提供5个LVPECL输出和3个LVDS输出(全为差分)。

每一条在LMK02000上的时钟输出通道均包含有一个分频器模块和延迟调整时钟。LMK02000一般都会跟一个低抖动的VCOX连接在一起。在这种情况下,一个Crystek 型号的CVHD-950X-100.0可提供一个单端CMOS时钟信号来驱动ADC的时钟输入。LMK02000 的锁相环路可把这个VCOX锁定到一个25MHz的参考振荡器(Connor-Winfield 型号CWX823),而LMK02000的锁相环路计数器、相位检测器和电荷泵是采用PIC微控制器电路板来编程的,详情请参看用户指南。

LMK02000的RMS信号抖动仅为128fs(输入的时钟范围由100Hz到20MHz)。图5表示出时钟的相位噪声性能,该性能值是在LMK02000的CLKout4情况下测量出的。从VCOX产生出来的单端时钟信号会供给ADC14DS105的CLK输入。

图5. LMK02000的相位噪声性能。

LMK02000精密时钟调整器将多种功能结合在一起,包括抖动清除/重新调整、倍频和参考时钟分配。该器件集成了一个高性能的整数-N锁相环路(PLL)、一个局部集成,环路滤波器、三个LVDS输出和5个LVPECL时钟输出分配模块。

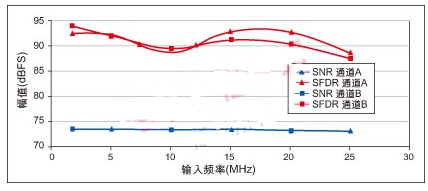

图6. 典型SFDR和SNR性能与输入频率的关系。

图6所示为差分放大器、带通滤波器和ADC的结合通道响应。请注意图中最佳的动态性能和通道间的匹配性。

责任编辑:gt

-

全差分放大器和单端转差分放大器的主要区别是什么?2023-11-14 904

-

全差分放大器四个增益的关系是什么?2023-09-18 3482

-

差分放大器的特点 差分放大器的优缺点 差分放大器的作用2023-09-04 14295

-

全差分放大器的评估2023-02-22 3299

-

2.5.1 全差分放大器及失真#放大器EE_Voky 2022-08-16

-

运放差分放大器电路分享2022-01-25 2556

-

如何使用有源匹配电路改善宽带全差分放大器的噪声性能?2021-04-13 2115

-

如何利用电阻网络调整差分放大器的固定增益?2021-04-12 1582

-

模拟集成电路设计-差分放大器版图2021-03-22 1864

-

AD8476:低功耗、单位增益、全差分放大器和ADC驱动器2021-03-19 1352

-

全差分放大器OPA1632资料分享2020-09-21 3566

-

使用全差分放大器构建仪表放大器2020-07-20 3469

-

基于毫瓦级功率的千兆赫兹信号驱动模拟系统2019-07-05 1799

-

差分放大器驱动高速ADC的电路2009-03-22 2856

全部0条评论

快来发表一下你的评论吧 !