中值滤波的原理和快速算法及利用FPGA技术实现

可编程逻辑

描述

引言

现代图像处理系统对实时性的要求愈来愈高,但图像的前端采集往往会受器件或环境影响而使获得的图像含有噪声,因而需要在对图像处理前进行去噪声处理。若使用通用的软件方法,由于处理过程需要进行大量的简单计算,因此会消耗不少时间而影响系统的实时性。随着现代电子技术的发展,用FPGA来完成中值滤波这类运算简单但数据量巨大的处理,无疑是一种理想的选择。

1、中值滤波的原理和快速算法

1.1 中值滤波原理

中值滤波是一种非线性空域滤波方法。它是可以有效抑制图像噪声,提高图像信噪比的非线性滤波技术。中值滤波首先对邻域点的灰度进行排序,然后选择中间值作为输出灰度值。与均值滤波器和其他线性滤波器相比,中值滤波可以很好的滤除脉冲噪声(Impulsive Noise)和椒盐噪声(Salt and Pepper Noise)。同时能够很好的保护图像边缘轮廓的细节。

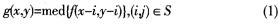

中值滤波的公式如下:

其中,g(x,y),f(x,y)为像素灰度值,S为模板窗口。

中值滤波的过程一般为:

(1)选择一个(2n+1) (2n+1)的窗口(一般是3×3或者5×5),使窗口沿图像数据的行方向和列方向从左至右、从上至下沿每个像素滑动。

(2)每次滑动后,对窗口内的像素灰度进行排序,并用中间值代替窗口中心位置的像素灰度值。

1.2 快速中值滤波算法

中值滤波算法的核心是快速求出中间灰度值。传统的排序法如冒泡法,运算量巨大。而用硬件实现不仅要消耗大量的资源,而且运算速度很慢,难以满足图像系统处理的实时性要求。本文针对大小为3×3的窗口采用了一种快速排序算法,可以在很大程度上减少运算量,且易于用较少的硬件资源实现。

图1所示是一个3×3窗口内的像素排列方式,该窗口将窗口内的各个像素点从左至右,从上至下依次定义为D11、D12、D13、D21、D22、D23、D31、D32、D33。

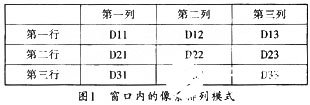

处理时,先分别对每一行的数据进行排序,以得到每一行的最大值、中间值和最小值。其中第一行得到的最大值为:Max1=max {D11,D12,D13};

中间值为:Med1=med{D11,D12,D13};

最小值为:Min1=min {D11,D12,D13};

同样,也可得到第二行的三个值Max2,Med2,Min2和第三行的三个值Max3,Med3,Min3。

由于在上述这九个数中,三个最大值中的最大值一定是九个像素值的最大值。同理,三个最小值中的最小值一定是九个像素值中的最小值。三个中值中的最大值至少大于五个像素值;即本行的最小值和其他两行中的中值及最小值。而三个中值中的最小值至少小于五个像素值;即本行的最大值和其他两行的中值和最小值。所以,比较三个最大值中的最小值Min_of_max、三个中值中的中间值Med_of_med以及三个最小值中的最大值Max_of_min,所得到的中间值就是最终的滤波结果Meddata。其具体过程如下;

虽然,与传统的排序方法相比,这种方法的比较次数大大减少。因为求出中值只用了19次比较运算,因而十分方便在FPGA上进行并行处理。

2、图像预处理系统和中值滤波器的设计

2.1 图像预处理系统设计

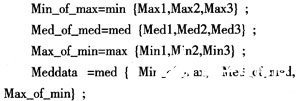

对图像的预处理,一般应在前端采集之后立即进行。图2给出了一个图像预处理系统的系统设计框图。

图2中,图像数据经前端设备采集并经过A/D转化后,可存人双口RAM中的一端。然后在选择控制模块的控制下将双口RAM中的帧数据提供给中值滤波模块,同时在双口RAM的另一端存人另一帧图像数据。接着将中值滤波处理后的图像数据存入SDRAM中,以供后续的进一步处理。双口RAM的容量只要可以存储两帧图像数据即可。

2.2 3×3窗口模块

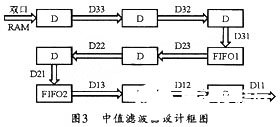

中值滤波作为图像预处理的一部分,其实时性是一个关键的要求。它要求滤波器能快速、连续的处理图像数据。中值滤波的第一个问题是要准确获得3×3窗口中的图像灰度数据。图3给出了该滤波器的设计框图。

图3中的滤波器用到了两个FIFO。这种设计可采用QuartusII中的Megacore实现。设计长度为一行数据(即256)。系统开始工作后,先对FIFO2写第一行图像数据,写满后再对FIFO1写第二行图像数据,直到FIFO1也写满。在此期间,FIFO1和FIFO2只写不读。当完成两行数据的写人后,将数据输入端和FIFO1、FIFO2如图2所示进行连接,此时的FIFO1和FIFO2只读不写,待三个时钟周期后,将FIFO1和FIFO2设为既读又写。这样,在寄存器输出端和两个FIFO的输出端即可获得第一个3×3模板中的图像灰度数据。此后,随着图像数据的输人,模板也沿着图像从左至右、从上至下移动。

2.3 模板中的数据排序

数据排序可分为三步。第一步是对每行的数据进行排序。第二步是对第一步所得到的大值组、中值组、小值组进行排序。第三步是对第二步所得到的大值组中的最小值、中值组中的中值、小值组中的最大值进行排序,最后得到中值。

具体用FPGA实现时,为了满足实时性要求,可采用流水线技术和并行处理方式。每一次数据排序的一个比较运算完成后,就把数据赋给下一级寄存器,并在下一个时钟周期做进一步处理。而该级寄存器则同时接收上一级寄存器传来的数据并进行相应的处理。本设计中共用了8级流水线,同时并行处理三行图像数据的排序。这样,在获得第一个窗口数据后再经过8个时钟周期后,就可随着模板的移动连续地获得中值了。

另外,要注意的一点是中值滤波算法不能对图像边缘进行处理。而普遍的方法是把边缘处的灰度设为0,具体电路设计时应加一个计数模块,以便确定此时的像素点是在图像边缘,这样就不用计算面将其直接设为0即可。这一点是很容易实现的。

3、硬件实现及结果

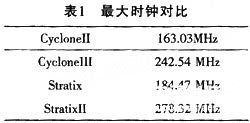

整个设计可采用VerilogHDL语言编写,并在QuartusII 6.0上实现,也可用Modelsim进行前后仿真。以便得到较高的处理速度。该设计可分别在ALTERA公司的CycloneII,CycloneIII,Stratix,StratixII器件上实现。表1列出了在各个器件族上进行全编译后的最大时钟频率。

由表1可见,中值滤波即使在低级别CycloneII器件上,也可以达到163.03MHz的时钟速率。

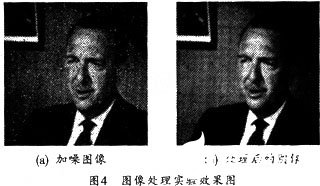

而在最新的CycloneIII器件上则可达到242.54MHz,在更高级的StratixII器件上则高达278.32MHz。这样以最高时钟处理一幅256×256×8bit的灰度图像只需236μs。图4所示是使用该设计在CycloneII平台上对一幅256×256×8bit的灰度图像进行处理的实验结果。

其中,图4 (a)在原图上加了椒盐噪声(saltand pepper noise)。图4(b)是经中值滤波处理后的图像。可以看出,中值滤波器对椒盐噪声有良好的滤除作用。

4、 结束语

本设计在ALTERA公司的CycloneII系列FPGA上成功实现了一种快速中值滤波算法,并获得了良好的处理结果。本方法为图像处理系统的前端预处理的滤波提供了一种解决方案,并可以应用于普遍的图像处理系统前端。事实上,本设计只需做微小的修改即可做为5×5、7×7以及更大的滤波模板。

-

人脸检测算法及新的快速算法2013-09-26 3938

-

基于FPGA的中值滤波算法实现2017-09-01 5875

-

请问如何实现改进的中值滤波器的设计?2021-04-14 2076

-

如何利用FPGA乘累加的快速算法设计出高速的FIR数字滤波器?2021-05-07 1897

-

快速中值滤波的FPGA实现2011-03-25 1858

-

测井图像的多级中值滤波算法及其FPGA实现2015-12-31 659

-

基于FPGA的ECC快速算法研究及设计2017-01-07 755

-

基于FPGA的实时图像中值滤波算法及实现_蒋涛2017-03-19 1541

-

基于查表的无乘法DCT快速算法 Jpeg压缩算法中的DCT快速算法2017-09-18 1144

-

DM6446的车牌定位快速算法实现与优化2017-10-26 1402

-

基于图像增强的去雾快速算法的FPGA实现2017-11-17 5987

-

图像加窗中值滤波算法的研究分析2018-11-30 1195

-

如何使用FPGA实现图像的中值滤波算法2021-04-01 1362

-

面向硬件实现的HEVC帧内编码快速算法2021-06-21 1087

-

2D中值滤波算法的设计实现2023-07-12 1772

全部0条评论

快来发表一下你的评论吧 !