基可编程逻辑器件和数字锁相实现快速位同步系统的设计

可编程逻辑

描述

1、引言

在时分复接通信系统中,位同步是收、发两端的时钟频率必须同频、同相,这样在接收端才能正确地判决发送端送来的每一个码元。为了达到收、发端频率同频、同相,在设计传输码型时,一般要考虑传输的码型中应含有发送端的时钟频率成分。这样,接收端从接收到的信码中提取出发端时钟频率来控制收端时钟,即可实现位同步。相位误差及同步建立时间是位同步系统两大主要性能指标,本文在保证位同步系统取得较小相位误差的前提下,提出一种基于FPGA技术的快速位同步系统设计方案。

2、 数字锁相原理

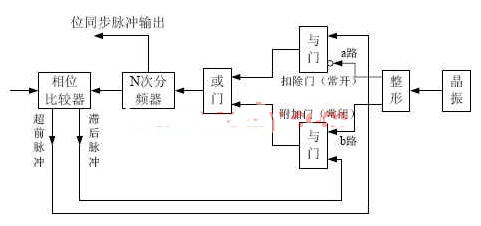

数字锁相是实现位同步的一种常用的方法,其原理框图如图1所示,由晶振、分频器、相位比较器和控制器所组成。其中控制器包括图中的扣除门、附加门和“或门”。晶振产生的信号经整形电路变成周期性的脉冲,然后经控制器再送入分频器,输出位同步脉冲。若接收码元的速率为 (Baud),则要求位同步脉冲的频率为 (Hz),晶振的振荡频率要设计为 (Hz),由晶振输出经整形得到重复频率为 (Hz)的窄脉冲,经扣除门、或门并 次分频后得到重复频率为 (Hz)位同步信号。

图1 数字锁相原理框图

3、位同步系统FPGA实现

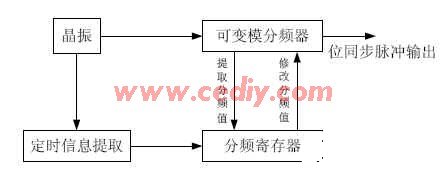

基于FPGA的位同步系统框图如图2所示,分频寄存器实现相位比较器、控制器功能,根据相位比较器输出结果控制分频值大小,通过不断修改可变模分频器的分频值,在功能上实现脉冲的扣除或添加。

图2 基于FPGA的位同步系统框图

3.1 定时信息提取

对通信理论中的基带信号频谱分析可知,对于基带信号,它若是随机的二进制非归零序列,则该信号本身不含位同步的定时信息。定时信息提取器由异或门和D触发器构成,用来提取输入信码中的边沿信息,相当于对非归零码进行微分,实现由非归零码向归零码的转换。提取到的边沿信息将作为分频寄存器的时钟信号,分频寄存器在边沿信息的控制下调整寄存器中的分频值。

3.2 晶振与可变模分频器

if (clk_240khz‘event and clk_240khz =’1‘) then

if (q=0) then q《=module_set; --修改分频值

else q《=q-’1‘;

end if;

if (q 《 49) then bs_out《=’1‘; --位同步脉冲输出

else bs_out 《=’0‘;

end if;

count100 《=q; --与分频值寄存器交换数据

end if;

3.3 分频寄存器

当信码定时信息到来时,如果从可变模分频器提取到的分频值为 ,则判为同步状态,大于 时判为滞后状态,滞后状态应减小分频值,小于 时判为超前状态,超前状态应加大分频值。模块主要VHDL代码如下:

if (bs_time’event and bs_time =‘1’) then --位定时控制

if (count100《49) then --判断是否超前

module_set《=“1100100”; --加大分频值

elsif (count100》49) then --判断是否滞后

module_set《=“1100010”; --减小分频值

else module_set 《=“1100011”; --同步状态

end if;

end if;

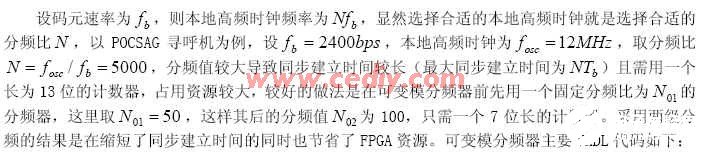

3.4 FPGA顶层设计

根据以上各部分功能模块,将它们生成图形符号后,建立顶层设计文件,图3给出了位同步系统的FPGA电路图。

图3 位同步系统的FPGA电路图

电路图模块说明: FRE_DIVIDER_50——50分频器;TIME_CAPTURE——定时信息提取器;MODULE_REGISTER——分频值寄存器;MODULE_DIVIDER——可变模分频器。

3.5 仿真分析

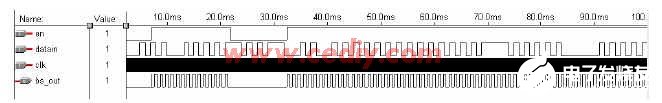

在MAX PLUS环境下,仿真参数为:本地高频时钟周期设为200ns,信码码元宽度为1ms,信码起始位置任意,仿真时间100ms,电路的仿真波形结果如图4所示:

图4 仿真波形结果

端口说明:en——位同步使能控制;data_in——输入信码;clk——本地高频时钟;bs_out——同步检测器输出。

图4的仿真结果直观地反映了数字锁相的工作过程,该电路在位同步使能控制“en”的控制下进行同步调整,分频器不断地修改分频值,使输出的位同步脉冲相位向着信码相位方向靠近,在78.96ms时刻位同步电路初次达到同步状态,产生了正确的与信码同频同相的位同步脉冲,完全达到了设计要求。

4、性能优化

由仿真分析我们不难看出本位同步电路的同步建立时间较长,问题在于分频寄存器在判断出电路状态后,加大或减小分频值的步进值太小,只能是一个本地时钟。在初始建立同步时,如果初始相位误差较大(最大时为半个码元宽度 ),这样造成同步建立时间较长,影响电路性能和信码正确判决与接收。

为了减小初始位同步建立时间,兼顾相位误差的要求,可对分频寄存器加以改进,灵活调整滞后或超前状态时分频值的步进值。具体做法是当相位相差较大时(这里设置为5个本地高频时钟宽度以上),步进值加大为5个高频时钟,而当相位误差较小时,则采用常规的一个单位的步进调整。以下是改进后的分频寄存器的VHDL代码:

if (bs_time‘event and bs_time =’1‘) then

if (count100《49) then

if(count100《44) then module_set《=“1101001”; --加大调整步进值

else module_set《=“1100100”;

end if;

elsif (count100》49) then

if (count100》54) then module_set《=“1011101”; --加大调整步进值

else module_set《=“1100010”;

end if;

else module_set 《=“1100011”;

end if;

end if;

仍采用3.5给出的仿真参数,以下分析其仿真结果。

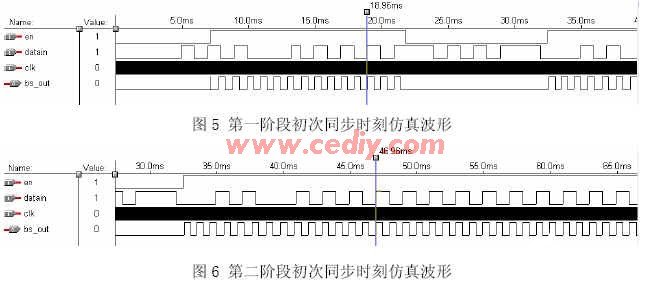

图5给出了第一阶段初次同步时刻,这里所说的第一阶段是指同步使能信号en的第一个有效时间段,相比未改进方案其同步建立时间明显缩短,在18.96ms时刻达到同步状态,而未改进方案的第一阶段没有出现同步时刻;图6给出了第二阶段(即en的第二个有效时间段)时初次同步时刻,初次同步出现在46.96ms时刻,相对于未改进方案给出的初次同步时刻78.96ms快了整整32.00ms,显然,经过改进后的位同步电路大大减小了同步建立时间,能够较快地建立起同步。

5、 结论

仿真结果表明基于FPGA的位同步系统性能优异,工作稳定、可靠。系统分频电路采用两级分频的方法在缩短了同步建立时间的同时也节省了FPGA的耗用资源,灵活调整滞后或超前状态时分频值的步进值极大地降低了系统的同步建立时间。

6、 本文作者创新点

提出了一种基于FPGA的快速位同步系统的设计方案,用两级分频的方法缩短了同步建立时间及节省了FPGA的耗用资源。

责任编辑:gt

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4571

-

可编程逻辑器件测试2023-06-06 1302

-

可编程逻辑器件(书皮)2022-07-10 786

-

PLD可编程逻辑器件2021-07-22 2321

-

怎么采用可编程逻辑器件设计数字系统?2021-04-29 1384

-

可编程逻辑器件的分类有哪些2020-06-10 31169

-

数字电子技术--可编程逻辑器件2016-12-12 1204

-

可编程逻辑器件2014-04-15 3676

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1163

-

可编程逻辑器件基础及应用实验指导书2010-03-24 785

-

基于可编程逻辑器件的数字电路设计2009-11-16 1939

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

基于单片机的复杂可编程逻辑器件快速配置方法2009-03-28 1157

-

可编程逻辑器件设计2006-03-25 1179

全部0条评论

快来发表一下你的评论吧 !