基于FPGA的超宽带系统的解决方案

可编程逻辑

描述

1、 引言

近几年,超宽带(UWB)无线通信系统在短距通信领域中越来越受到人们的重视。它具有许多独特的优点,如通信容量大、低截获/检测概率、频带宽、强抗多径干扰能力和高分辨率、低设备成本等特点。这些优势使UWB通信成为了当今学术界和商业领域研究热点之一。MBOK相对于传统的DSSS扩频调制方式,改逐比特扩频为逐码元扩频,通过对信息数据的合理编码既提高了码速又节省了频带,因此得到了广泛研究和应用,使其成为室内无线扩频通信的主要研究热点。

本文介绍了基于MBOK-TH-UWB通信系统信号产生的建模与设计以及信号的接收处理与设计,利用目前FPGA设计灵活,集成度高,处理速度快,并能充分满足高速数字电路和数字信号处理等时钟管理信号完整性,高速带宽接口标准等要求的一系列优点,通过VHDL建模与设计,给出了一个基于Altera公司的FPGA的超宽带系统的解决方案。

2 、基于MBOK-TH-UWB实验系统

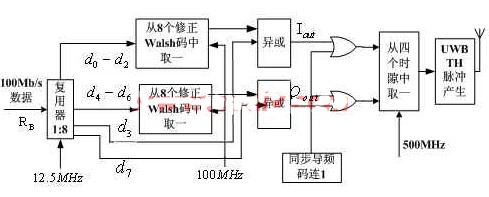

基于MBOK-TH-UWB的实验通信系统由UWB发射机(图1)UWB接收机(图3)组成

2.1系统发射部分

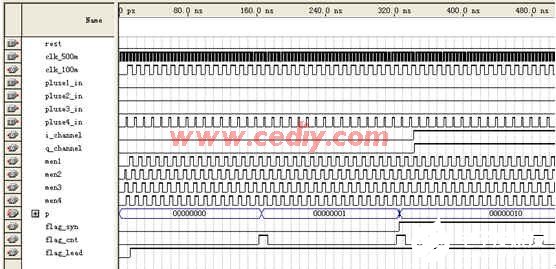

系统的发射部分主要包括了MBOK调制和TH-UWB脉冲信号的产生,如图1所示:广义信源输出连续的串行0、1 码经1:8复用器串并转换后d0-d2,d4-d6分别映射8个正交修正walsh码(表一所示) d3,d7 分别与8个正交修正walsh码异或后输出I、Q两路信号,经过从四个时隙中取一模块产生宽度为4ns的低电平,作为UWB信号发生器的触发控制脉冲信号,整个编码模块采用Altera公司StratixⅡ系列EP2S15F484C3来实现,在QUARTUS II系统开发平台下,对经过MBOK-TH编码电路数字基带部分进行了模块化设计,并进行软件仿真,仿真结果如图2所示

图1 系统发射部分框图

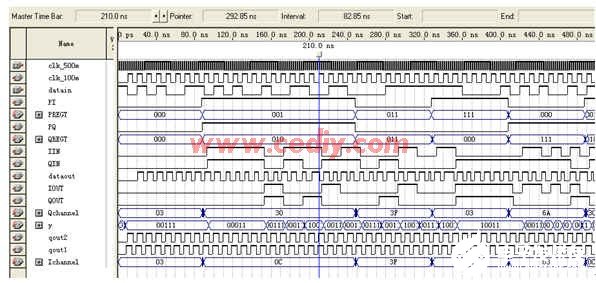

图2 MBOK-TH编码的仿真图形

图2 中datain 代表框图1中 Rb数据输入,IIN和QIN对应框图1中Iout和Qout的输出,最后dataout输出用来驱动UWB脉冲信号的产生。

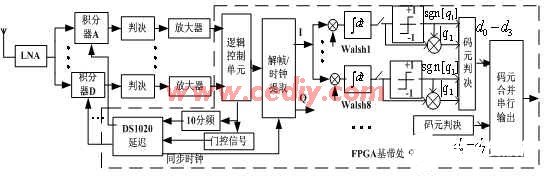

2.2系统接收部分

接收部分主要包括了积分检测和同步捕获模块和MBOK-TH解扩和码元恢复部分,其中同步捕获是整个系统实现的关键,传统的方法是通过检测接收信号与本地模板信号的相关峰值来捕获同步[4],但在高速、密集多径的室内通信环境中,这种捕获方法并不是最优的,它将导致较长的捕获时间,并且实现起来也较难。

具体原理框图如图3前半部分所示,天线接收到的微弱信号经过LNA放大后馈入四路工作于不同时隙的可控积分器,积分结果通过高速电平比较器送入高速FPGA 进行基带信号处理,DS1020模块是由Dallas公司的延迟器件为核心的独立于FPGA的外围电路,每一延迟步进按照型号分为15、25、50、100、200ps,各型号固定延迟都为10ns,刚好是一个码元周期,并由FPGA通过对其写入的控制字来调整门控信号和1G时钟的延迟时间。

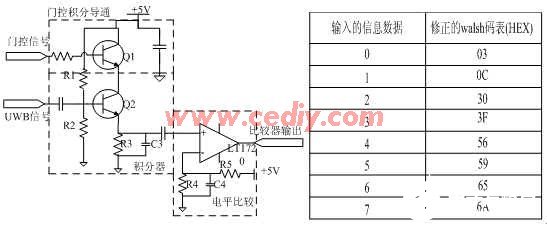

图3 系统接收部分

UWB接收机通过射频积分检测电路实现对接收信号及其多径分量的捕获,这里利用电容的充放电特性实现线性积分,设计了如图4所示:门控积分比较电路分为三个主要部分,以Q1为主要部件的门控积分导通,以Q2为核心的积分器和主要由LT1720构成的单电平比较电路,当门控信号输入为高电平(LVTTL电平)时,Q1导通UWB微弱信号经LNA放大后与Q2的基级偏压叠加馈入Q2,Q2对输入信号的正半周进行线性放大,并由接在Q2射级端的R3,C3组成的RC积分器取出输入信号的包络,并送入以LT1720位核心的单电平比较器进行判决输出;反之,Q2截至,集电极电流为零,电容C3通过R3放电清零,比较器输出为低。

图4 门控积分比较电路 表一 修正walsh码表

如图4所示:门控信号控制积分器使其工作时间为4ns,清零时间为6ns,每路错开2ns,这样4路积分器刚好涵盖整个重复周期,任意时刻总有对应的积分器处于工作。系统同步捕获采用导频码的方法,在发送数据信息之前,插入的导频码发送连1的触发信号,每一重复的时钟周期的前6ns为高电平,后4ns为低电平,捕获期间:门控脉冲产生模块在逻辑控制单元的驱动下输出如图8所示的门控信号,判决模块把积分器的输出值与判决比较器的参考电平值进行实时比较输出。同时,逻辑控制单元在单位时间内对4路积分判决器的输出的脉冲个数进行统计计数,计数结束后判决最后一路捕获的脉冲个数是否达到单位时间内应捕获的脉冲个数,如果计数不足就调整 DS1020模块延迟门控信号的时间,直至积分D输出的脉冲个数达到单位时间应捕获的,同步后把1G时钟经DS1020模块再作占空比为50%的10分频输出作为位同步时钟,如果适当地选择比较器的参考值,那么在任何一个码元宽度(10ns)内,仅有一个支路输出窄脉冲。这样就可以正确解调出接收到的码元数据。

对基带处理电路同步控制进行仿真,得到的仿真结果如图5所示。

图5:收端基带部分同步控制仿真波形

经过解帧和时钟提取模块后,数据就进入解扩和码元恢复模块,解扩过程则是以同样的修正的walsh码集作相关运算,对相关值进行判决,恢复出原始信息,MBOK-TH解扩框图如图3所示,I路从相关值中提取出符号信息sgn(Qi) 和绝对值信Qi的绝对值,对Qi的绝对值 进行择大判决,通过查表获得与此Walsh码相对应的原始信息(3bit信息),最后与代数符号成为4比特数据,从而完成一条支路的信息的扩频,对于Q支路采取同样的操作。

和绝对值信Qi的绝对值,对Qi的绝对值 进行择大判决,通过查表获得与此Walsh码相对应的原始信息(3bit信息),最后与代数符号成为4比特数据,从而完成一条支路的信息的扩频,对于Q支路采取同样的操作。

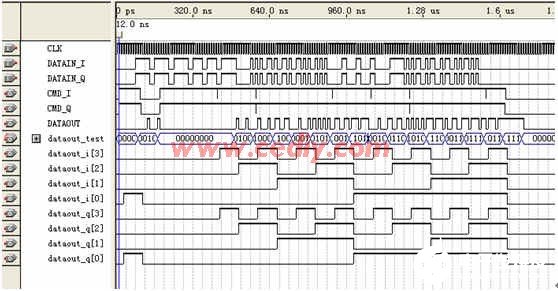

在QUARTUS II对这一部分进行设计仿真,仿真波形如下图所示

图6 MBOK解扩部分的仿真图

仿真管脚说明:DATAIN_I,DATAIN_Q分别代表I、Q两路信号的输入, CMD_I,CMD_Q两个中间变量代表两路检测出来的数据是否跟与修正的walsh码集相对应,为下一步数据处理作准备,dataout是解调出来的数据,dataout_test是为了便于检察两路解调出来的数据是不是满足要求,仿真结果表明是正确的。

3、分析总结

本文介绍了基于MBOK-TH-UWB通信系统信号产生的建模与设计以及信号的接收处理与设计,利用FPGA在高速数据通信系统中所具有的一系列优点,通过以QUARTUS II开发系统为平台,对系统的各个部分进行了模块化设计,并进行了软件仿真,给出了一个基于Altera公司高速高性能的FPGA的超宽带系统的解决方案,这种方法把同步捕获放在主要数字基带处理部分,与传统同步捕获的方法相比较它降低前端接收电路的设计的复杂度和调试的难度。分析结果这种方法适用于在室内无线短距离UWB通信系统中的同步捕获。

本文作者创新点: 利用文中UWB信号接收机的检测信号的方式,在硬件上把高速FPGA和延迟器件DS1020相结合,设计了适合UWB通信系统同步捕获的方案。

责任编辑:gt

-

华为AI解决方案加速超宽带产业创新2024-11-01 1562

-

超宽带技术UWB的应用是什么2024-03-15 2263

-

超宽带技术有哪些特点?2023-05-08 3616

-

UBW超宽带天线的设计2022-11-08 6762

-

瑞萨电子与3db Access合作推出安全超宽带的解决方案2021-02-05 2364

-

采用Acqiris信号分析仪的安捷伦超宽带数字接收器2019-10-31 1530

-

怎么设计基于枝节加载的超宽带滤波器?2019-08-21 2655

-

超宽带人员定位系统2018-11-20 3101

-

uwb超宽带定位原理全面解析2018-10-16 4479

-

UWB超宽带定位系统方案整体设计架构2018-03-13 1415

-

超宽带引信系统研究2016-12-14 709

-

xs110 uwb超宽带解决方案2011-10-26 1282

-

空时编码技术在超宽带通信系统中的应用2009-12-30 794

-

超宽带RF测量2008-11-26 4370

全部0条评论

快来发表一下你的评论吧 !