基于FPGA器件实现大容量高速存储系统的方案设计

可编程逻辑

描述

1、概述

数据存储设备是航天器的关键设备之一,为各种空间试验或探测数据的采集、存储以及在轨处理等方面提供了重要的支撑平台。随着航天电子技术的发展,人们面临的数据处理任务愈来愈繁重,对数据采集速率、数据采集系统的存储量等都提出了越来越高的技术要求。当前,以FLASH(闪速存储器)为基本存储介质的大容量固态存储器己经成为当前航天器数据存储的主流方案之一。闪速存储器( flash memory,简称闪存)是由EEPROM发展起来的一种新兴的存储器件,由于其具有非易失性、成本低、密度大、功耗小、可在线重复编程和擦除、具有抗震动和冲击、温度适应范围宽等特点,得到了非常广泛的应用。同时,由于目前的FPGA技术比较成熟、编程方便、控制灵活,而且可以通过软件实现各种接口功能,因此在高速数据采集和存储中采用FPGA作为控制部分,可以提高系统处理得速度及系统的灵活性和适应性。

本文介绍了一种以FPGA作为控制器,FLASH MEMORY作为主存储器的大容量高速存储系统方案,并对关键技术及实现途径进行了论述,在存储容量及存储速度上实现了突破。

2 、系统方案设计

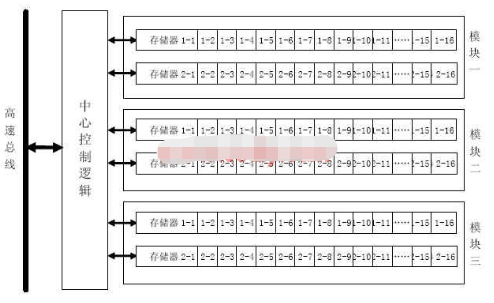

超大容量高速存储系统主要由高速总线、中心控制逻辑以及存储单元组成,其中存储单元是核心部分。该系统要实现超大容量数据的存储,达到96GB的存储容量,共使用了三个存储模块,其原理框图如图1所示。其中,每个存储模块有两个存储通道,每个通道采用16片1GB的FLASH,则可达到单通道存储容量为16GB,单个存储模块的存储容量为32GB,要想继续增大存储容量,则可通过增加存储器组的方式。其中,由于存储模块的容量要求非常大,因此选取K9K8G08U0M作为存储模块的组成单元,每片容量为1GB,读写速度高达40MB/s。

每组存储器按40MB/s的读写速度,Flash Memory每页(2KB)的编程时间最高为700us,则每页(2KB)所需的时间TW为:

TW=1/40M×2048=25ns×2048=51.2us

用分页写入的方式来读写Flash,一共需要≥700÷51.2=14片串联,就可以以40MB/s的全速写入速度操作Flash。每组存储器的读写速度为Sc(这里设存储器的读写速度为40MB/s),存储器的数据总线宽度为8位(1字节),共有n组存储器读写接口可以并行完成读写操作,则总的读写速度Sg为:

Sg = Sc × n = 40MB/s ×n

图1 高速大容量存储模块原理框图

3、 系统工作时序及逻辑控制

存储模块共有三个工作状态:读、写及擦除。系统上电后进入初始化状态,可编程逻辑器件根据输入状态判断是进入读、写、擦除中的哪一个状态。所有的逻辑控制都是由可编程逻辑控制器(FPGA)来完成。

3.1 FLASH数据循环写入技术

本设计采用16片FLASH数据循环写入技术,在每次读、写及擦除操作前都要对每一片FLASH进行无效块判断操作。若判断某一缓冲区为无效块,则跳过,继续下一块操作。每一片FLASH一页的数据缓冲区为2KB,最快写入速度为40MB/s,可计算出写入一页缓冲区数据需要时间约为50us,而对一页缓冲区的数据进行编程典型时间为200us,最长时间为700us,将16片FLASH构成存储器阵列,共32KB的数据缓冲区,其连续循环写入速度为40MB/s,完成16片FLASH的写操作需要800us,大于页编程的最长时间,使得循环16片页写入操作,保证第一页编程操作完成。依次操作,直至将所有存储器写满。在一个通道存储完毕之后,由FPGA内部的通道切换模块将通道切换至另一通道继续存储。

3.2 无效块的处理

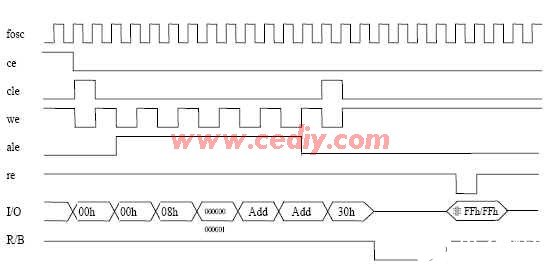

在使用大容量FLASH存储器时无效块的处理是首要考虑的问题,本设计中在每次读、写和擦除操作前都要对每一片FLASH进行无效块判断操作。过程是:上电判断无效块,无效块标志在每一块的第1页或第2页的2048列地址上,为非11111111时为无效块,先判断第一

页为无效,跳到下一块;若第一页为有效再判断第二页,若第二页为非11111111,则该块也是无效块,跳到下一块进行处理。无效块识别时序如图2所示。

图2 无效块识别时序

3.3 程序流程及地址管理

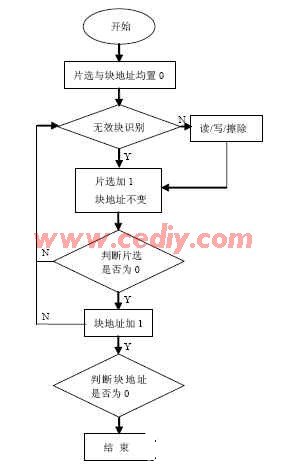

使用VHDL编写程序的流程如图3所示,由于在对FLASH的操作中有对无效块的操作,所以如果顺序进行读写擦除操作,在单路16片FLASH芯片的地址管理上将会出现混乱。所以采取的地址管理方法是:

(1) 在进行读、写、擦除之前,均先对无效块进行识别;

(2) 确定是无效块时,直接跳至下一片,块地址不变;

(3) 确定不是无效块时,直接对其进行读、写、擦除操作;

(4) 在读和擦除状态时,通过等待R/B信号进入下一块的操作,而在写状态时不等待R/B信号,在上一块编程的同时下一块也开始进入写操作,在一次片选循环完成后统计无效块的个数,等待16片全部编程完成后,再将片选加一进入下一次循环。

图3 程序流程图

3.4 多模块同时写入方式

要想达到大容量存储,必须采用多个存储模块同时存储的方式,具体是由外部的主控制模块调度采集模块向具体的存储模块传输数据,可采用轮询的方式来选择存储模块。如图4所示,通过外部的控制卡设置存储模块的地址,先存001号存储模块,然后002号,之后003号,再返回001号,每次传输X个字节后切换存储模块(X可根据需要自行设定),由主控制模块来控制传输的方向。

4、 结束语

本文提出了一种实现超大容量数据存储的方案,采用层次化设计思想,将整个系统分成几个模块,再将整个存储区间分成若干个独立的子模块分别进行存储,每个模块可以自行管理,可根据需要灵活改变存储容量;采用分页并行存储及拓宽总线的方式以提高存取速度;研究了针对FLASH芯片的存储区管理策略,包括多块FLASH芯片的地址管理以及无效块管理等。

文章创新点:

1、超大容量数据的存储:采用层次化设计思想,将整个系统分成几个模块,再将整个存储区间分成若干个独立的子模块分别进行存储,每个模块可以自行管理,可根据需要灵活改变存储容量;

2、采用分页并行存储及拓宽总线的方式以提高存储速度;

3、研究针对FLASH芯片的存储区管理策略,包括多块FLASH芯片的地址管理以及无效块管理等。

责任编辑:gt

-

常见的几种不同的高速数据采集存储系统介绍2019-07-04 3088

-

如何利用FPGA的设计微型数字存储系统?2019-08-01 950

-

FPGA如何为相机设备设计高速大容量存储2019-08-07 3101

-

分享一款不错的基于FPGA超高速雷达住处实时采集存储系统2021-04-15 2658

-

怎么实现基于FPGA的水声信号采样存储系统设计?2021-05-06 974

-

大容量固态存储设备的FPGA实现2010-12-08 692

-

基于FPGA的微型数字存储系统设计2009-11-04 1169

-

高速大容量存储系统设计2010-03-08 1419

-

高速数据采集与存储系统技术方案2011-07-07 796

-

车载CAN总线记录仪实现大容量存储系统2011-09-08 2747

-

基于SATA硬盘和FPGA的高速数据采集存储系统2011-11-15 1699

-

如何使用FPGA设计高速实时数据采集存储系统的资料概述2018-12-10 1515

-

基于FPGA的逻辑功能实现高速大容量存储系统的设计2020-07-21 1764

-

如何使用FPGA实现多通道图像采集存储系统的设计2021-01-29 1087

-

如何使用闪存实现图像存储系统的设计2021-03-23 1202

全部0条评论

快来发表一下你的评论吧 !